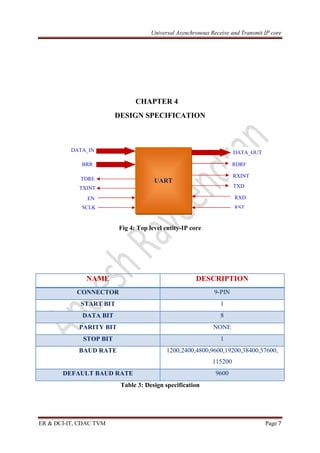

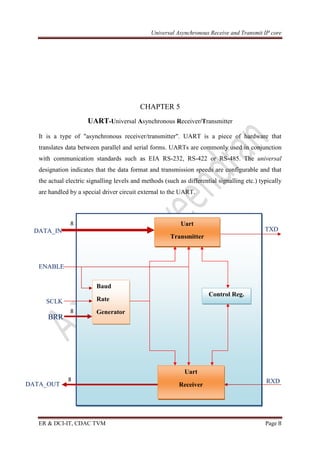

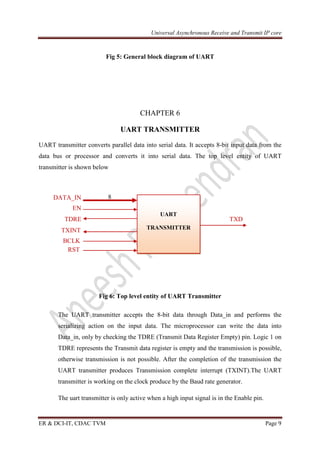

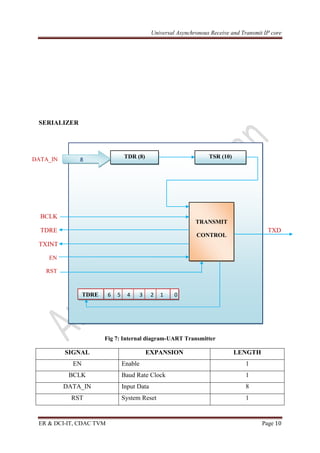

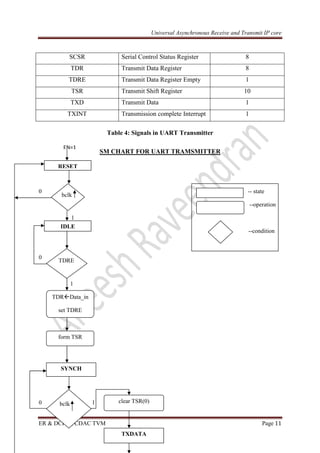

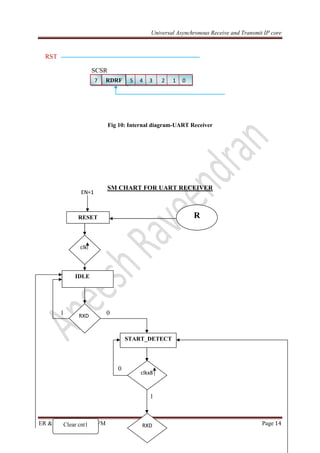

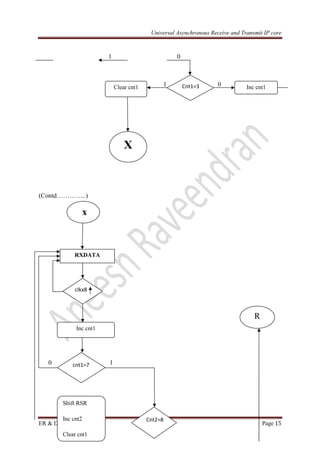

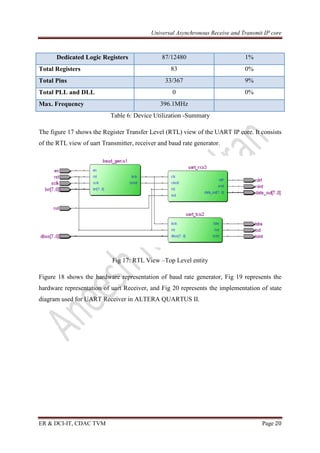

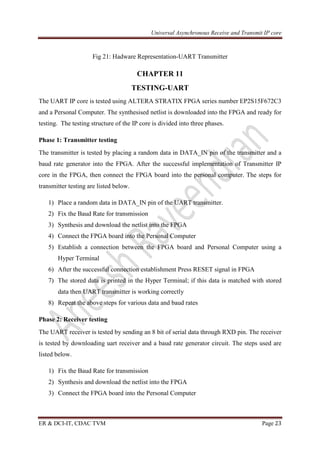

This document describes a Universal Asynchronous Receive and Transmit (UART) IP core. It discusses the RS-232 serial communication protocol that the UART uses. It then provides details on the design specification of the UART IP core, including its 9-pin connector, data formats, and configurable baud rates. The document also describes the internal design of the UART transmitter and receiver blocks, including how they convert parallel data to serial and vice versa.