Sequential circuits

•Download as PPT, PDF•

0 likes•7 views

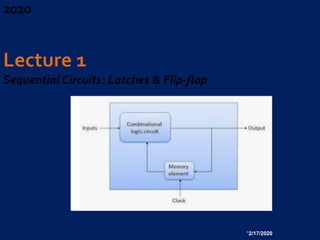

- Sequential circuits use a periodic clock signal to determine when to store values from combinational logic circuits. - The basic storage element is a flip flop, which can be constructed from latches. Common types include D, JK, and T flip flops. - Flip flops store their output on either the rising or falling edge of the clock signal. They allow data to be stored indefinitely until the next clock edge. - Multiple flip flops can be combined to store multiple bits of data, forming the basis of computer memory systems. Sequential circuits combine storage from flip flops with additional combinational logic.

Report

Share

Report

Share

Recommended

Lect20 Engin112

This document discusses sequential circuits and flip flops. It explains that flip flops can store data on the rising or falling edge of a trigger signal, unlike latches which store data based on trigger levels. Different types of flip flops like D, J-K, and T flip flops are described along with their characteristics. Asynchronous inputs allow flip flops to be preset or cleared independently of the clock. Multiple flip flops can be used together to store parallel data, forming the basis of computer memory.

Flip flops

This document discusses various types of flip-flops including SR, D, JK, and T flip-flops. It provides details on their structure and operation through descriptions and truth tables. The SR flip-flop uses an edge detector circuit to trigger on clock pulses. The D flip-flop is built from an SR flip-flop. The JK flip-flop eliminates uncertainty when the SR inputs are both 1. The T flip-flop is a modification of the JK flip-flop that toggles its output when the input T is 1. References are provided for additional information on digital electronics and flip-flop principles.

Chapter 3

The document discusses sequential circuits and their components. It begins with an overview of sequential circuits and finite state machines. It then covers different types of flip-flops like D flip-flops and their usage. Counters and sequencers are presented as examples of sequential circuits. Details about designing a 3-bit up counter like its state table and logic equations are provided. Finally, registers are discussed including an example of a 4-bit register with parallel load.

Trts d flip flop1

This document discusses D flip-flops. It states that a D flip-flop stores one bit of data and its output, Q, follows the input, D, at the rising or falling edge of the clock signal, CLK. A D flip-flop can be constructed by adding an inverter to an S-R flip-flop. The document provides examples of the timing diagram of a D flip-flop and how positive and negative edge triggered D flip-flops work. It also discusses using D flip-flops to create a ring counter and provides an example of a 6-bit ring counter with its output states over 6 clock cycles.

Flip flop

Flip flops are used to store digital data and can be triggered on either the rising or falling edge of a clock signal. The D flip flop stores the input data on the rising edge of the clock. Multiple flip flops can be used together to store parallel data from combinational logic circuits. Asynchronous reset inputs allow the flip flop output to be asynchronously cleared regardless of the clock. Flip flops are fundamental building blocks that enable the storage of data in digital circuits and computers.

Latch and flip flop

Latch and flip flop circuits are used to store digital information. A latch can store a bit as long as power is applied, while a flip flop uses feedback to store a bit even after inputs change. There are different types of flip flops like SR, JK, D and T flip flops that store bits based on their input conditions and clock signal. Flip flops are edge triggered which means they change state only on rising or falling edge of the clock signal. This provides synchronization between logic and memory in digital circuits.

state diagrams of flip flops

This document discusses state diagrams and state tables for sequential circuits. It describes how state diagrams use circles for system states and arcs for transitions between states due to events. State tables have sections for present state, next state, and output. They show the state of flip-flops before and after a clock pulse and output values. Examples of SR, JK, D and T flip-flops are provided along with their characteristic equations and state diagrams. Characteristic equations define the next state in terms of the present state and inputs.

Flip flop

1. A flip-flop is a basic element of sequential circuits that has two stable states and whose output depends on both the current input and its previous state.

2. An SR flip-flop can be constructed using two NOR gates, with states that are set by a high S input and reset by a high R input.

3. Gated flip-flops only change state in response to changes at the clock input, allowing the circuit response to be controlled at specific times.

Recommended

Lect20 Engin112

This document discusses sequential circuits and flip flops. It explains that flip flops can store data on the rising or falling edge of a trigger signal, unlike latches which store data based on trigger levels. Different types of flip flops like D, J-K, and T flip flops are described along with their characteristics. Asynchronous inputs allow flip flops to be preset or cleared independently of the clock. Multiple flip flops can be used together to store parallel data, forming the basis of computer memory.

Flip flops

This document discusses various types of flip-flops including SR, D, JK, and T flip-flops. It provides details on their structure and operation through descriptions and truth tables. The SR flip-flop uses an edge detector circuit to trigger on clock pulses. The D flip-flop is built from an SR flip-flop. The JK flip-flop eliminates uncertainty when the SR inputs are both 1. The T flip-flop is a modification of the JK flip-flop that toggles its output when the input T is 1. References are provided for additional information on digital electronics and flip-flop principles.

Chapter 3

The document discusses sequential circuits and their components. It begins with an overview of sequential circuits and finite state machines. It then covers different types of flip-flops like D flip-flops and their usage. Counters and sequencers are presented as examples of sequential circuits. Details about designing a 3-bit up counter like its state table and logic equations are provided. Finally, registers are discussed including an example of a 4-bit register with parallel load.

Trts d flip flop1

This document discusses D flip-flops. It states that a D flip-flop stores one bit of data and its output, Q, follows the input, D, at the rising or falling edge of the clock signal, CLK. A D flip-flop can be constructed by adding an inverter to an S-R flip-flop. The document provides examples of the timing diagram of a D flip-flop and how positive and negative edge triggered D flip-flops work. It also discusses using D flip-flops to create a ring counter and provides an example of a 6-bit ring counter with its output states over 6 clock cycles.

Flip flop

Flip flops are used to store digital data and can be triggered on either the rising or falling edge of a clock signal. The D flip flop stores the input data on the rising edge of the clock. Multiple flip flops can be used together to store parallel data from combinational logic circuits. Asynchronous reset inputs allow the flip flop output to be asynchronously cleared regardless of the clock. Flip flops are fundamental building blocks that enable the storage of data in digital circuits and computers.

Latch and flip flop

Latch and flip flop circuits are used to store digital information. A latch can store a bit as long as power is applied, while a flip flop uses feedback to store a bit even after inputs change. There are different types of flip flops like SR, JK, D and T flip flops that store bits based on their input conditions and clock signal. Flip flops are edge triggered which means they change state only on rising or falling edge of the clock signal. This provides synchronization between logic and memory in digital circuits.

state diagrams of flip flops

This document discusses state diagrams and state tables for sequential circuits. It describes how state diagrams use circles for system states and arcs for transitions between states due to events. State tables have sections for present state, next state, and output. They show the state of flip-flops before and after a clock pulse and output values. Examples of SR, JK, D and T flip-flops are provided along with their characteristic equations and state diagrams. Characteristic equations define the next state in terms of the present state and inputs.

Flip flop

1. A flip-flop is a basic element of sequential circuits that has two stable states and whose output depends on both the current input and its previous state.

2. An SR flip-flop can be constructed using two NOR gates, with states that are set by a high S input and reset by a high R input.

3. Gated flip-flops only change state in response to changes at the clock input, allowing the circuit response to be controlled at specific times.

Latches and flip flop

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.

2.3 sequantial logic circuit

This document discusses sequential logic circuits and flip-flops. It begins by defining sequential logic and differentiating it from combinational logic. It then describes flip-flops as the basic building blocks of sequential logic that provide memory. It identifies four common types of flip-flops - SR, JK, D and T - and describes their operation, truth tables and implementation using logic gates. The document provides details on each type of flip-flop to help understand their functionality and applications in sequential logic circuits.

Rs flipflop or SR flipFlop

Rs flipflop or SR flipFLop

You can watch my lectures at:

Digital electronics playlist in my youtube channel:

https://www.youtube.com/channel/UC_fItK7wBO6zdWHVPIYV8dQ?view_as=subscriber

My Website : https://easyninspire.blogspot.com/

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...Hsien-Hsin Sean Lee, Ph.D.

1) The document discusses switches and CMOS transistors. It describes how a basic switch works and analogizes it to a transistor.

2) It then covers transistor characteristics like cut-off, linear, and saturation regions. Threshold voltage and factors affecting it are also discussed.

3) Switch logic is examined for switches in series (AND function) and parallel (OR function).

4) CMOS transistors are introduced, including nMOS and pMOS types. A transmission gate using both is described for transmitting signals without degradation.Edge Trigged Flip Flops

Edge Trigged Flip Flpps, this presentation will cover the following topics

Flip Flops

Properties of flip flops

Edge trigged flip flops

THE EDGE TRIGGERED S-R FLIP FLOPS

THE EDGE TRIGGERED J-K FLIP FLOPS

THE EDGE TRIGGERED D FLIP FLOPS

THE EDGE TRIGGERED T FLIP FLOPS

Operating characteristics of edge trigged flip flops

Flip-Flop (Clocked Bistable)

This document discusses various types of digital logic gates and flip-flops, including their functionality and applications. It covers topics such as RS latches, JK flip-flops, D flip-flops, T flip-flops, switch debouncing, and synchronous vs. asynchronous logic. The document also explains concepts like clocked inputs, setup and hold times, and positive and negative edge triggering.

Lect19 Engin112

This document discusses sequential circuits called latches that are used to store data. It describes how latches are built using logic gates like NAND and NOR gates. Specifically, it explains the basic S-R latch which can be set or reset, and how adding control logic converts it into a D latch that stores the data input when a clock signal is high. Latches are important because they allow circuits to store intermediate values, unlike combinational logic which only responds to current inputs.

Logic Design - Chapter 6: Flip Flops

This document discusses sequential logic circuits and flip-flops. It begins with set-reset latches using NOR and NAND gates and their truth tables. It then covers clocked SR latches which become flip-flops. Different types of flip-flops are examined like JK, T, and D flip-flops. It discusses issues like race conditions and solutions like master-slave flip-flops. Timing diagrams and examples of different flip-flop types responding to inputs are provided.

Clocked Sequential circuit analysis and design

The presentation covers clocked sequential circuit analysis and design process demonstrated with example. State reduction and state assignment is design is also described.

Sequential logic circuit

1) The document discusses sequential logic circuits and covers topics like latches, flip-flops, their analysis and modeling in hardware description languages.

2) It describes various types of latches and flip-flops like SR, D, JK, T flip-flops and compares their operations.

3) Guidelines are provided for designing synchronous sequential circuits which include deriving a state diagram and table, reducing states, assigning codes, deriving equations and drawing the logic diagram.

Understanding Flip Flops

A flip-flop is a basic component of computer memory that has two main states (0 or 1) and remains in that state even after the input is removed. There are two main types of flip-flops - NOR and NAND - which are made up of basic latch components. A latch uses feedback to remember its state, and flip-flops add a clock that controls when the latch can change states.

Combinational circuits

A combinational circuit is composed of basic logic gates like NOT, AND, and OR gates. Logic gates perform operations using combinations of input signals to produce output signals. An OR gate outputs a 1 if any or both of its inputs are 1. An AND gate outputs a 1 only if both inputs are 1. A NOT gate, or inverter, outputs the opposite of its single input. Combinational circuits use these logic gates together to perform more complex logical operations on multiple inputs and produce a single output.

Introduction state machine

A state machine is a system that can be described by a set of states that the system transitions through. It has a set of inputs, outputs, and memory. There are two main types - Mealy machines where the output is a function of the state and inputs, and Moore machines where the output is only a function of the state. To design a state machine, you first understand the problem, draw a state diagram, reduce states if possible, assign states, and design the circuit from the state table. An example is a serial adder where each bit is added sequentially using states to track the carry.

Flip flops

The document discusses sequential circuits and their basic components. It describes how SR latches can store a bit using feedback and how their behavior can be represented using truth tables and state diagrams. SR latches are glitch sensitive. D latches and D flip-flops are also discussed, with latches being level sensitive and flip-flops edge triggered. Other types of flip-flops include T and J-K flip-flops. A master-slave J-K flip-flop is shown to realize a clocked J-K flip-flop using two SR latches.

Designing Clocked Synchronous State Machine

The document describes the design of a synchronous state machine that detects a 0101 input sequence. It begins with the state diagram and transition table, then derives the excitation and output equations. The circuit diagram shows it uses D-type flip-flops for the state elements and logic gates to generate the next state and output based on the current state and input. It will output a 1 whenever the 0101 sequence is detected in the input stream and a 0 otherwise.

Lec9

This document discusses sequential circuits and their analysis and design. It begins by defining sequential circuits and their basic components like latches and flip-flops. It then covers analyzing synchronous sequential circuits using their output functions, state equations, and state tables. The document concludes by outlining the steps for designing a synchronous sequential circuit from its specification.

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...Hsien-Hsin Sean Lee, Ph.D.

This document discusses combinational logic and mixed logic design. It begins by defining combinational circuits as those whose outputs are determined immediately by the current input combination, without any internal storage. The document then presents an example of designing a 9-input odd function hierarchically using 3-input odd functions. Mixed logic design is introduced to allow implementing combinational logic using only NAND gates, only NOR gates, or both. DeMorgan's laws are used to convert gate types by adding or removing bubbles on the inputs. Several examples showcase designing logic circuits using only NAND gates or only NOR gates.Logic Design - Chapter 7: Sequential Circuit Analysis and Design

- CLASSIFICATION OF COUNTERS.

- RIPPLE COUNTERS (ASYNCHRONOUS COUNTERS).

- 3-bit Asynchronous Binary counter.

- COUNT SEQUENCE .

- DOWN COUNTERS.

- DESIGN OF DIVIDE – BY – N COUNTERS.

- BCD RIPPLE (DECADE) COUNTER.

- SYNCHRONOUS COUNTERS.

- SYNCHRONOUS BINARY DOWN-COUNTER.

- UP/DOWN SYNCHRONOUS COUNTERS.

Digital_Electronics_Module_4_Sequential_Circuits v0.6.pptx

This document discusses sequential circuits and their components. It begins by defining sequential circuits as circuits whose outputs depend not only on present inputs but also past states, stored using latches and flip-flops. It then covers various types of sequential circuits and their basic components like latches, flip-flops, registers and counters. Specific latch and flip-flop types like SR, D, JK and T are described along with their characteristics. Applications of shift registers and different counter types are also mentioned.

5.8 Integrated circuits

This document provides an overview of integrated circuits and digital techniques including:

1) Half adders and full adders which are basic building blocks for addition. Parallel adders allow adding more bits. Subtraction is also discussed.

2) Flip-flops like R-S, D, and J-K which are used for temporary data storage, counting, and other operations. Their functions and truth tables are described.

3) Counters, registers, decoders, encoders and other integrated circuits which are constructed using flip-flops and perform operations like serial-parallel conversion.

Assignment#5

This document discusses various types of flip flops including RS, JK, D, and T flip flops. It provides the theory of sequential circuits and flip flops. It also gives the truth tables and explanations for each type of flip flop. The aim is to verify the truth tables of these flip flops experimentally using logic gates, input switches, and output LEDs. The procedure and result are to check the components, make the circuit connections, provide various input combinations, and note the output to verify the truth tables for each flip flop type.

Dee2034 chapter 4 flip flop for students part

This document discusses types of flip flops used in sequential circuits. It begins by introducing sequential circuits and flip flops. The most basic flip flop is the SR flip flop, which can be constructed using either NAND or NOR gates. The document describes the logic symbol, truth table, and operation of the SR flip flop. It then discusses clocked SR flip flops and other types of flip flops like JK and T flip flops. The document provides examples of determining the output of SR flip flops given different input waveforms. It concludes by introducing the clock signal which controls when outputs of clocked sequential circuits can change state.

More Related Content

What's hot

Latches and flip flop

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.

2.3 sequantial logic circuit

This document discusses sequential logic circuits and flip-flops. It begins by defining sequential logic and differentiating it from combinational logic. It then describes flip-flops as the basic building blocks of sequential logic that provide memory. It identifies four common types of flip-flops - SR, JK, D and T - and describes their operation, truth tables and implementation using logic gates. The document provides details on each type of flip-flop to help understand their functionality and applications in sequential logic circuits.

Rs flipflop or SR flipFlop

Rs flipflop or SR flipFLop

You can watch my lectures at:

Digital electronics playlist in my youtube channel:

https://www.youtube.com/channel/UC_fItK7wBO6zdWHVPIYV8dQ?view_as=subscriber

My Website : https://easyninspire.blogspot.com/

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...Hsien-Hsin Sean Lee, Ph.D.

1) The document discusses switches and CMOS transistors. It describes how a basic switch works and analogizes it to a transistor.

2) It then covers transistor characteristics like cut-off, linear, and saturation regions. Threshold voltage and factors affecting it are also discussed.

3) Switch logic is examined for switches in series (AND function) and parallel (OR function).

4) CMOS transistors are introduced, including nMOS and pMOS types. A transmission gate using both is described for transmitting signals without degradation.Edge Trigged Flip Flops

Edge Trigged Flip Flpps, this presentation will cover the following topics

Flip Flops

Properties of flip flops

Edge trigged flip flops

THE EDGE TRIGGERED S-R FLIP FLOPS

THE EDGE TRIGGERED J-K FLIP FLOPS

THE EDGE TRIGGERED D FLIP FLOPS

THE EDGE TRIGGERED T FLIP FLOPS

Operating characteristics of edge trigged flip flops

Flip-Flop (Clocked Bistable)

This document discusses various types of digital logic gates and flip-flops, including their functionality and applications. It covers topics such as RS latches, JK flip-flops, D flip-flops, T flip-flops, switch debouncing, and synchronous vs. asynchronous logic. The document also explains concepts like clocked inputs, setup and hold times, and positive and negative edge triggering.

Lect19 Engin112

This document discusses sequential circuits called latches that are used to store data. It describes how latches are built using logic gates like NAND and NOR gates. Specifically, it explains the basic S-R latch which can be set or reset, and how adding control logic converts it into a D latch that stores the data input when a clock signal is high. Latches are important because they allow circuits to store intermediate values, unlike combinational logic which only responds to current inputs.

Logic Design - Chapter 6: Flip Flops

This document discusses sequential logic circuits and flip-flops. It begins with set-reset latches using NOR and NAND gates and their truth tables. It then covers clocked SR latches which become flip-flops. Different types of flip-flops are examined like JK, T, and D flip-flops. It discusses issues like race conditions and solutions like master-slave flip-flops. Timing diagrams and examples of different flip-flop types responding to inputs are provided.

Clocked Sequential circuit analysis and design

The presentation covers clocked sequential circuit analysis and design process demonstrated with example. State reduction and state assignment is design is also described.

Sequential logic circuit

1) The document discusses sequential logic circuits and covers topics like latches, flip-flops, their analysis and modeling in hardware description languages.

2) It describes various types of latches and flip-flops like SR, D, JK, T flip-flops and compares their operations.

3) Guidelines are provided for designing synchronous sequential circuits which include deriving a state diagram and table, reducing states, assigning codes, deriving equations and drawing the logic diagram.

Understanding Flip Flops

A flip-flop is a basic component of computer memory that has two main states (0 or 1) and remains in that state even after the input is removed. There are two main types of flip-flops - NOR and NAND - which are made up of basic latch components. A latch uses feedback to remember its state, and flip-flops add a clock that controls when the latch can change states.

Combinational circuits

A combinational circuit is composed of basic logic gates like NOT, AND, and OR gates. Logic gates perform operations using combinations of input signals to produce output signals. An OR gate outputs a 1 if any or both of its inputs are 1. An AND gate outputs a 1 only if both inputs are 1. A NOT gate, or inverter, outputs the opposite of its single input. Combinational circuits use these logic gates together to perform more complex logical operations on multiple inputs and produce a single output.

Introduction state machine

A state machine is a system that can be described by a set of states that the system transitions through. It has a set of inputs, outputs, and memory. There are two main types - Mealy machines where the output is a function of the state and inputs, and Moore machines where the output is only a function of the state. To design a state machine, you first understand the problem, draw a state diagram, reduce states if possible, assign states, and design the circuit from the state table. An example is a serial adder where each bit is added sequentially using states to track the carry.

Flip flops

The document discusses sequential circuits and their basic components. It describes how SR latches can store a bit using feedback and how their behavior can be represented using truth tables and state diagrams. SR latches are glitch sensitive. D latches and D flip-flops are also discussed, with latches being level sensitive and flip-flops edge triggered. Other types of flip-flops include T and J-K flip-flops. A master-slave J-K flip-flop is shown to realize a clocked J-K flip-flop using two SR latches.

Designing Clocked Synchronous State Machine

The document describes the design of a synchronous state machine that detects a 0101 input sequence. It begins with the state diagram and transition table, then derives the excitation and output equations. The circuit diagram shows it uses D-type flip-flops for the state elements and logic gates to generate the next state and output based on the current state and input. It will output a 1 whenever the 0101 sequence is detected in the input stream and a 0 otherwise.

Lec9

This document discusses sequential circuits and their analysis and design. It begins by defining sequential circuits and their basic components like latches and flip-flops. It then covers analyzing synchronous sequential circuits using their output functions, state equations, and state tables. The document concludes by outlining the steps for designing a synchronous sequential circuit from its specification.

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...Hsien-Hsin Sean Lee, Ph.D.

This document discusses combinational logic and mixed logic design. It begins by defining combinational circuits as those whose outputs are determined immediately by the current input combination, without any internal storage. The document then presents an example of designing a 9-input odd function hierarchically using 3-input odd functions. Mixed logic design is introduced to allow implementing combinational logic using only NAND gates, only NOR gates, or both. DeMorgan's laws are used to convert gate types by adding or removing bubbles on the inputs. Several examples showcase designing logic circuits using only NAND gates or only NOR gates.Logic Design - Chapter 7: Sequential Circuit Analysis and Design

- CLASSIFICATION OF COUNTERS.

- RIPPLE COUNTERS (ASYNCHRONOUS COUNTERS).

- 3-bit Asynchronous Binary counter.

- COUNT SEQUENCE .

- DOWN COUNTERS.

- DESIGN OF DIVIDE – BY – N COUNTERS.

- BCD RIPPLE (DECADE) COUNTER.

- SYNCHRONOUS COUNTERS.

- SYNCHRONOUS BINARY DOWN-COUNTER.

- UP/DOWN SYNCHRONOUS COUNTERS.

What's hot (18)

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...

Lec9 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Com...

Logic Design - Chapter 7: Sequential Circuit Analysis and Design

Logic Design - Chapter 7: Sequential Circuit Analysis and Design

Similar to Sequential circuits

Digital_Electronics_Module_4_Sequential_Circuits v0.6.pptx

This document discusses sequential circuits and their components. It begins by defining sequential circuits as circuits whose outputs depend not only on present inputs but also past states, stored using latches and flip-flops. It then covers various types of sequential circuits and their basic components like latches, flip-flops, registers and counters. Specific latch and flip-flop types like SR, D, JK and T are described along with their characteristics. Applications of shift registers and different counter types are also mentioned.

5.8 Integrated circuits

This document provides an overview of integrated circuits and digital techniques including:

1) Half adders and full adders which are basic building blocks for addition. Parallel adders allow adding more bits. Subtraction is also discussed.

2) Flip-flops like R-S, D, and J-K which are used for temporary data storage, counting, and other operations. Their functions and truth tables are described.

3) Counters, registers, decoders, encoders and other integrated circuits which are constructed using flip-flops and perform operations like serial-parallel conversion.

Assignment#5

This document discusses various types of flip flops including RS, JK, D, and T flip flops. It provides the theory of sequential circuits and flip flops. It also gives the truth tables and explanations for each type of flip flop. The aim is to verify the truth tables of these flip flops experimentally using logic gates, input switches, and output LEDs. The procedure and result are to check the components, make the circuit connections, provide various input combinations, and note the output to verify the truth tables for each flip flop type.

Dee2034 chapter 4 flip flop for students part

This document discusses types of flip flops used in sequential circuits. It begins by introducing sequential circuits and flip flops. The most basic flip flop is the SR flip flop, which can be constructed using either NAND or NOR gates. The document describes the logic symbol, truth table, and operation of the SR flip flop. It then discusses clocked SR flip flops and other types of flip flops like JK and T flip flops. The document provides examples of determining the output of SR flip flops given different input waveforms. It concludes by introducing the clock signal which controls when outputs of clocked sequential circuits can change state.

SEQUENTIAL CIRCUITS -Module 5 (1).pptx

This document provides an introduction to sequential circuits and various types of flip-flops. It discusses the differences between combinational and sequential circuits, and describes SR, D, JK, T, and JK flip-flops. Their block diagrams, truth tables, characteristic tables, and excitation tables are presented. Applications of flip-flops such as counters, frequency dividers, shift registers, and data storage are also covered briefly. Finally, the document discusses various types of shift registers including serial-in serial-out, serial-in parallel-out, parallel-in serial-out, and parallel-in parallel-out.

Chapter 4 flip flop for students

This document discusses flip-flops and sequential circuits. It begins with an introduction to sequential circuits and flip-flops. There are several types of flip-flops discussed including SR flip-flops, clocked SR flip-flops, JK flip-flops, and T flip-flops. SR flip-flops can be constructed using either NAND or NOR gates. The document provides details on the logic diagrams, truth tables, and operation of SR flip-flops. It also discusses using a clock signal to control synchronous sequential circuits and provides examples of waveforms and exercises for SR flip-flops.

Flip flops & registers

1) Flip-flops are basic memory elements that store one bit of information as a 1 or 0. Common types include RS, D, JK, and T flip-flops.

2) Registers are groups of flip-flops that can store multiple bits and perform data processing. Data is loaded into registers by transferring new information during a clock pulse.

3) Master-slave JK flip-flops prevent racing conditions by using two flip-flops triggered on opposite clock edges, with the slave output following the master.

latchesandflipflops.ppt

This document discusses latches and flip-flops. It describes the SR latch, gated SR latch, D latch, and gated D latch. It also covers edge-triggered flip-flops including the SR, D, and JK flip-flops. The edge-triggered flip-flops are synchronous, bistable devices that change state based on the rising or falling edge of a clock pulse. Common applications of flip-flops include data storage, data transfer, counting, and frequency division.

Digital design slides for engineering

The document discusses different types of circuits including combinational and sequential circuits. It describes sequential circuits as having an output that depends on present inputs as well as past outputs. Several types of sequential circuits are then described in more detail, including synchronous sequential circuits which use a clock signal, and asynchronous sequential circuits which do not use a clock. Storage elements called latches and flip-flops are discussed, with flip-flops being preferred over latches in synchronous logic circuits due to their edge-triggered behavior. Different types of flip-flops such as SR, D, JK, and T flip-flops are described along with their characteristic equations and excitation tables. Registers are introduced as groups of flip-flops that can

Latches and flip flops

This document discusses latches and flip-flops. It describes the SR latch, gated SR latch, D latch, and gated D latch. It also covers edge-triggered flip-flops including the SR, D, and JK flip-flops. The key uses of flip-flops are for data storage, data transfer, counting, and frequency division in digital circuits and sequential logic.

Digital clock presentation

This document discusses JK flip-flops and their applications in counters and seven segment displays. It describes the structure of a JK flip-flop, including its inputs of J, K, PR, CLR and CLK, and its outputs of Q and Q'. It explains the four modes of operation for a JK flip-flop: hold, set, reset, and toggle. Counters are described as using multiple flip-flops connected in series to count pulses. Seven segment displays are discussed as a way to display numbers visually using an arrangement of LED segments, with drivers needed to interpret BCD input for the display.

8.flip flops and registers

Flip flops are basic memory elements that store one bit of information as a 1 or 0. Common types include RS, D, JK, T, and master-slave JK flip flops. Flip flops have two stable states and two complementary outputs. They are used as registers for storage, in frequency dividers, and digital counters. Registers consist of groups of flip flops that hold information, while shift registers can shift data in one or both directions using cascaded flip flops and clock pulses. Flip flops have applications in interfacing digital systems, as delay circuits, and for converting between serial and parallel data.

15CS32 ADE Module 4

This document discusses various topics related to flip-flops and shift registers including:

1. Flip-flop timing parameters like setup time, hold time, and propagation delay.

2. The JK master-slave flip-flop configuration which uses two flip-flops to avoid unwanted state changes.

3. Switch contact bounce and how an RS latch can be used in a de-bounce circuit.

4. Different representations of flip-flops like truth tables, characteristic tables, and state diagrams.

5. HDL implementations of different types of flip-flops.

6. Shift register types like serial-in serial-out, serial-in parallel-out, parallel-in serial-

Chapter 6: Sequential Logic

Sequential circuits are circuits whose outputs depend not only on present inputs but also on past inputs or states. There are two types: synchronous use a clock signal to synchronize state changes, asynchronous can change state at any time. Common memory elements are flip-flops including RS, D, JK, and T flip-flops. The master-slave flip-flop construction using two flip-flops avoids unpredictable states by separating the sampling and output functions.

10529144.ppt

Latches and flip-flops are basic forms of digital memory. Latches have two stable states and can be constructed from NOR or NAND gates. The most basic type is the S-R latch, which can be set or reset by applying a momentary input signal. Flip-flops differ in that they are clocked devices which change state only on a clock edge. Common types include the D flip-flop and J-K flip-flop.

JK flip flops

JK flip-flops have two outputs, Q and Q', and four modes of operation: hold, set, reset, toggle. The primary output is Q. There are two stable states that can store state information. JK flip-flops are used for data storage in registers, counting in counters, and frequency division. They can divide the frequency of a periodic waveform in half by toggling on each input clock pulse.

Latches and flip flops

This document discusses latches and flip-flops. It begins by explaining the difference between latches and flip-flops, noting that latches do not have a clock signal while flip-flops do. It then discusses several types of flip-flops - RS, Clocked RS, D, JK, and T - providing the definition, explanation, circuit diagram, and truth table for each. It also discusses several types of latches - SR, Gated SR, and D - providing the definition, explanation, and circuit diagram for each. The document aims to explain the key characteristics and workings of various latches and flip-flops.

Lab 12 – Latches and Flip-Flops Mugisha OmaryLab 12 .docx

The document discusses latches and flip-flops. It explains that latches can remain in the state they were set in even after input signals are removed. The main difference between latches and flip-flops is that latches are level-triggered while flip-flops are edge-triggered. Various latch and flip-flop circuits like D latches, SR latches, and JK flip-flops are described along with their truth tables. Experiments were conducted using integrated circuits to observe and verify the behavior of different latch and flip-flop circuits.

What are Flip Flops and Its types.

What are Flip Flops and Its types. What are Flip Flops and Its types. What are Flip Flops and Its types. What are Flip Flops and Its types. What are Flip Flops and Its types. What are Flip Flops and Its types. What are Flip Flops and Its types.

Similar to Sequential circuits (20)

Digital_Electronics_Module_4_Sequential_Circuits v0.6.pptx

Digital_Electronics_Module_4_Sequential_Circuits v0.6.pptx

Lab 12 – Latches and Flip-Flops Mugisha OmaryLab 12 .docx

Lab 12 – Latches and Flip-Flops Mugisha OmaryLab 12 .docx

Recently uploaded

Mechanical Engineering on AAI Summer Training Report-003.pdf

Mechanical Engineering PROJECT REPORT ON SUMMER VOCATIONAL TRAINING

AT MBB AIRPORT

一比一原版(USF毕业证)旧金山大学毕业证如何办理

原件一模一样【微信:95270640】【旧金山大学毕业证USF学位证成绩单】【微信:95270640】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

【业务选择办理准则】

一、工作未确定,回国需先给父母、亲戚朋友看下文凭的情况,办理一份就读学校的毕业证【微信:95270640】文凭即可

二、回国进私企、外企、自己做生意的情况,这些单位是不查询毕业证真伪的,而且国内没有渠道去查询国外文凭的真假,也不需要提供真实教育部认证。鉴于此,办理一份毕业证【微信:95270640】即可

三、进国企,银行,事业单位,考公务员等等,这些单位是必需要提供真实教育部认证的,办理教育部认证所需资料众多且烦琐,所有材料您都必须提供原件,我们凭借丰富的经验,快捷的绿色通道帮您快速整合材料,让您少走弯路。

留信网认证的作用:

1:该专业认证可证明留学生真实身份【微信:95270640】

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

办理旧金山大学毕业证毕业证学位证USF学位证【微信:95270640 】外观非常精致,由特殊纸质材料制成,上面印有校徽、校名、毕业生姓名、专业等信息。

办理旧金山大学毕业证USF学位证毕业证学位证【微信:95270640 】格式相对统一,各专业都有相应的模板。通常包括以下部分:

校徽:象征着学校的荣誉和传承。

校名:学校英文全称

授予学位:本部分将注明获得的具体学位名称。

毕业生姓名:这是最重要的信息之一,标志着该证书是由特定人员获得的。

颁发日期:这是毕业正式生效的时间,也代表着毕业生学业的结束。

其他信息:根据不同的专业和学位,可能会有一些特定的信息或章节。

办理旧金山大学毕业证毕业证学位证USF学位证【微信:95270640 】价值很高,需要妥善保管。一般来说,应放置在安全、干燥、防潮的地方,避免长时间暴露在阳光下。如需使用,最好使用复印件而不是原件,以免丢失。

综上所述,办理旧金山大学毕业证毕业证学位证USF学位证【微信:95270640 】是证明身份和学历的高价值文件。外观简单庄重,格式统一,包括重要的个人信息和发布日期。对持有人来说,妥善保管是非常重要的。

Use PyCharm for remote debugging of WSL on a Windo cf5c162d672e4e58b4dde5d797...

This document serves as a comprehensive step-by-step guide on how to effectively use PyCharm for remote debugging of the Windows Subsystem for Linux (WSL) on a local Windows machine. It meticulously outlines several critical steps in the process, starting with the crucial task of enabling permissions, followed by the installation and configuration of WSL.

The guide then proceeds to explain how to set up the SSH service within the WSL environment, an integral part of the process. Alongside this, it also provides detailed instructions on how to modify the inbound rules of the Windows firewall to facilitate the process, ensuring that there are no connectivity issues that could potentially hinder the debugging process.

The document further emphasizes on the importance of checking the connection between the Windows and WSL environments, providing instructions on how to ensure that the connection is optimal and ready for remote debugging.

It also offers an in-depth guide on how to configure the WSL interpreter and files within the PyCharm environment. This is essential for ensuring that the debugging process is set up correctly and that the program can be run effectively within the WSL terminal.

Additionally, the document provides guidance on how to set up breakpoints for debugging, a fundamental aspect of the debugging process which allows the developer to stop the execution of their code at certain points and inspect their program at those stages.

Finally, the document concludes by providing a link to a reference blog. This blog offers additional information and guidance on configuring the remote Python interpreter in PyCharm, providing the reader with a well-rounded understanding of the process.

VARIABLE FREQUENCY DRIVE. VFDs are widely used in industrial applications for...

Variable frequency drive .A Variable Frequency Drive (VFD) is an electronic device used to control the speed and torque of an electric motor by varying the frequency and voltage of its power supply. VFDs are widely used in industrial applications for motor control, providing significant energy savings and precise motor operation.

Applications of artificial Intelligence in Mechanical Engineering.pdf

Historically, mechanical engineering has relied heavily on human expertise and empirical methods to solve complex problems. With the introduction of computer-aided design (CAD) and finite element analysis (FEA), the field took its first steps towards digitization. These tools allowed engineers to simulate and analyze mechanical systems with greater accuracy and efficiency. However, the sheer volume of data generated by modern engineering systems and the increasing complexity of these systems have necessitated more advanced analytical tools, paving the way for AI.

AI offers the capability to process vast amounts of data, identify patterns, and make predictions with a level of speed and accuracy unattainable by traditional methods. This has profound implications for mechanical engineering, enabling more efficient design processes, predictive maintenance strategies, and optimized manufacturing operations. AI-driven tools can learn from historical data, adapt to new information, and continuously improve their performance, making them invaluable in tackling the multifaceted challenges of modern mechanical engineering.

Supermarket Management System Project Report.pdf

Supermarket management is a stand-alone J2EE using Eclipse Juno program.

This project contains all the necessary required information about maintaining

the supermarket billing system.

The core idea of this project to minimize the paper work and centralize the

data. Here all the communication is taken in secure manner. That is, in this

application the information will be stored in client itself. For further security the

data base is stored in the back-end oracle and so no intruders can access it.

Generative AI Use cases applications solutions and implementation.pdf

Generative AI solutions encompass a range of capabilities from content creation to complex problem-solving across industries. Implementing generative AI involves identifying specific business needs, developing tailored AI models using techniques like GANs and VAEs, and integrating these models into existing workflows. Data quality and continuous model refinement are crucial for effective implementation. Businesses must also consider ethical implications and ensure transparency in AI decision-making. Generative AI's implementation aims to enhance efficiency, creativity, and innovation by leveraging autonomous generation and sophisticated learning algorithms to meet diverse business challenges.

https://www.leewayhertz.com/generative-ai-use-cases-and-applications/

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Sinan from the Delivery Hero mobile infrastructure engineering team shares a deep dive into performance acceleration with Gradle build cache optimizations. Sinan shares their journey into solving complex build-cache problems that affect Gradle builds. By understanding the challenges and solutions found in our journey, we aim to demonstrate the possibilities for faster builds. The case study reveals how overlapping outputs and cache misconfigurations led to significant increases in build times, especially as the project scaled up with numerous modules using Paparazzi tests. The journey from diagnosing to defeating cache issues offers invaluable lessons on maintaining cache integrity without sacrificing functionality.

一比一原版(CalArts毕业证)加利福尼亚艺术学院毕业证如何办理

CalArts毕业证学历书【微信95270640】CalArts毕业证’圣力嘉学院毕业证《Q微信95270640》办理CalArts毕业证√文凭学历制作{CalArts文凭}购买学历学位证书本科硕士,CalArts毕业证学历学位证【实体公司】办毕业证、成绩单、学历认证、学位证、文凭认证、办留信网认证、(网上可查,实体公司,专业可靠)

(诚招代理)办理国外高校毕业证成绩单文凭学位证,真实使馆公证(留学回国人员证明)真实留信网认证国外学历学位认证雅思代考国外学校代申请名校保录开请假条改GPA改成绩ID卡

1.高仿业务:【本科硕士】毕业证,成绩单(GPA修改),学历认证(教育部认证),大学Offer,,ID,留信认证,使馆认证,雅思,语言证书等高仿类证书;

2.认证服务: 学历认证(教育部认证),大使馆认证(回国人员证明),留信认证(可查有编号证书),大学保录取,雅思保分成绩单。

3.技术服务:钢印水印烫金激光防伪凹凸版设计印刷激凸温感光标底纹镭射速度快。

办理加利福尼亚艺术学院加利福尼亚艺术学院毕业证文凭证书流程:

1客户提供办理信息:姓名生日专业学位毕业时间等(如信息不确定可以咨询顾问:我们有专业老师帮你查询);

2开始安排制作毕业证成绩单电子图;

3毕业证成绩单电子版做好以后发送给您确认;

4毕业证成绩单电子版您确认信息无误之后安排制作成品;

5成品做好拍照或者视频给您确认;

6快递给客户(国内顺丰国外DHLUPS等快读邮寄)

-办理真实使馆公证(即留学回国人员证明)

-办理各国各大学文凭(世界名校一对一专业服务,可全程监控跟踪进度)

-全套服务:毕业证成绩单真实使馆公证真实教育部认证。让您回国发展信心十足!

(详情请加一下 文凭顾问+微信:95270640)欢迎咨询!子小伍玩小伍比山娃小一岁虎头虎脑的很霸气父亲让山娃跟小伍去夏令营听课山娃很高兴夏令营就设在附近一所小学山娃发现那所小学比自己的学校更大更美操场上还铺有塑胶跑道呢里面很多小朋友一班一班的快快乐乐原来城里娃都藏这儿来了怪不得平时见不到他们山娃恍然大悟起来吹拉弹唱琴棋书画山娃都不懂却什么都想学山娃怨自己太笨什么都不会斟酌再三山娃终于选定了学美术当听说每月要交元时父亲犹豫了山娃也说爸算了吧咱学校一学期才转

Digital Twins Computer Networking Paper Presentation.pptx

A Digital Twin in computer networking is a virtual representation of a physical network, used to simulate, analyze, and optimize network performance and reliability. It leverages real-time data to enhance network management, predict issues, and improve decision-making processes.

Computational Engineering IITH Presentation

This Presentation will give you a brief idea about what Computational Engineering at IIT Hyderabad has to offer.

Recently uploaded (20)

Mechanical Engineering on AAI Summer Training Report-003.pdf

Mechanical Engineering on AAI Summer Training Report-003.pdf

Use PyCharm for remote debugging of WSL on a Windo cf5c162d672e4e58b4dde5d797...

Use PyCharm for remote debugging of WSL on a Windo cf5c162d672e4e58b4dde5d797...

VARIABLE FREQUENCY DRIVE. VFDs are widely used in industrial applications for...

VARIABLE FREQUENCY DRIVE. VFDs are widely used in industrial applications for...

Applications of artificial Intelligence in Mechanical Engineering.pdf

Applications of artificial Intelligence in Mechanical Engineering.pdf

4. Mosca vol I -Fisica-Tipler-5ta-Edicion-Vol-1.pdf

4. Mosca vol I -Fisica-Tipler-5ta-Edicion-Vol-1.pdf

Generative AI Use cases applications solutions and implementation.pdf

Generative AI Use cases applications solutions and implementation.pdf

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Digital Twins Computer Networking Paper Presentation.pptx

Digital Twins Computer Networking Paper Presentation.pptx

Sequential circuits

- 1. °2/17/2020

- 2. Mahasiswa dapat menjelaskan cara kerja komponen dasar rangkaian Sequential, yaitu Latch dan Flip-flop. °2/17/2020

- 4. Circuits require memory to store intermediate data Sequential circuits use a periodic signal to determine when to store values. ◦ A clock signal can determine storage times ◦ Clock signals are periodic Single bit storage element is a flip flop A basic type of flip flop is a latch Latches are made from logic gates ◦ NAND, NOR, AND, OR, Inverter °2/17/2020

- 5. Hasil operasi Rangkaian Logika Kombinasional adalah respon terhadap kombinasi input yang diberikan. Hanya bisa menjumlahkan dua bilangan. Untuk menjumlahkan bilangan ketiga, diperlukan penyimpanan informasi hasil penjumlahan sebelumnya. ▪ Contoh : 2+1 +5 ▪ 2 + 1 = 3 maka 3 disimpan di dalam memory, kemudian : ▪ 3 + 5 = 8 (a sequential operation); To handle this, we need sequential logic capable of storing intermediate (and final) results. °2/17/2020

- 6. °2/17/2020 Combinational circuit Flip Flops OutputsInputs Next state Present state Timing signal (clock) Clock Clock a periodic external event (input) synchronizes when current state changes happen keeps system well-behaved makes it easier to design and build large systems

- 7. °2/17/2020 1 1 1 0 0 1 0 0 S R Q Q’ 0 1 1 0 Set 1 0 Stable 0 1 Reset 0 0 Undefined R (reset) Q Q S (set) ° S-R latch made from cross-coupled NORs ° If Q = 1, set state ° If Q = 0, reset state ° Usually S=0 and R=0 ° S=1 and R=1 generates unpredictable results

- 8. °2/17/2020 S R Q Q’ 0 0 0 1 1 0 1 1 S R Q Q’ 0 1 1 0 Set 1 0 Store 0 1 Reset 1 1 Disallowed ° Latch made from cross-coupled NANDs ° Sometimes called S’-R’ latch ° Usually S=1 and R=1 ° S=0 and R=0 generates unpredictable results

- 9. °2/17/2020 ° Occasionally, desirable to avoid latch changes ° C = 0 disables all latch state changes ° Control signal enables data change when C = 1 ° Right side of circuit same as ordinary S-R latch.

- 10. Latch operation enabled by C Input sampling enabled by gates °2/17/2020 R’ S’ Q’ Q C’ Outputs change when C is low: RESET and SET Otherwise: HOLD Latch is level-sensitive, in regards to C Only stores data if C’ = 0

- 11. °2/17/2020 Q Q’ C D S R X Y X Y C Q Q’ 0 0 1 Q0 Q0’ Store 0 1 1 0 1 Reset 1 0 1 1 0 Set 1 1 1 1 1 Disallowed X X 0 Q0 Q0’ Store 0 1 0 1 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ ° Q0 indicates the previous state (the previously stored value)

- 12. °2/17/2020 Q Q’ C D S R X Y 0 1 0 1 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ ° Input value D is passed to output Q when C is high ° Input value D is ignored when C is low

- 13. °2/17/2020 E x Latches on following edge of clock E D Q C x z z ° Z only changes when E is high ° If E is high, Z will follow X

- 14. °2/17/2020 E x Latches on following edge of clock E D Q C x z z ° The D latch stores data indefinitely, regardless of input D values, if C = 0 ° Forms basic storage element in computers

- 15. °2/17/2020 ° SR latch is based on NOR gates ° S’R’ latch based on NAND gates ° D latch can be based on either. ° D latch sometimes called transparent latch

- 16. Latches are based on combinational gates (e.g. NAND, NOR) Latches store data even after data input has been removed S-R latches operate like cross-coupled inverters with control inputs (S = set, R = reset) With additional gates, an S-R latch can be converted to a D latch (D stands for data) D latch is simple to understand conceptually ◦ When C = 1, data input D stored in latch and output as Q ◦ When C = 0, data input D ignored and previous latch value output at Q °2/17/2020

- 17. Latches respond to trigger levels on control inputs ◦ Example: If G = 1, input reflected at output Difficult to precisely time when to store data with latches Flip flops store data on a rising or falling trigger edge. ◦ Example: control input transitions from 0 -> 1, data input appears at output ◦ Data remains stable in the flip flop until until next rising edge. Different types of flip flops serve different functions Flip flops can be defined with characteristic functions. °2/17/2020

- 18. °2/17/2020 Lo-Hi edgeHi-Lo edge ° What if the output only changed on a C transition? C D Q Q’ 0 0 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ Positive edge triggered

- 19. °2/17/2020 ° Consider two latches combined together ° Only one C value active at a time ° Output changes on falling edge of the clock

- 20. °2/17/2020 D gets latched to Q on the rising edge of the clock. ° Stores a value on the positive edge of C ° Input changes at other times have no effect on output C D Q Q’ 0 0 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ Positive edge triggered

- 21. °2/17/2020 ° Stores a value on the positive edge of C ° Input changes at other times have no effect on output

- 22. Positive Edge-Triggered J-K Flip-Flop 0 0 Q0 Q0’ 0 1 0 1 1 0 1 0 1 1 TOGGLE QJ Q’CLKK°Created from D flop °J sets °K resets °J=K=1 -> invert output °2/17/2020

- 23. °2/17/2020 ° Two data inputs, J and K ° J -> set, K -> reset, if J=K=1 then toggle output Characteristic Table

- 24. 2. Positive Edge-Triggered T Flip-Flop 0 Q0 Q0’ 1 TOGGLE Q Q’CT °Created from D flop °T=0 -> keep current °K resets °T=1 -> invert current °2/17/2020

- 25. °2/17/2020 • J, K are synchronous inputs o Effects on the output are synchronized with the CLK input. • Asynchronous inputs operate independently of the synchronous inputs and clock o Set the FF to 1/0 states at any time.

- 26. °2/17/2020

- 27. °2/17/2020 ° Flip flops store outputs from combinational logic ° Multiple flops can store a collection of data

- 28. Flip flops are powerful storage elements ◦ They can be constructed from gates and latches! D flip flop is simplest and most widely used Asynchronous inputs allow for clearing and presetting the flip flop output Multiple flops allow for data storage ◦ The basis of computer memory! Combine storage and logic to make a computation circuit Next time: Analyzing sequential circuits. °2/17/2020

- 29. Gunakan Multisim untuk merancang rangkaian penyimpan 3 bit data secara paralel. Kemudian data tersebut dihapus Diisi lagi dengan data baru °2/17/2020