Embed presentation

Download as PDF, PPTX

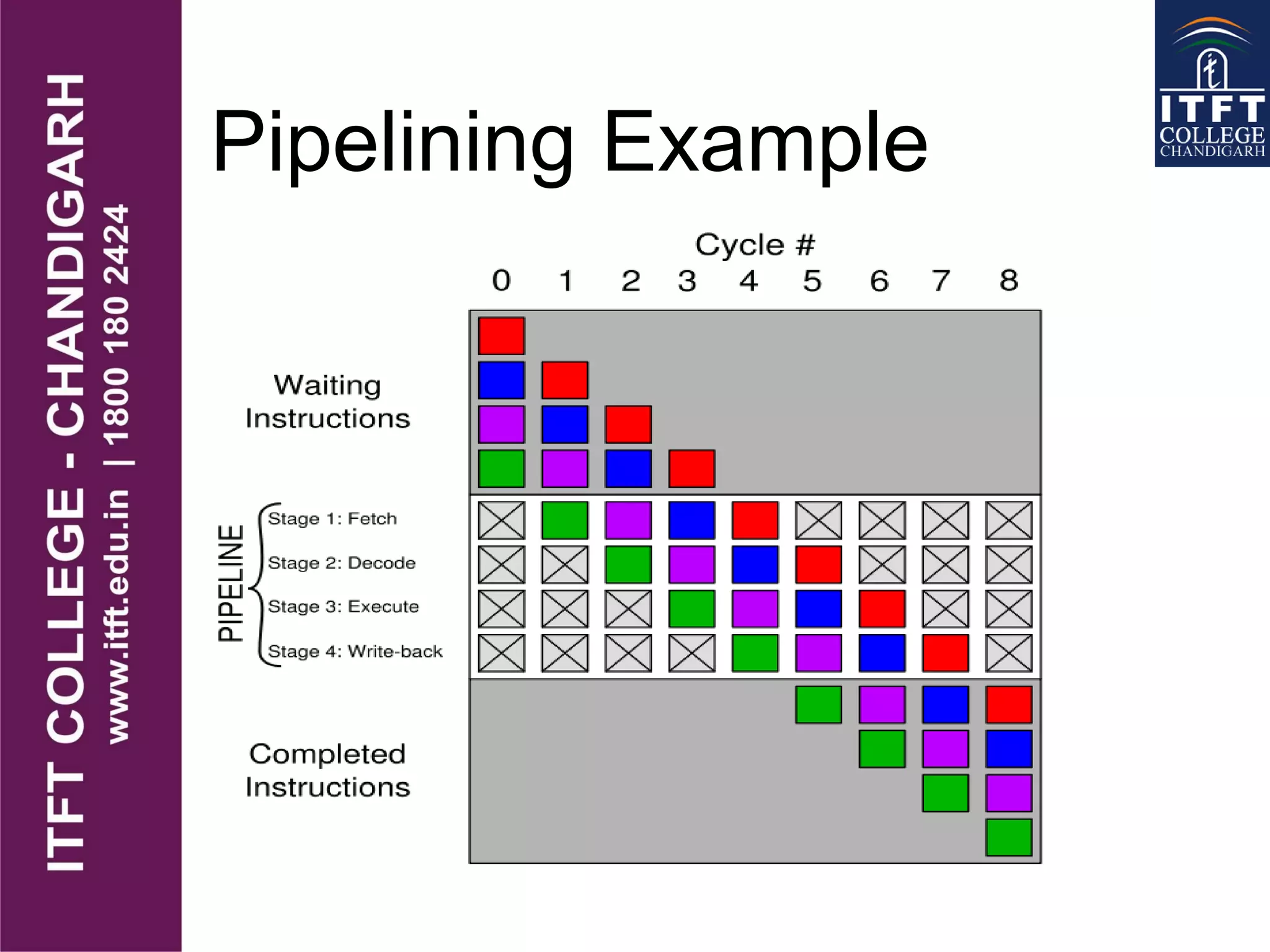

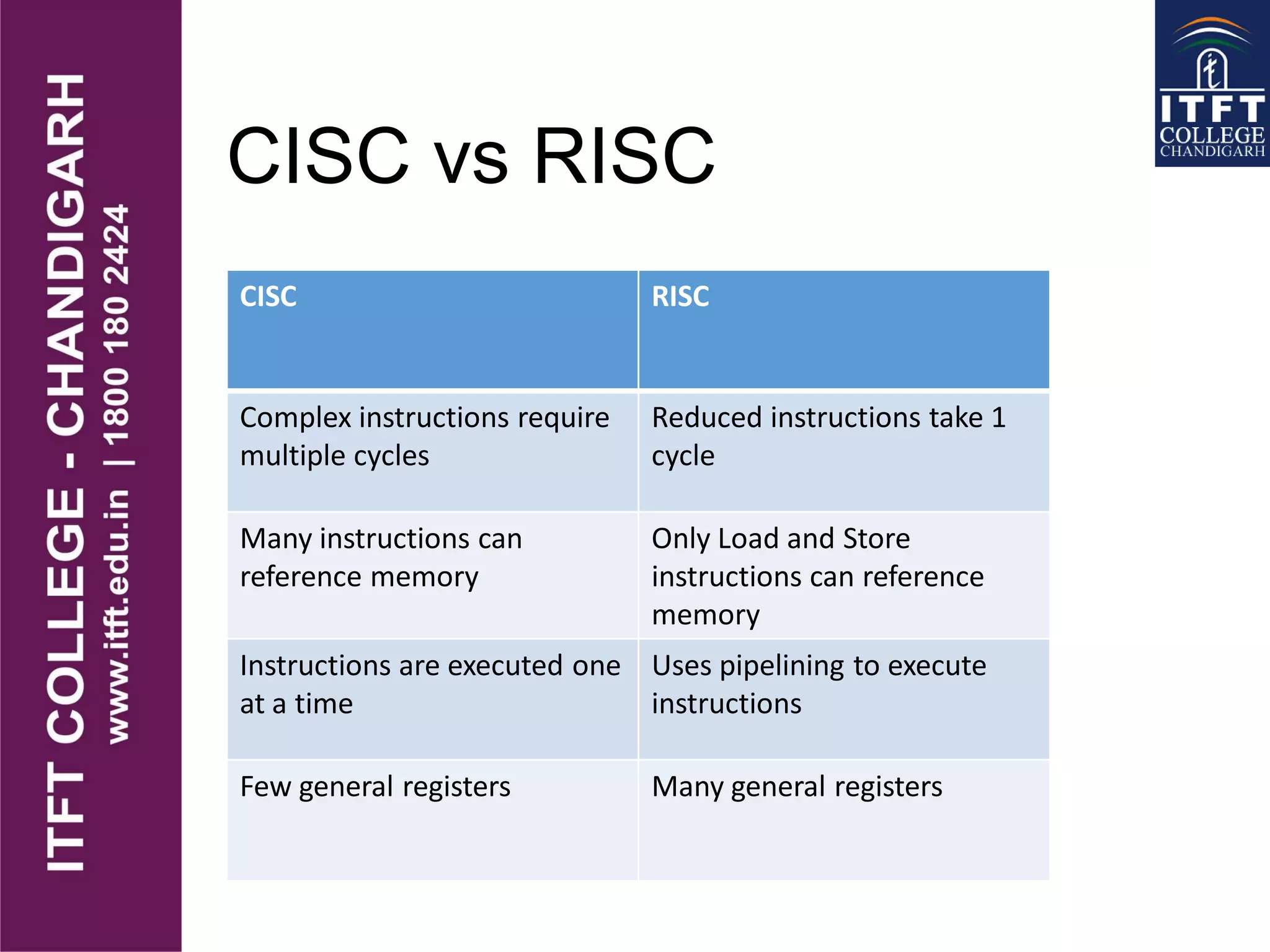

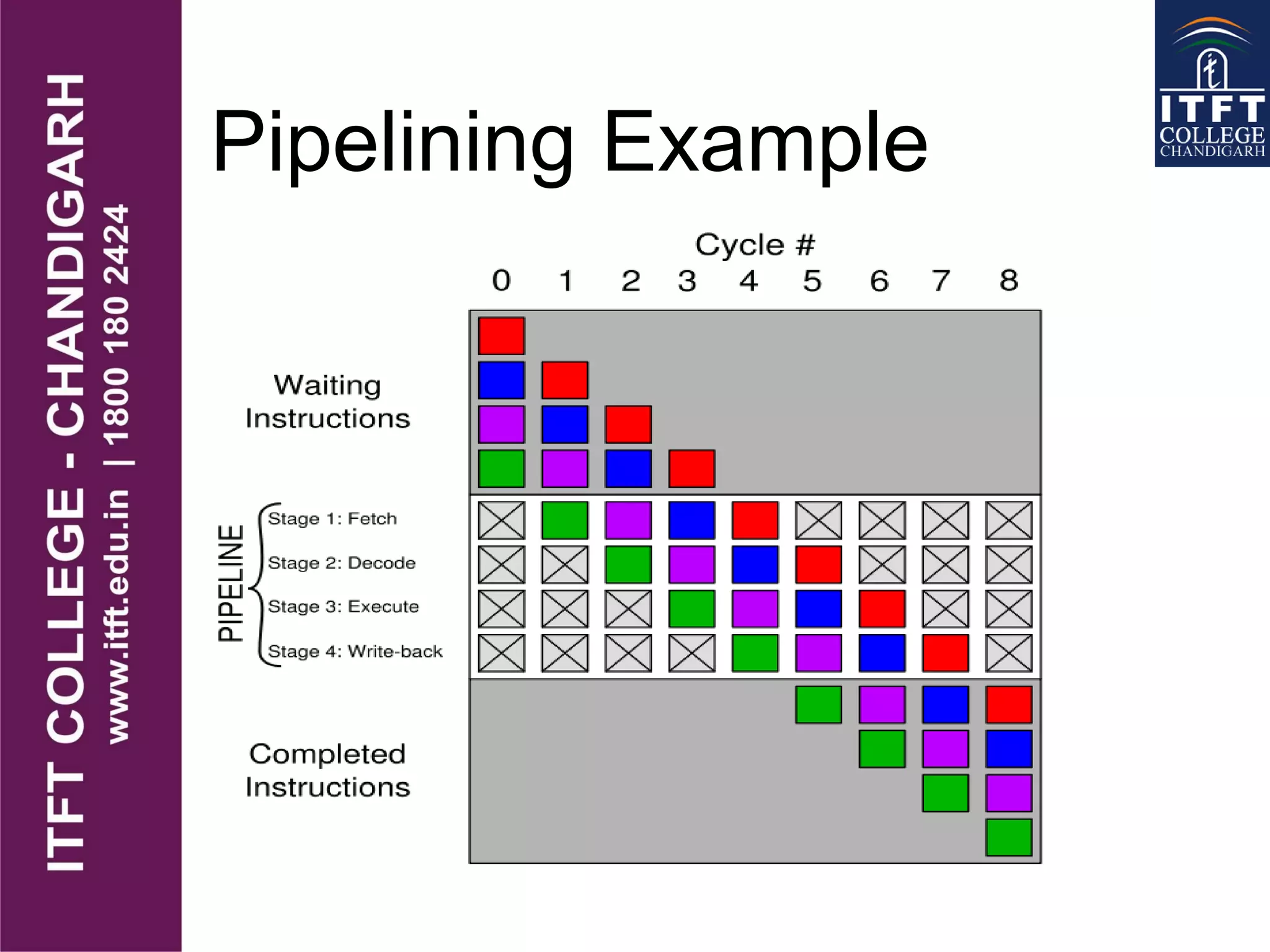

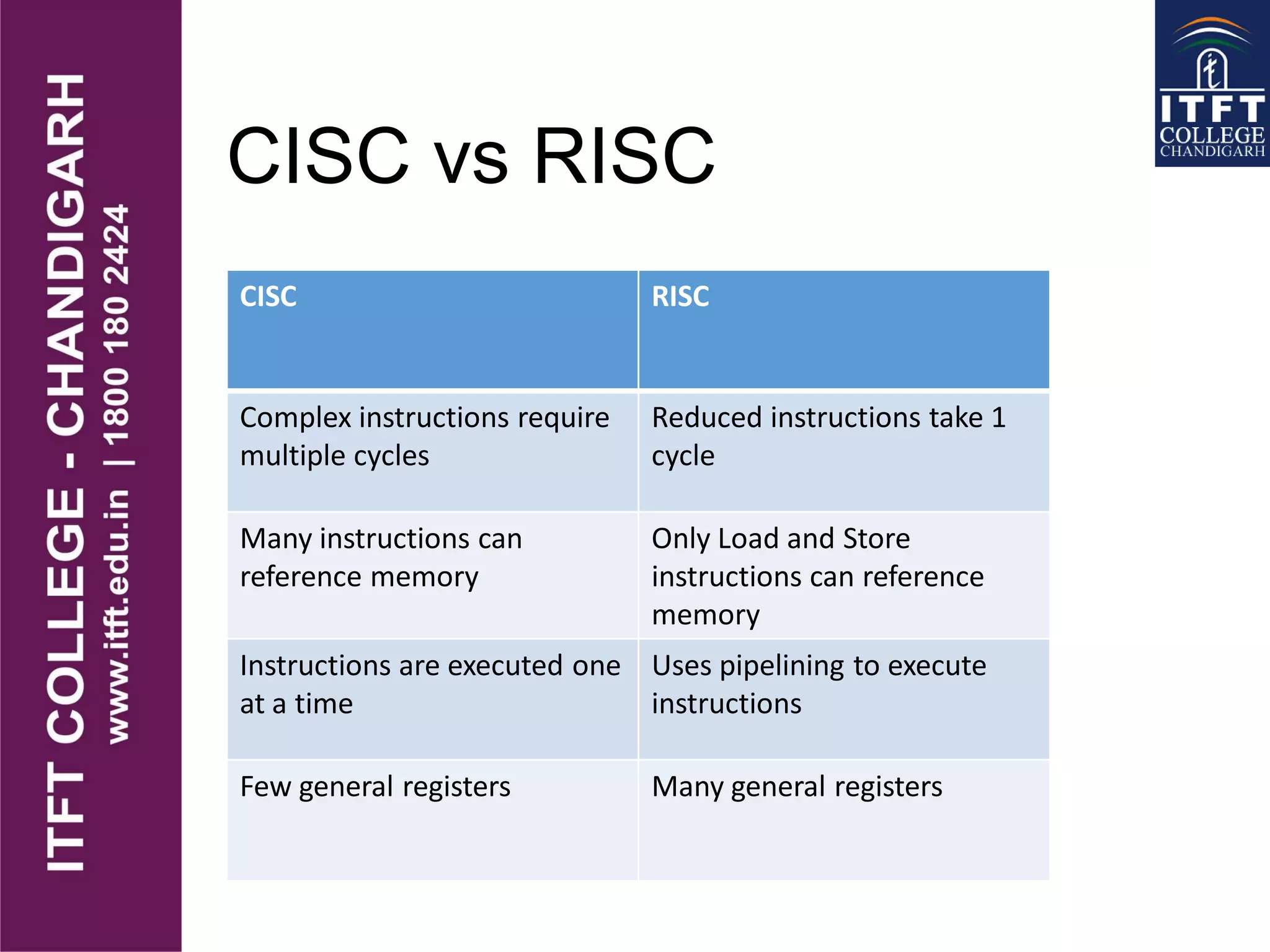

This document provides an overview of CISC and RISC architectures. CISC uses complex instructions that perform multiple low-level operations in one instruction, taking multiple clock cycles to execute. It has few general purpose registers. RISC uses simpler instructions that are executed in one clock cycle. It has many general purpose registers and only load and store instructions can access memory directly. Pipelining allows RISC processors to process multiple instructions simultaneously for improved efficiency compared to CISC which executes instructions sequentially.