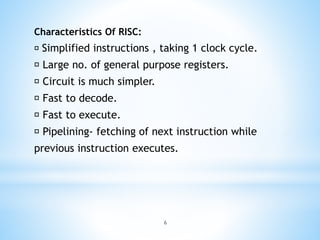

The presentation discusses RISC (Reduced Instruction Set Computer), a microprocessor architecture that uses a small set of optimized instructions for efficiency. It highlights the history, characteristics, and design principles of RISC, including simplified instruction execution, large register sets, and fixed-length instructions. RISC architectures are widely utilized in modern devices like cell phones and tablets, enabling faster microprocessor development.