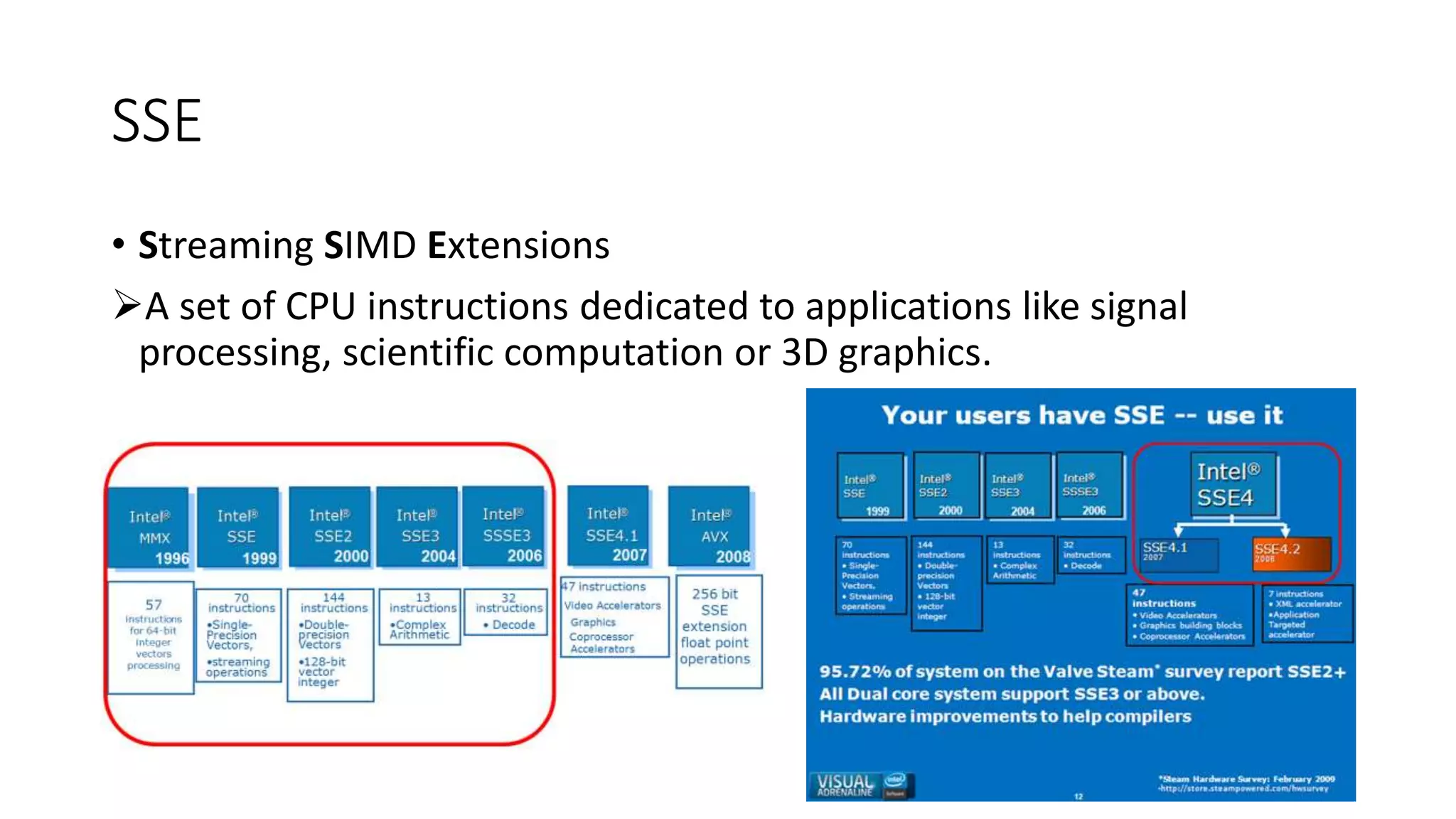

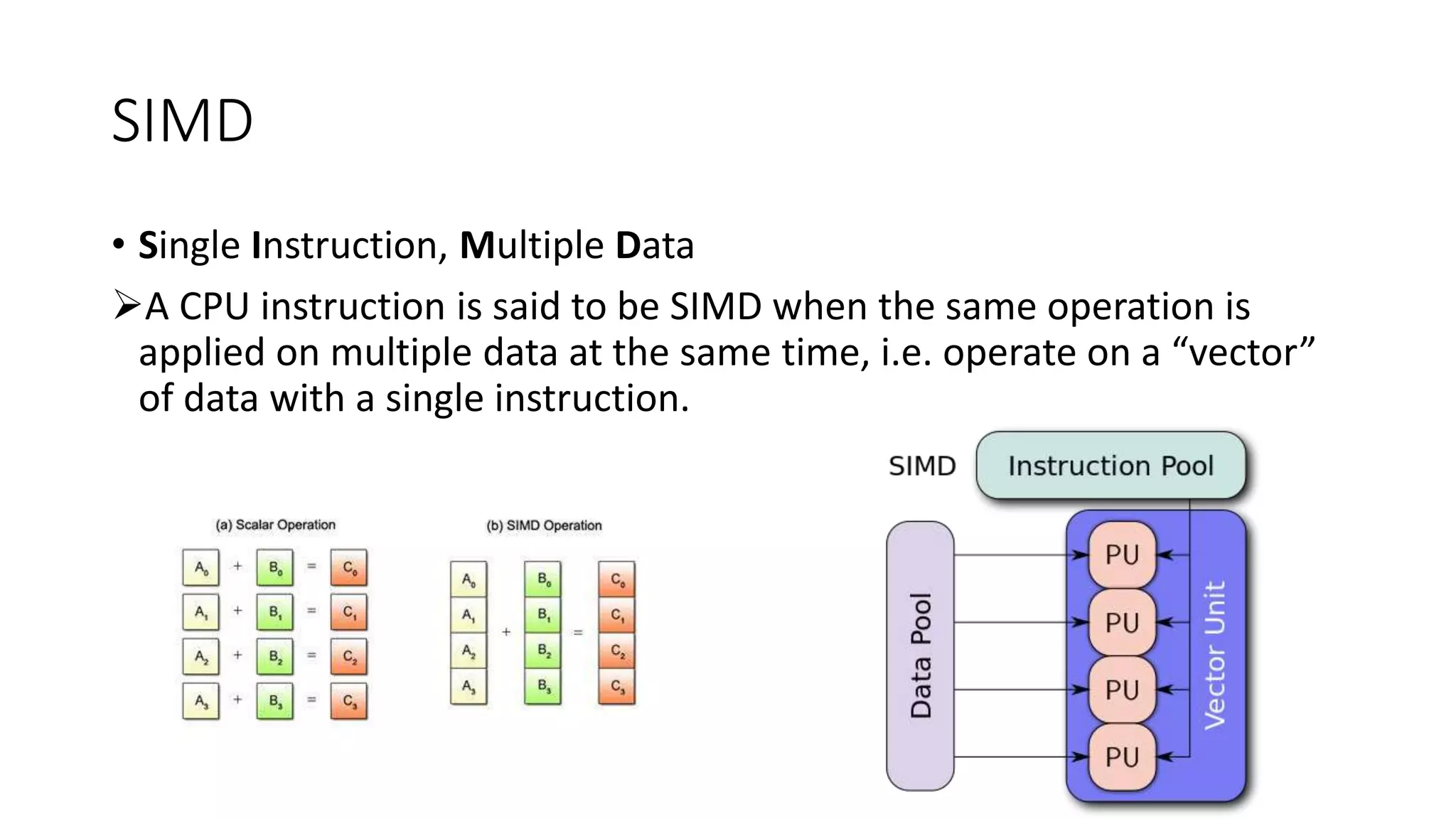

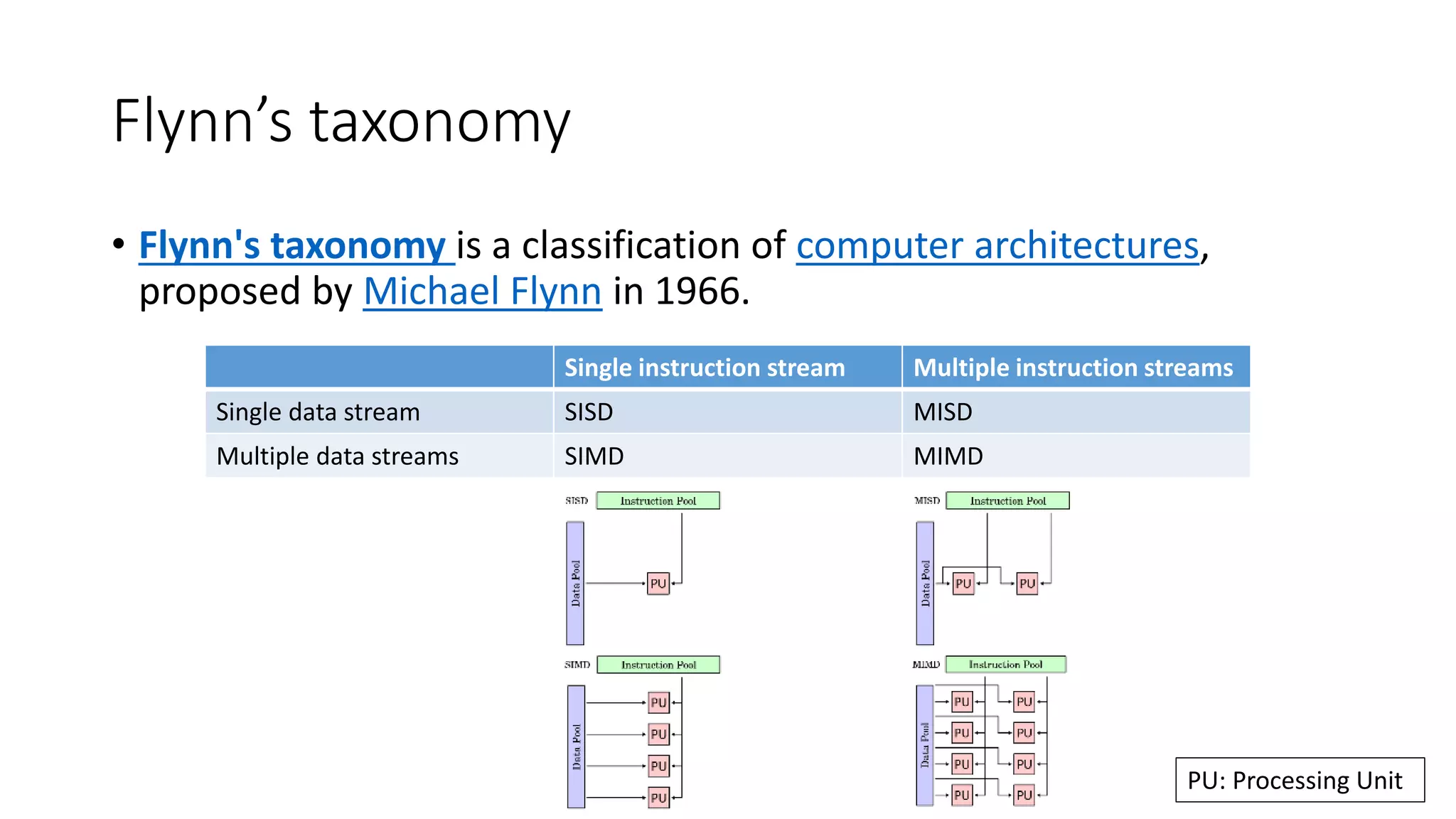

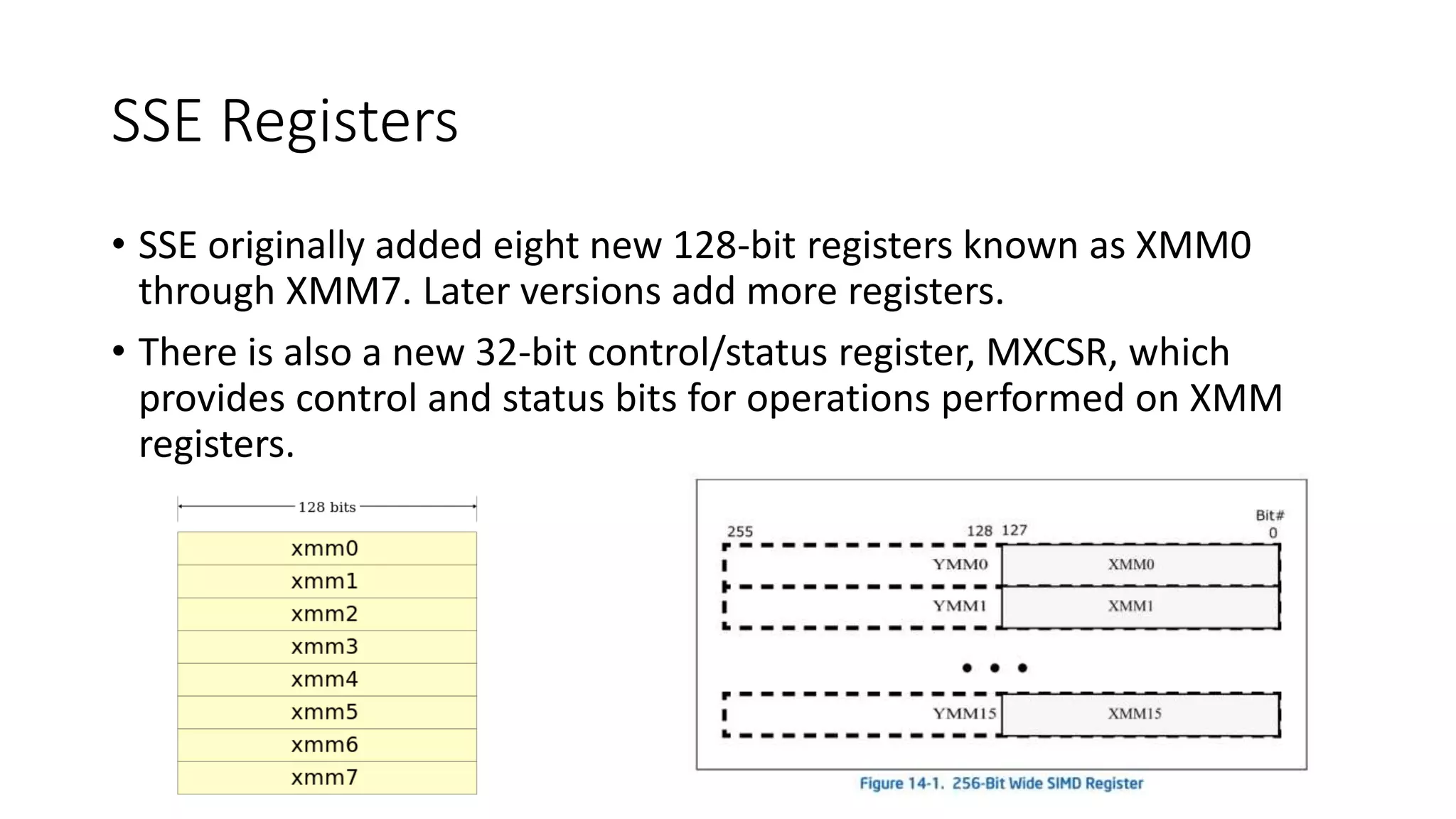

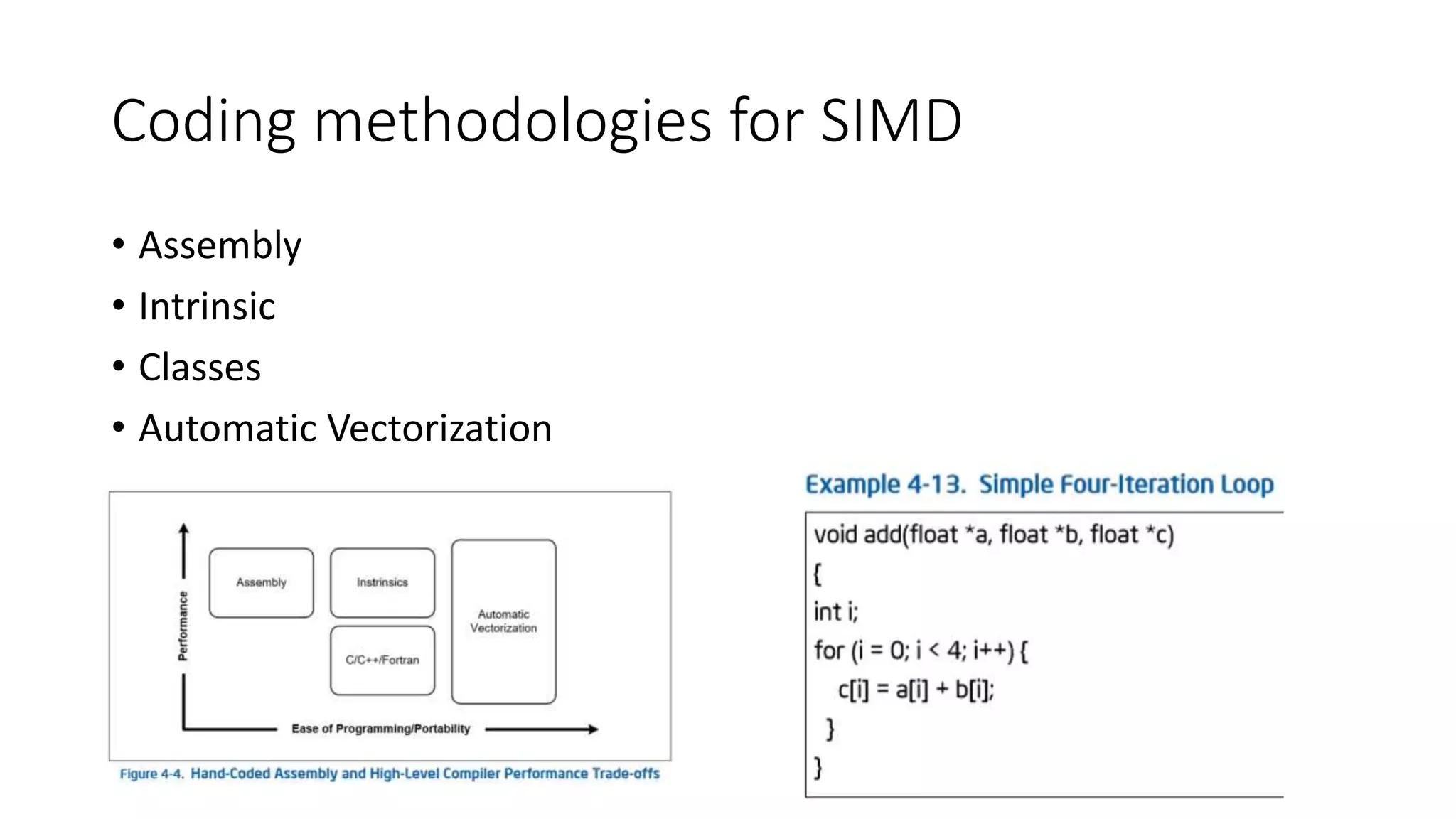

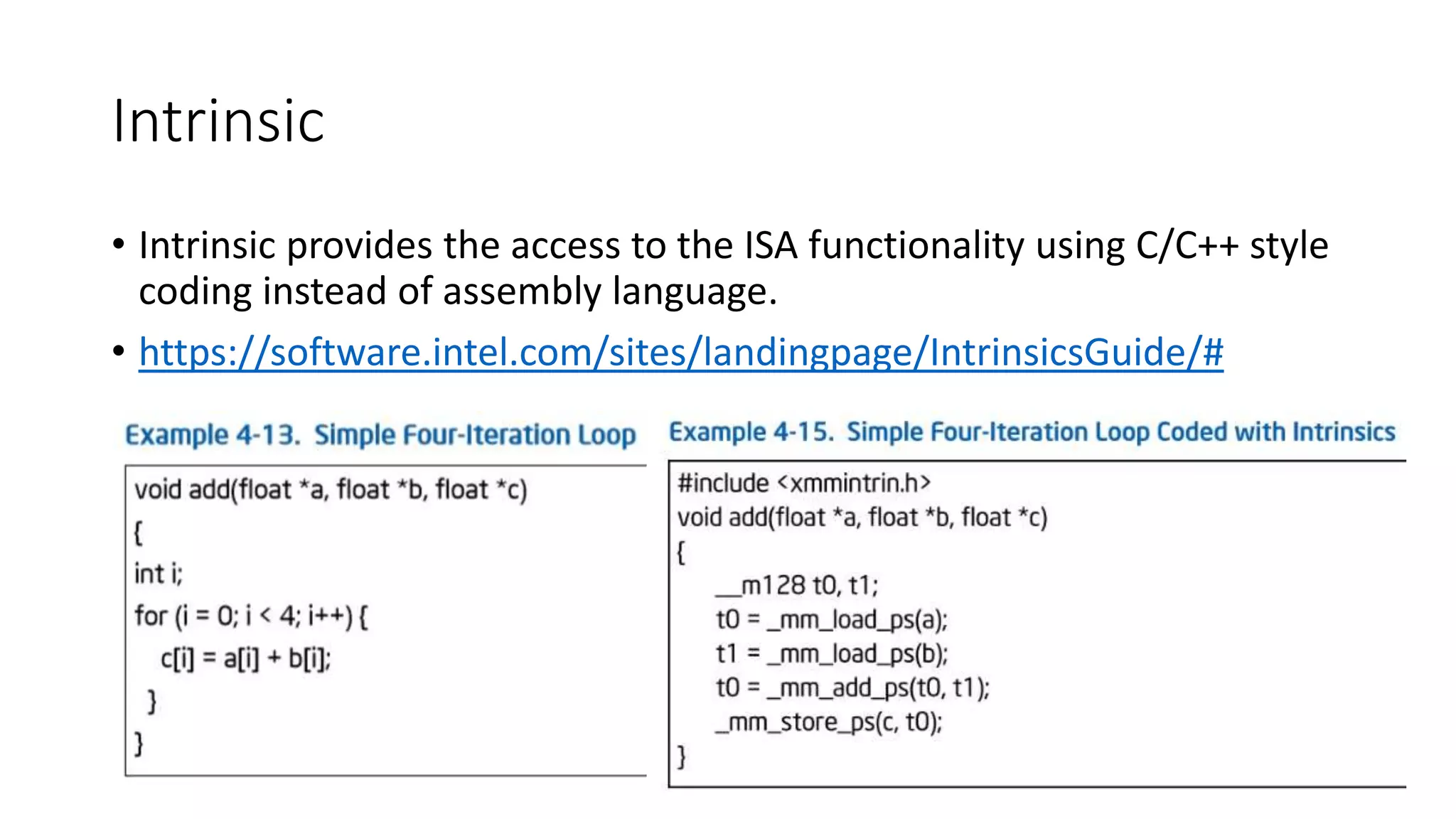

This document discusses streaming SIMD extensions (SSE) and how to use SIMD instructions to boost program performance. It defines SSE as a set of CPU instructions for applications like signal processing that use single instruction, multiple data (SIMD) parallelism. The document outlines what SSE is, the advantages of SIMD, how to identify if an application can benefit from SSE, different SSE versions, coding methods like assembly and intrinsics, and references for further information.