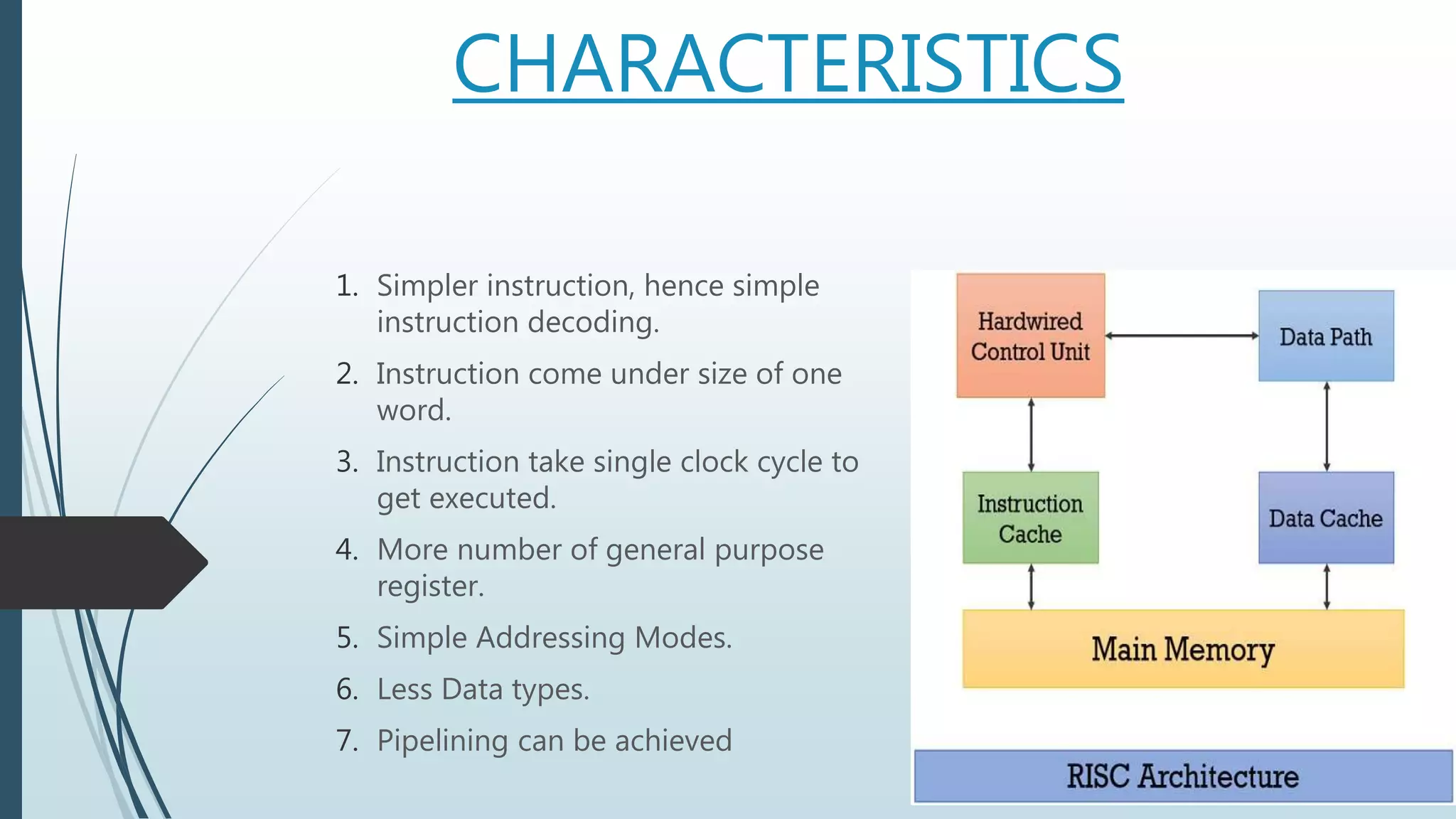

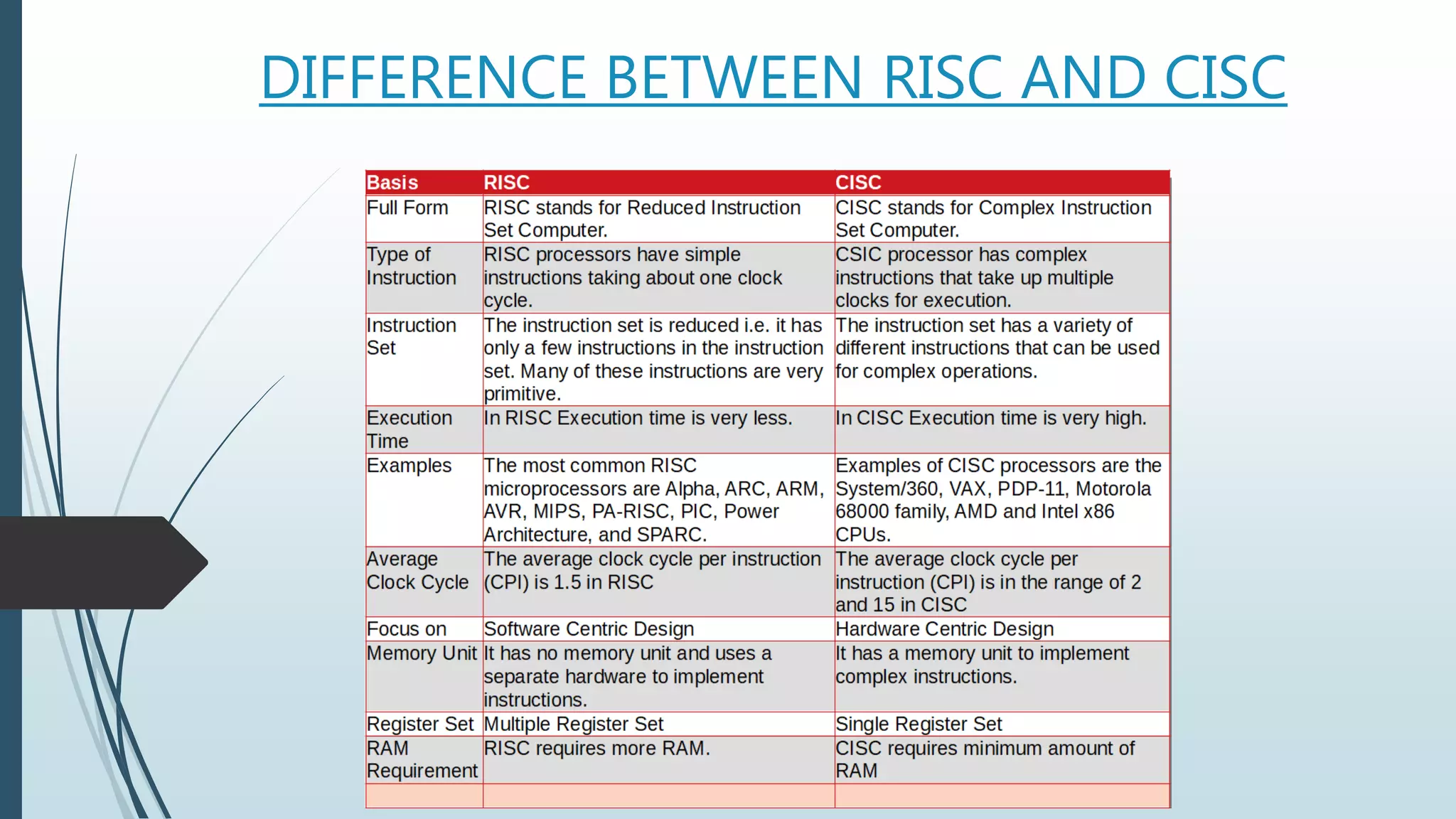

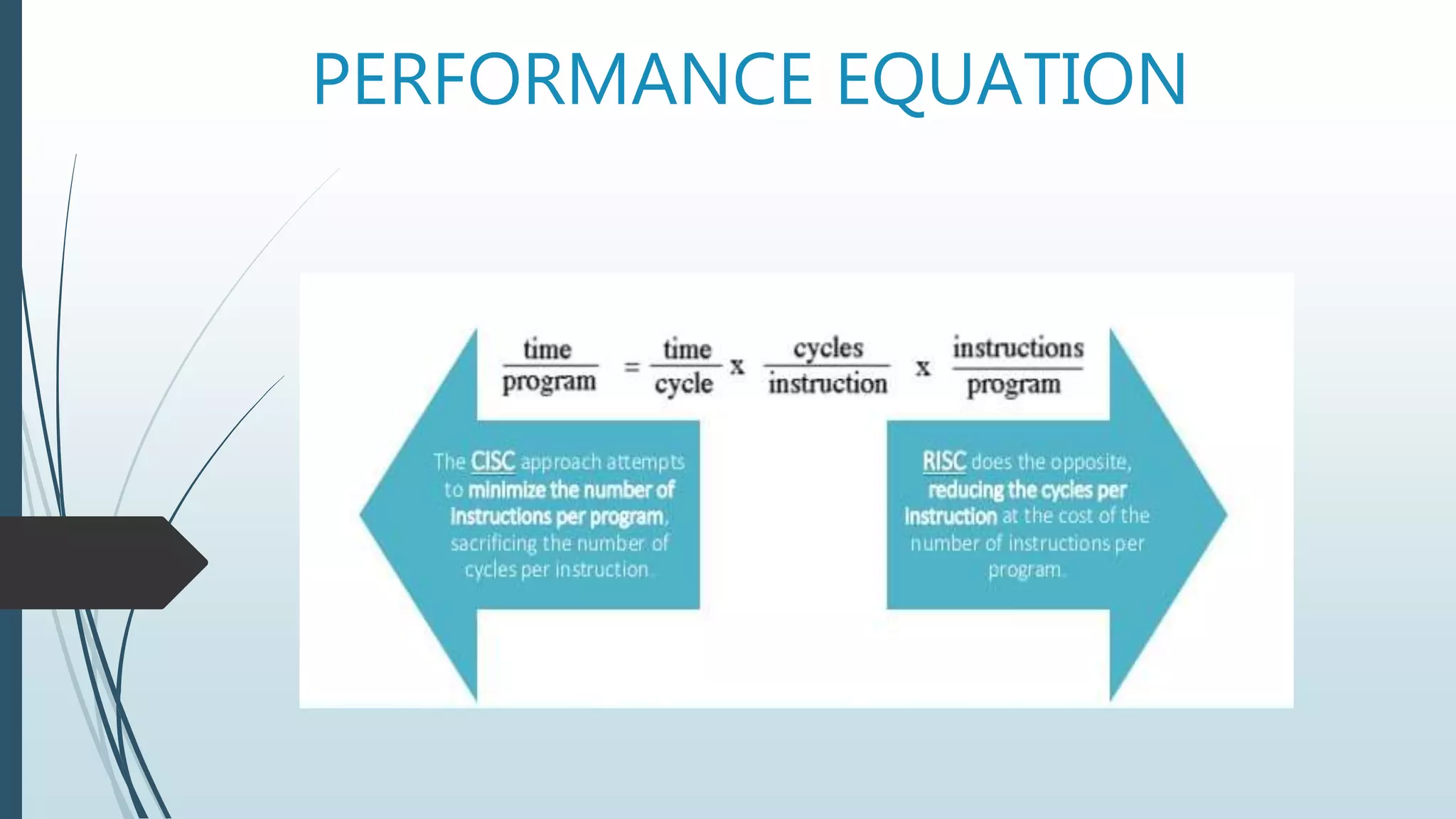

This document discusses RISC (Reduced Instruction Set Computer) architecture. It provides a brief history of early RISC projects from IBM, Stanford, and UC-Berkeley in the late 1970s and early 1980s. Key characteristics of RISC include simpler instructions that take a single clock cycle to execute, a large number of general purpose registers, and the use of pipelining to allow simultaneous execution of instruction stages. The document concludes that while RISC and CISC designs have converged over time, RISC chips still utilize uniform single-cycle instructions and have a register-to-register load/store architecture with many general purpose registers.