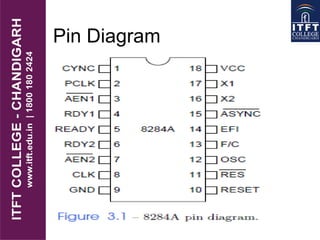

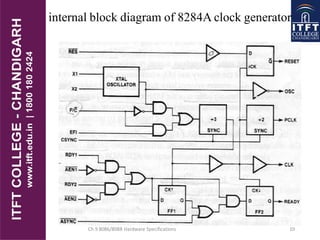

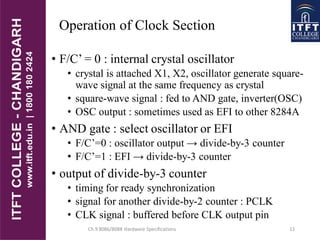

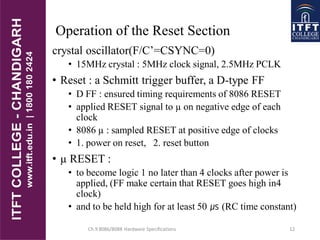

The 8284 is an integrated circuit clock generator designed specifically for use with the 8086/8088 microprocessors. It provides clock signals and synchronization that are required by these processors. The 8284 contains oscillators that generate the clock signal from either an internal or external crystal. It also contains circuitry to synchronize ready signals and generate wait states. Pins on the device include clock outputs, ready inputs, and a reset output to interface with the microprocessor.