This document discusses the evolution of computer architecture from CISC to RISC designs. It covers major advances like cache memory and microprocessors that enabled RISC. Key RISC features include large register files optimized via register allocation algorithms, simple instruction sets, and emphasis on optimizing instruction pipelines. Pipelining enables parallel fetch and execute cycles, and techniques like delayed branching optimize pipeline utilization. While CISC aimed to ease compiler complexity, RISC prioritizes simple instructions that can complete in one cycle. The tradeoffs between CISC and RISC remain controversial with no definitive consensus due to the complexity of separating hardware and software factors.

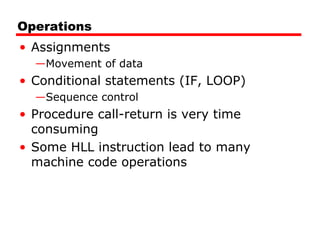

![Weighted Relative Dynamic Frequency of HLL

Operations [PATT82a]

Dynamic Occurrence

Machine-Instruction

Weighted

Memory-Reference

Weighted

Pascal C Pascal C Pascal C

ASSIGN 45% 38% 13% 13% 14% 15%

LOOP 5% 3% 42% 32% 33% 26%

CALL 15% 12% 31% 33% 44% 45%

IF 29% 43% 11% 21% 7% 13%

GOTO — 3% — — — —

OTHER 6% 1% 3% 1% 2% 1%](https://image.slidesharecdn.com/13risc-170412105116/85/13-risc-10-320.jpg)