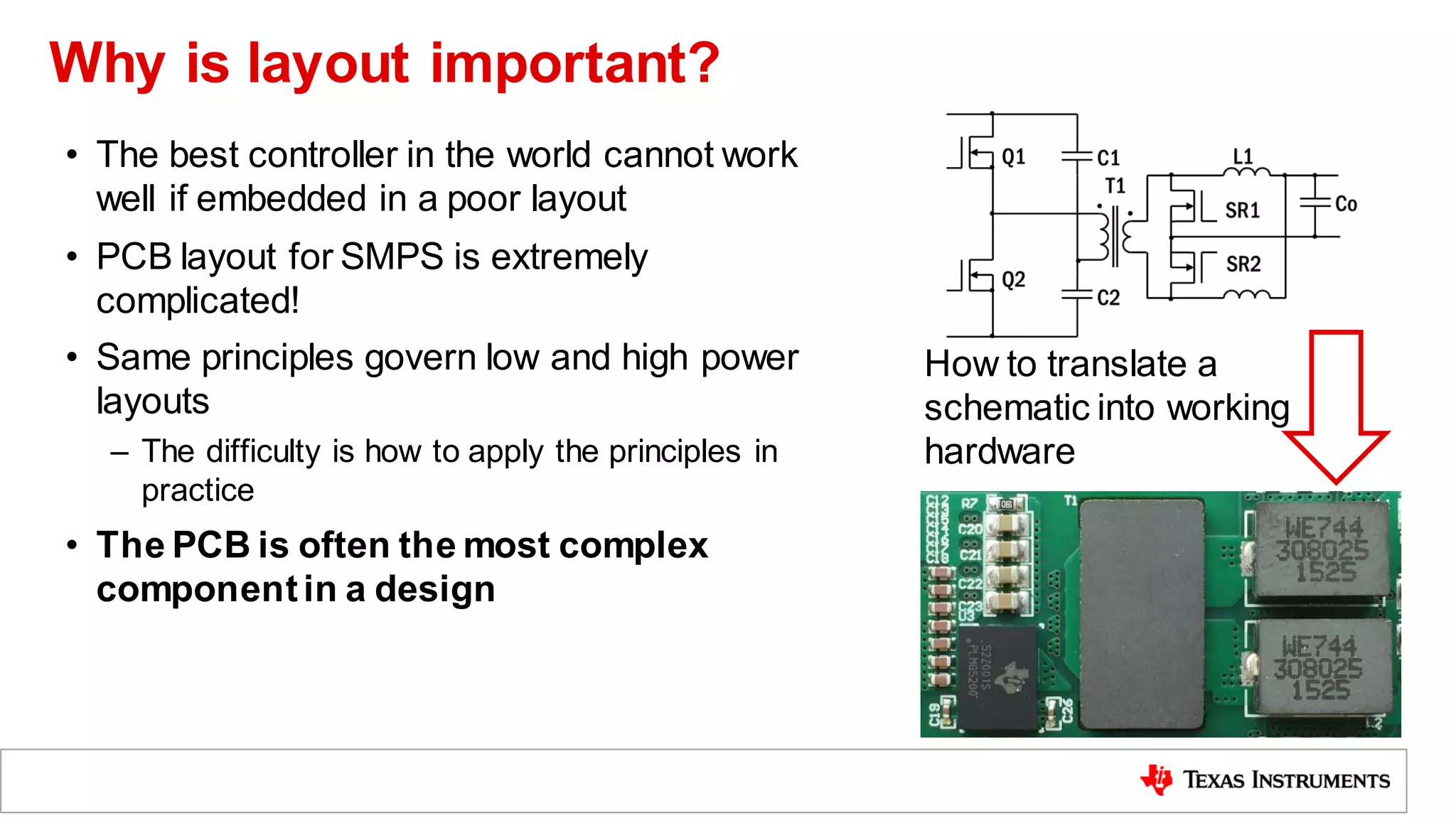

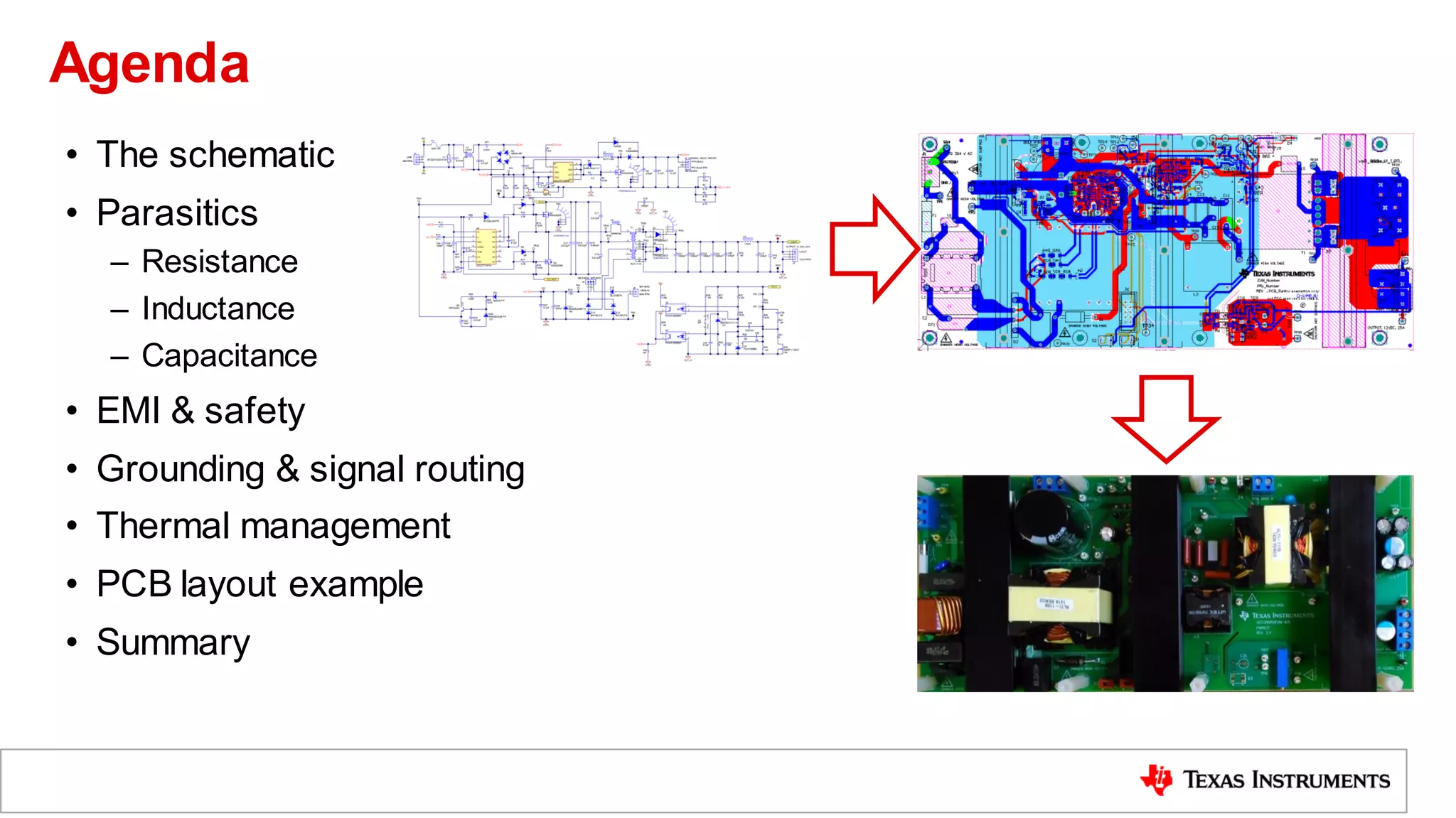

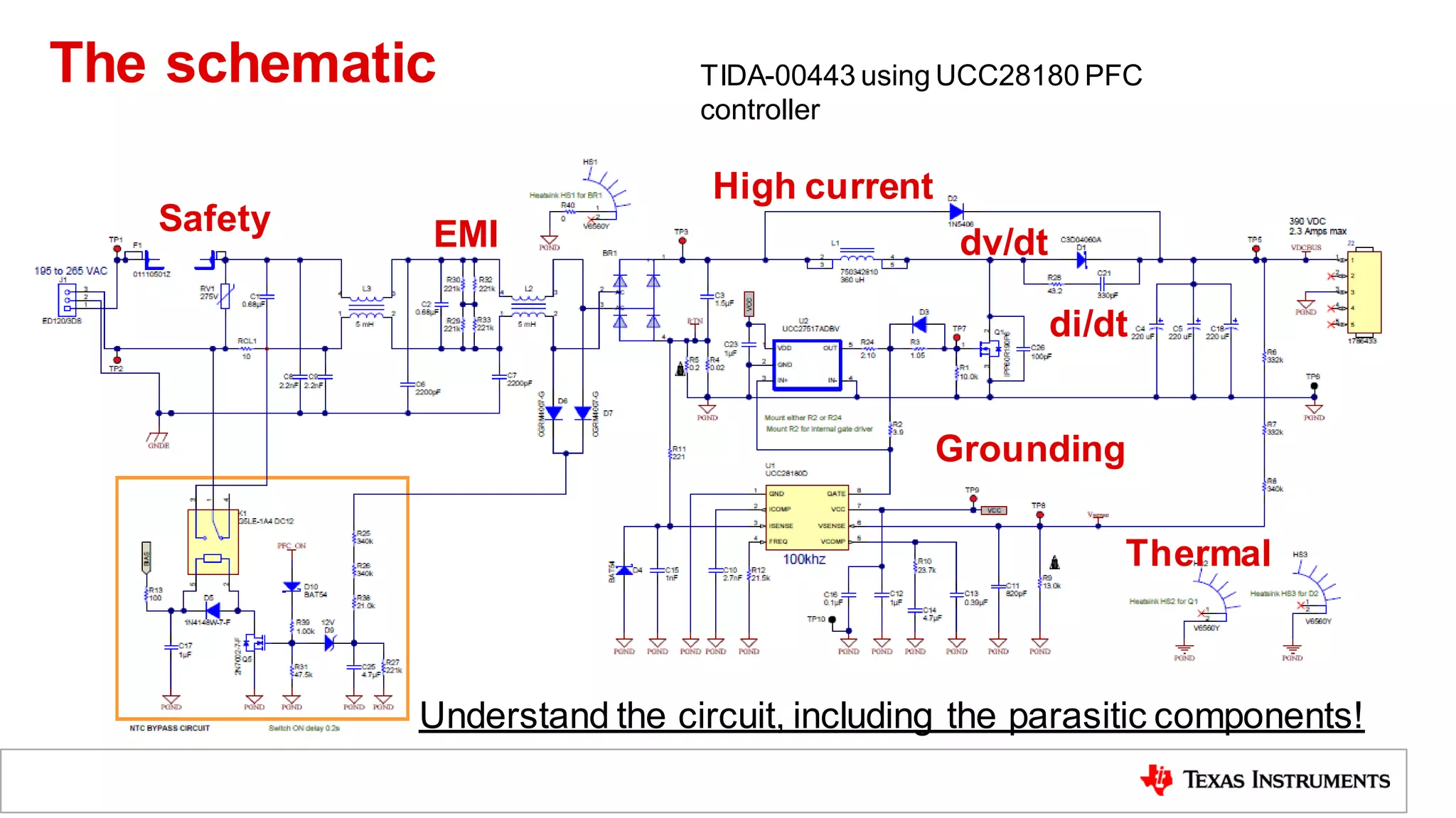

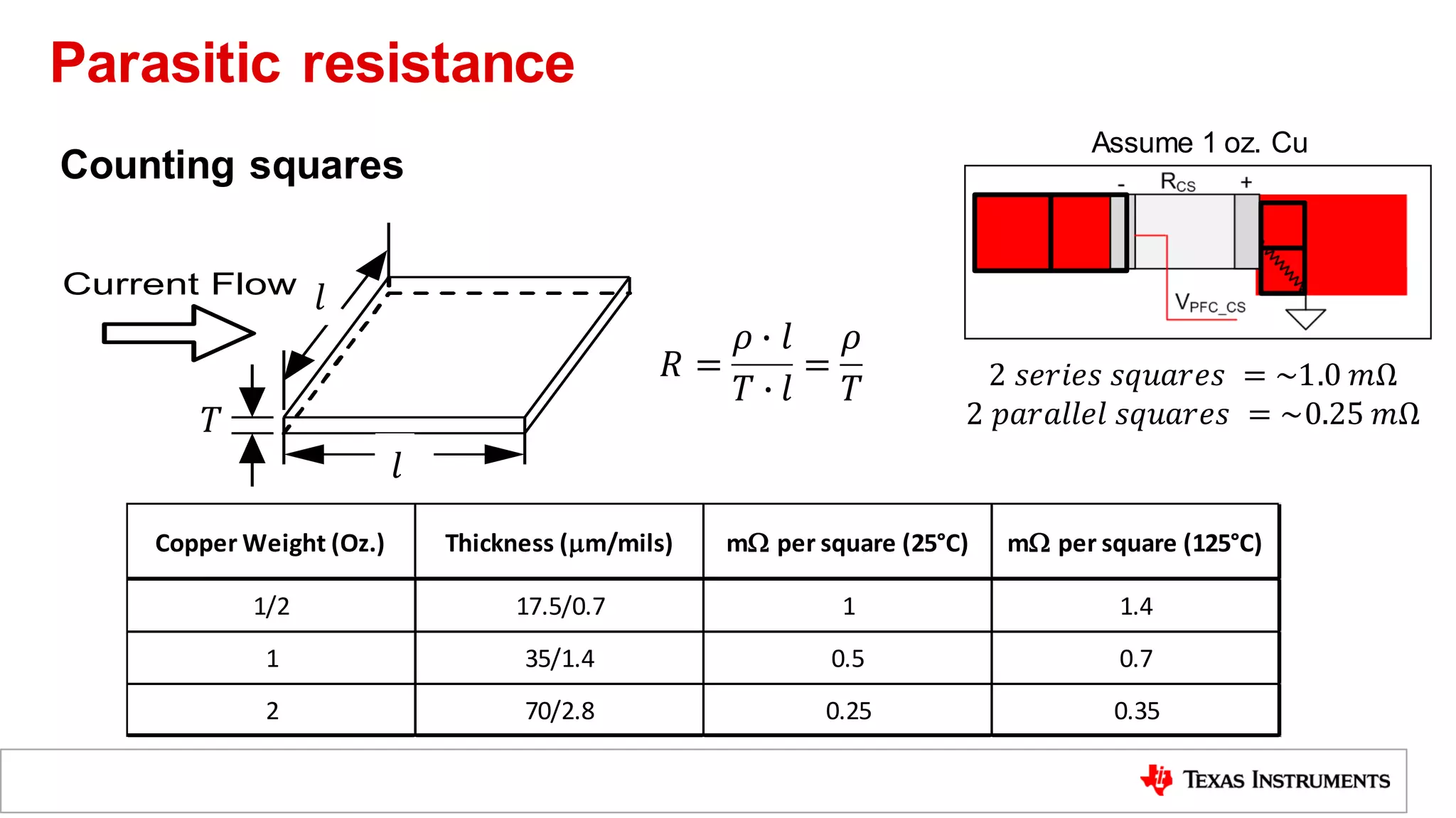

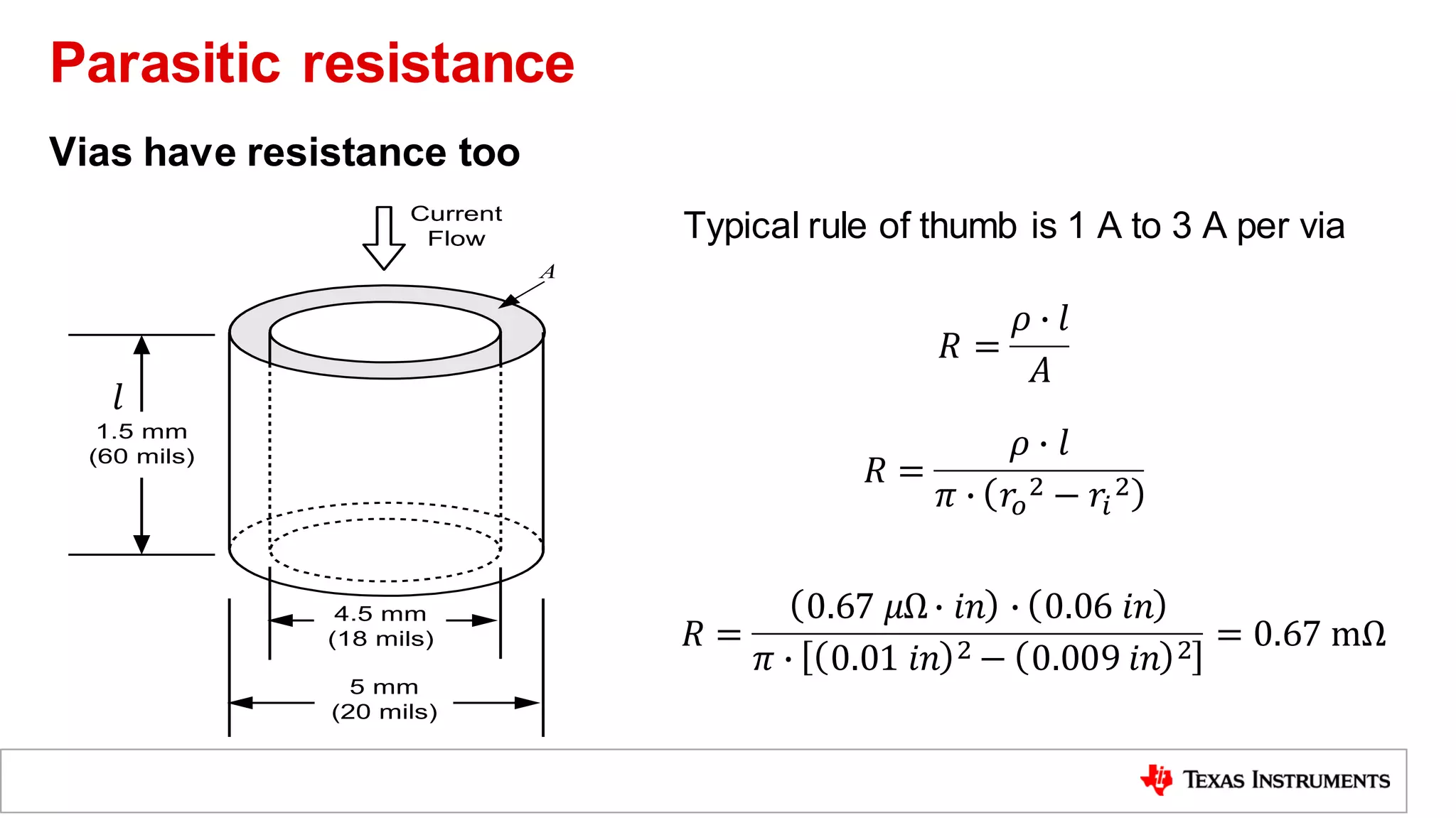

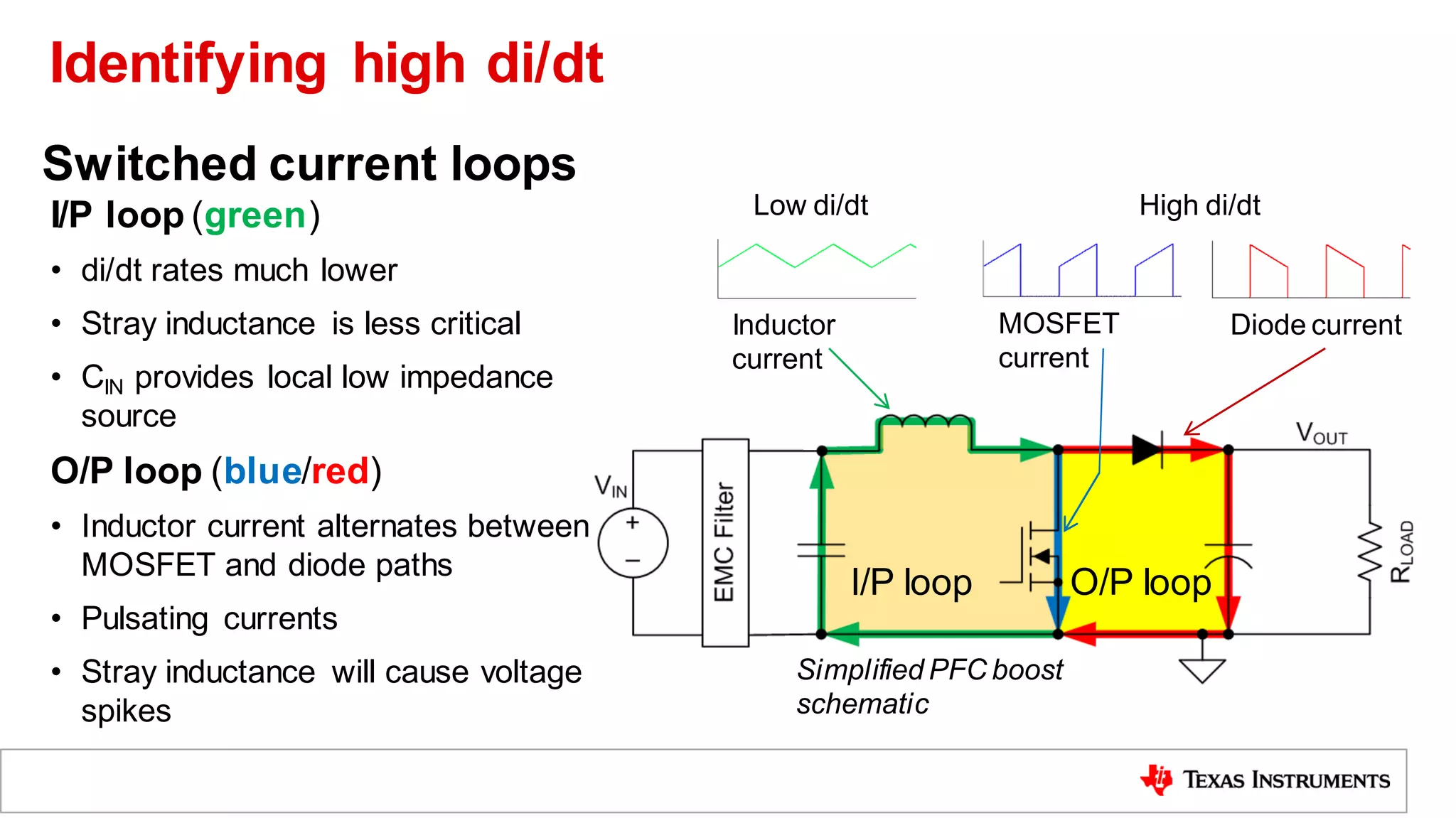

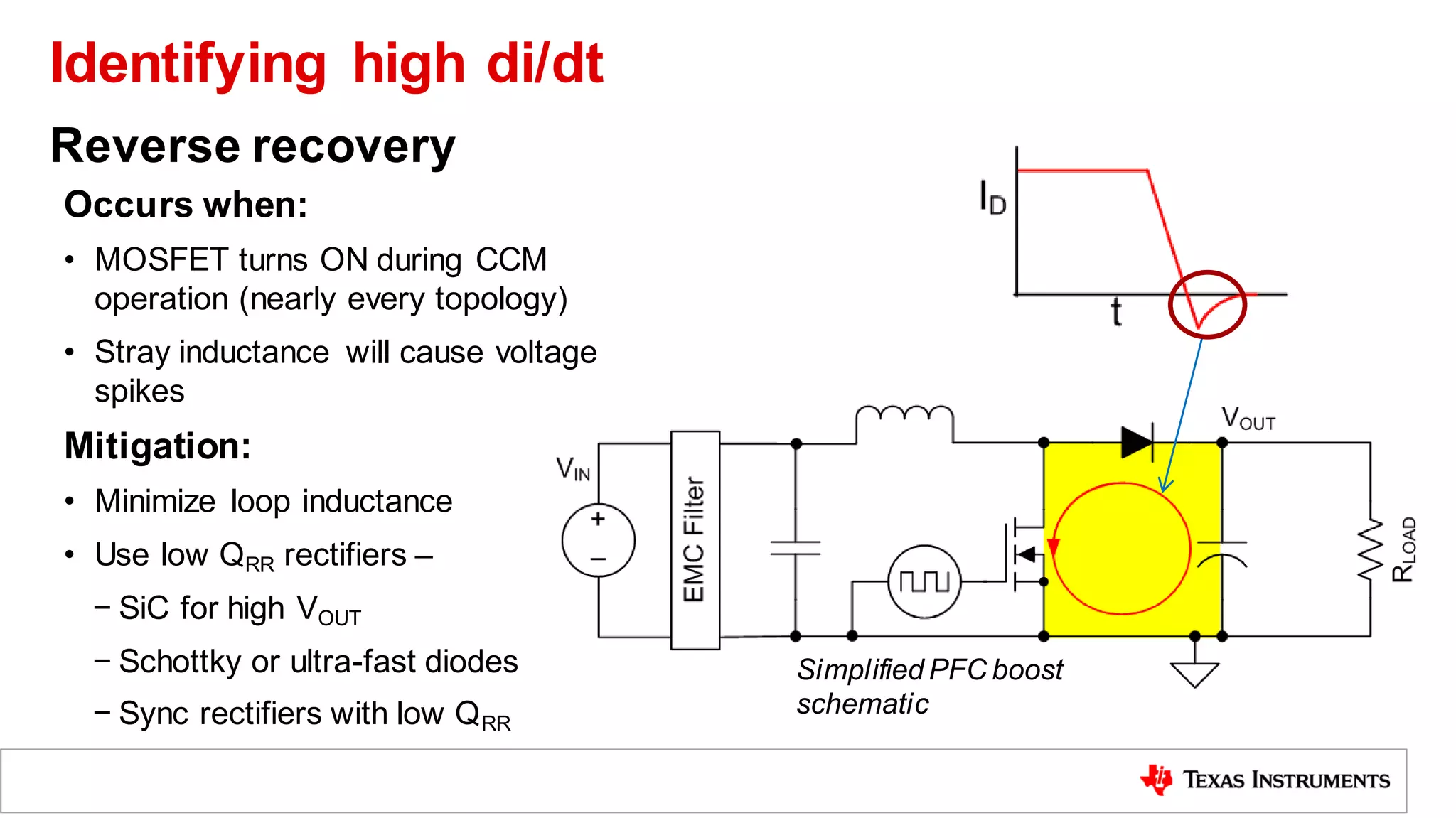

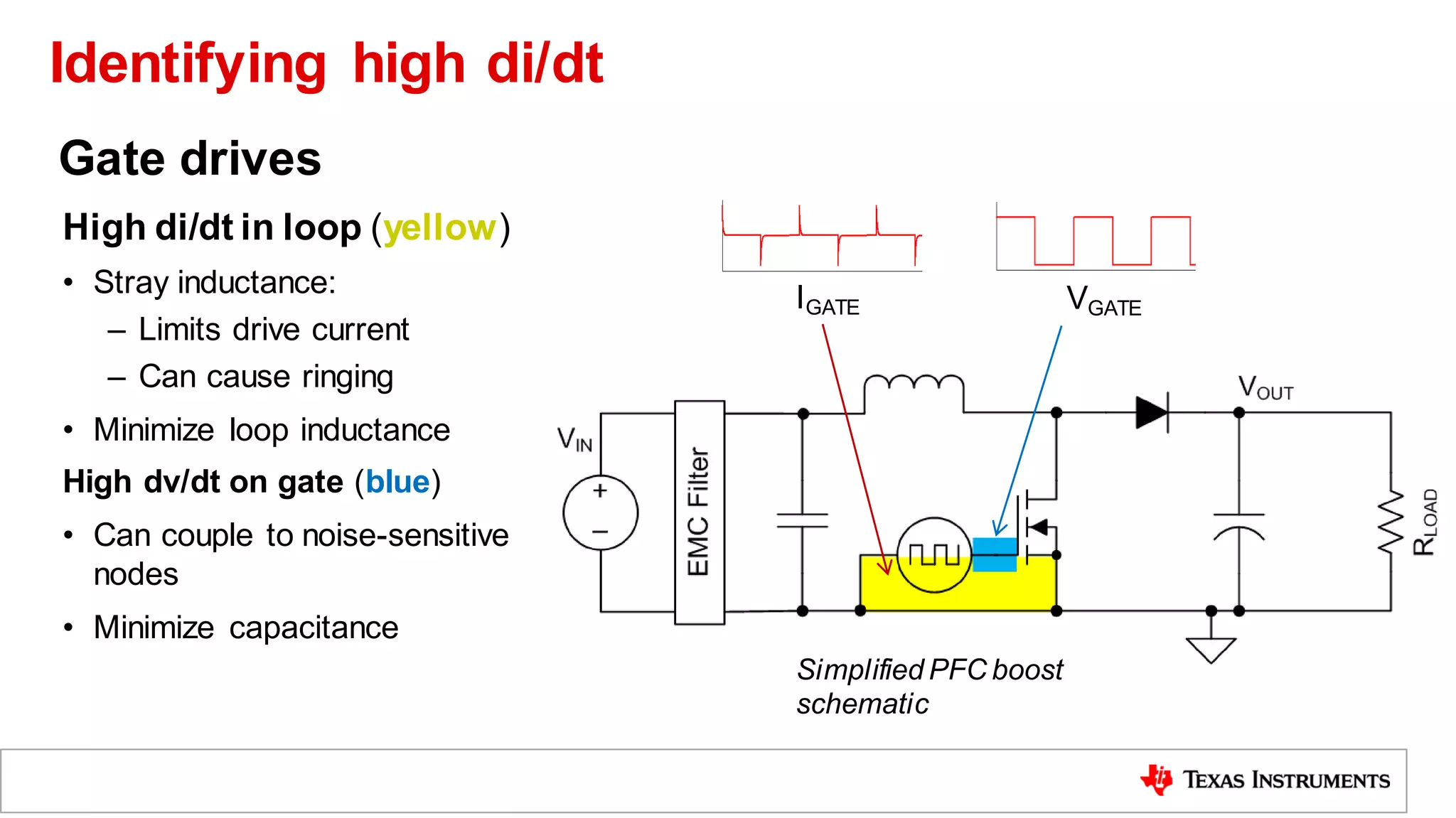

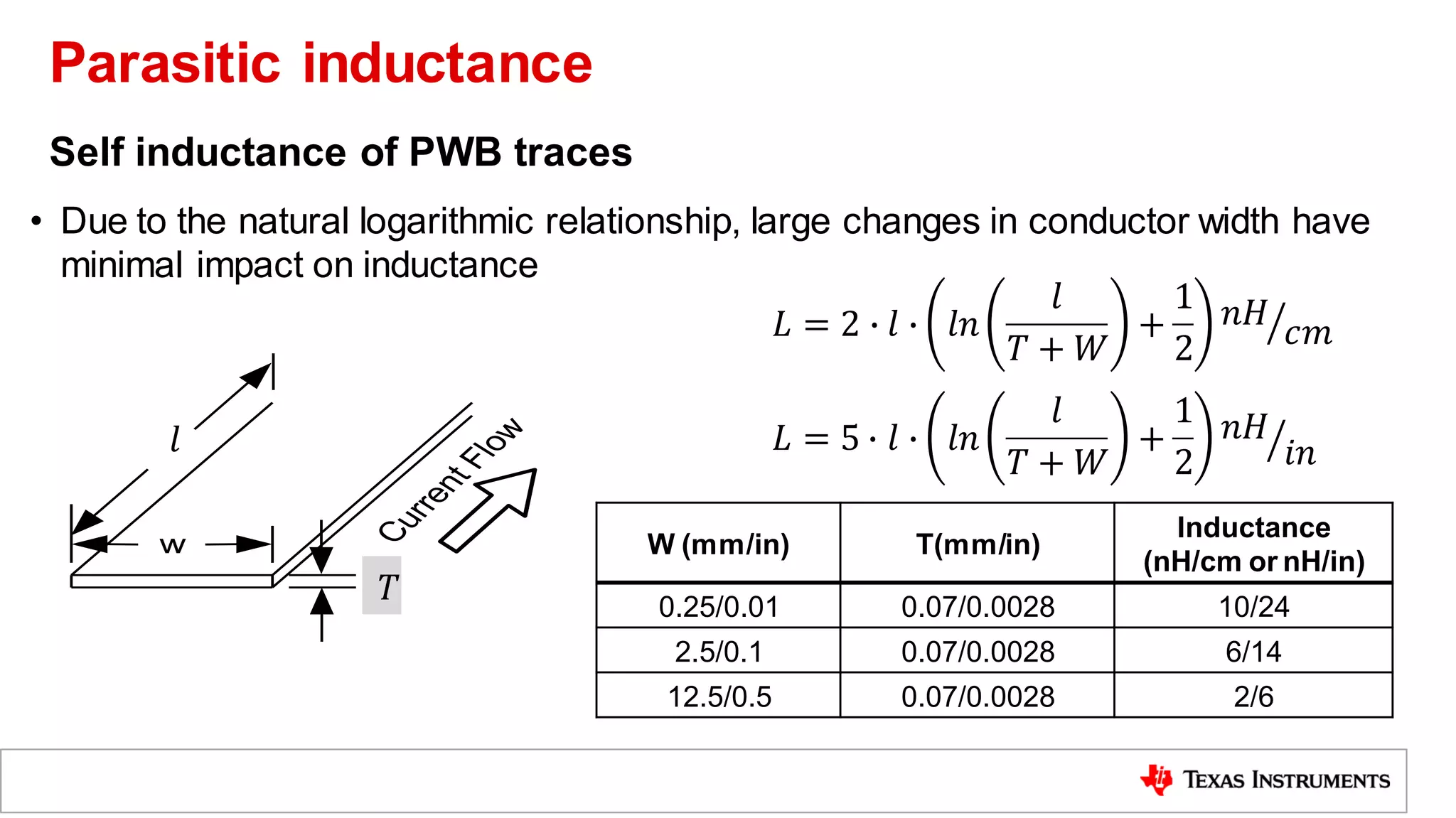

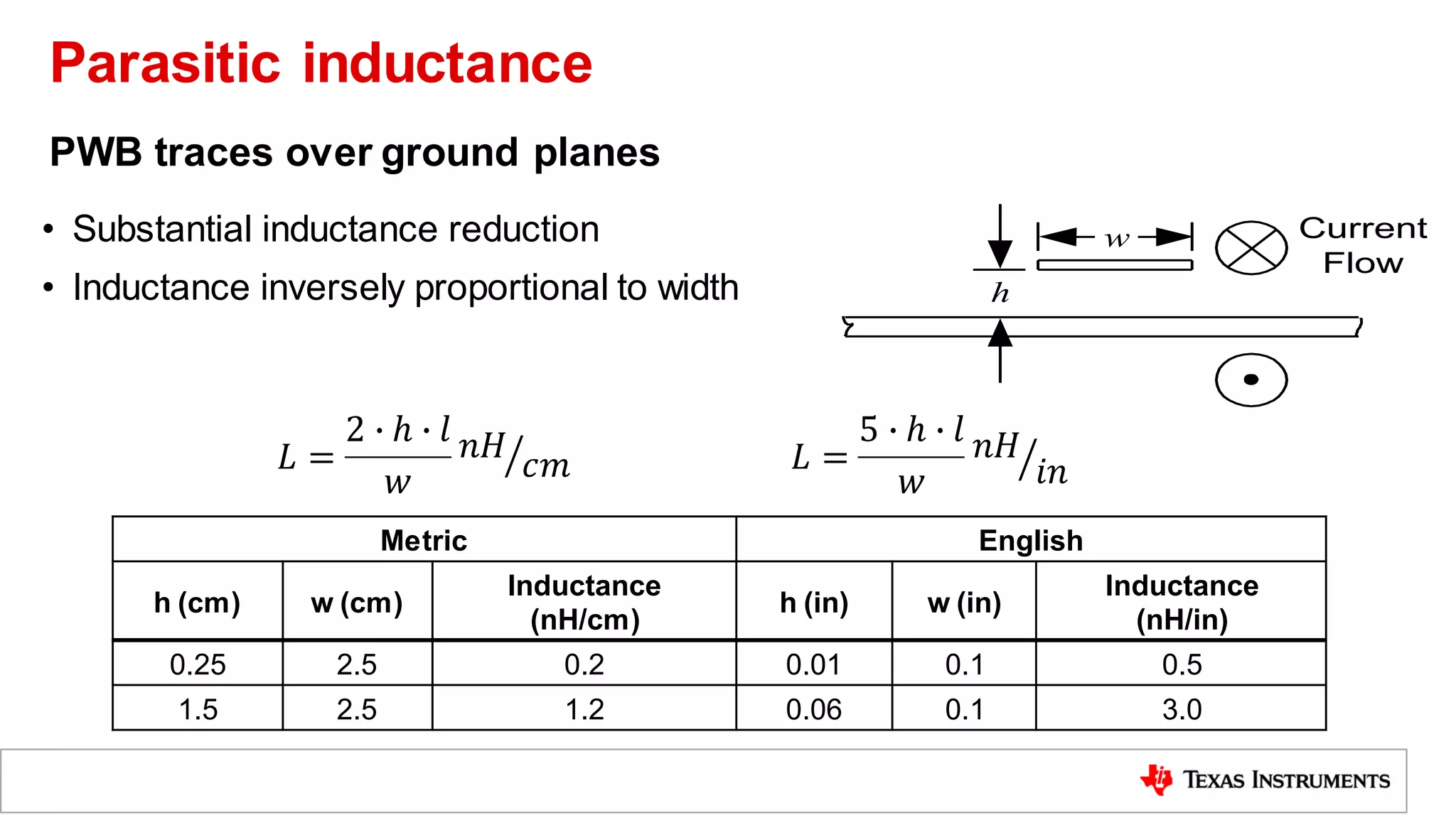

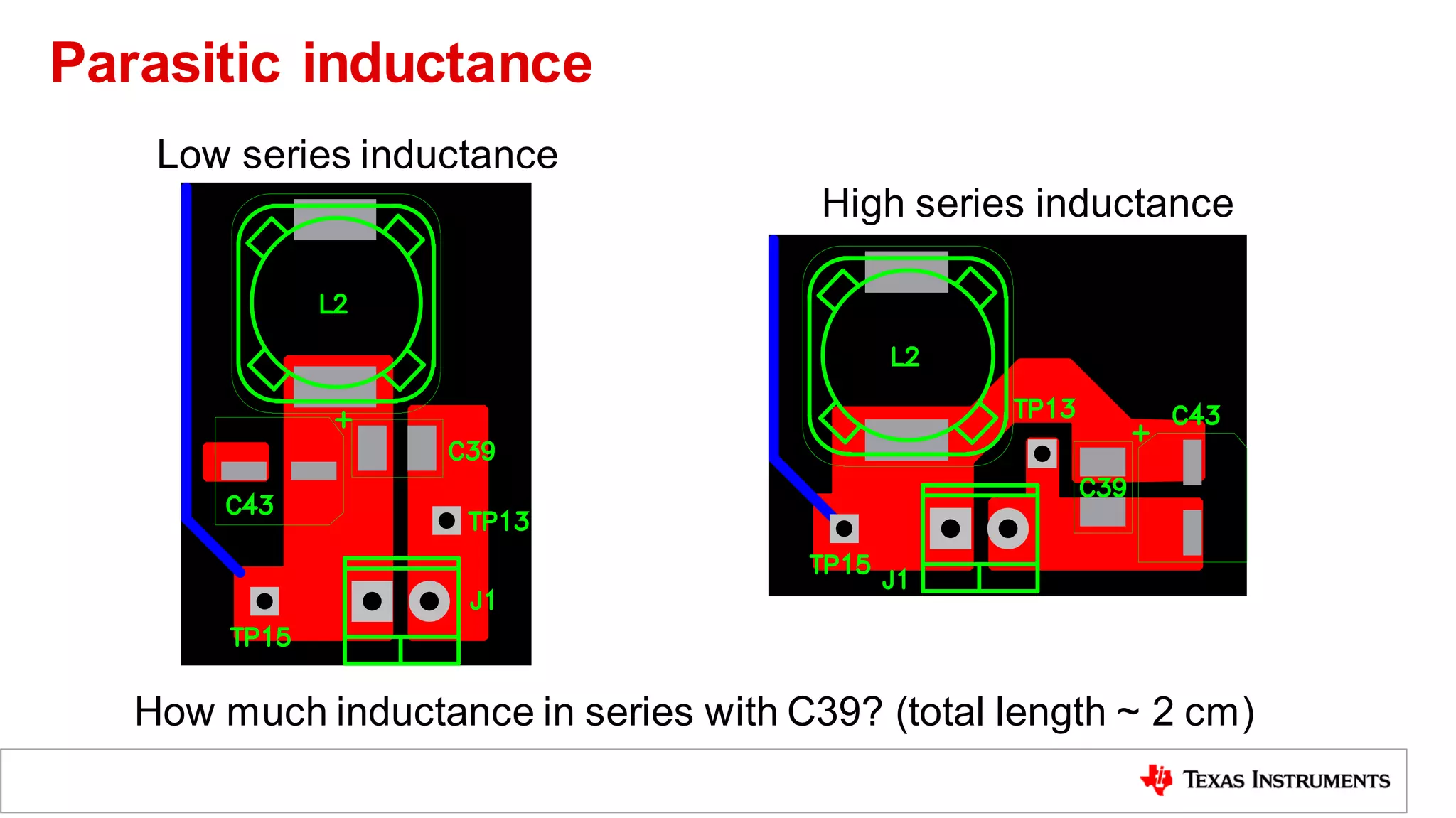

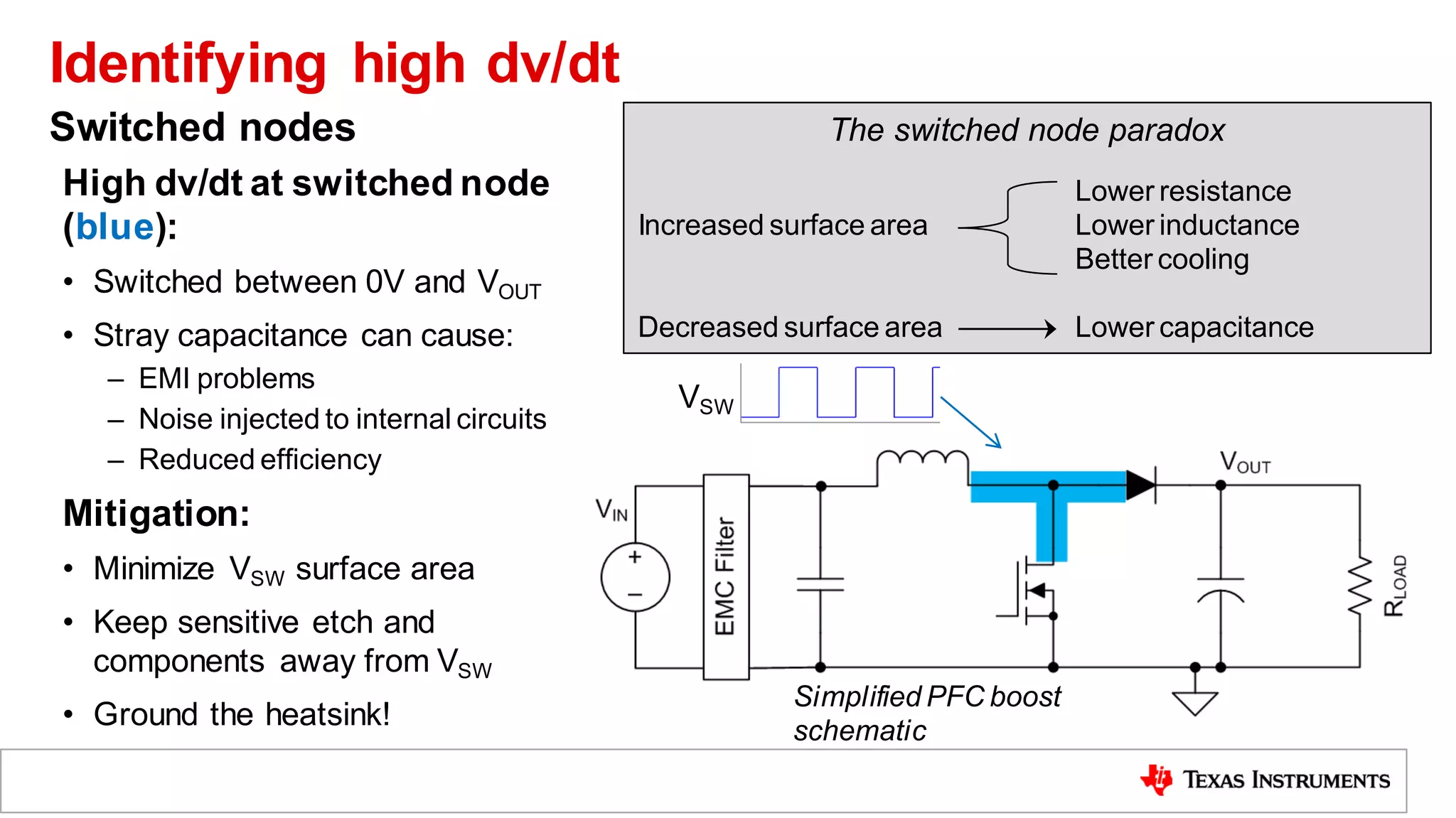

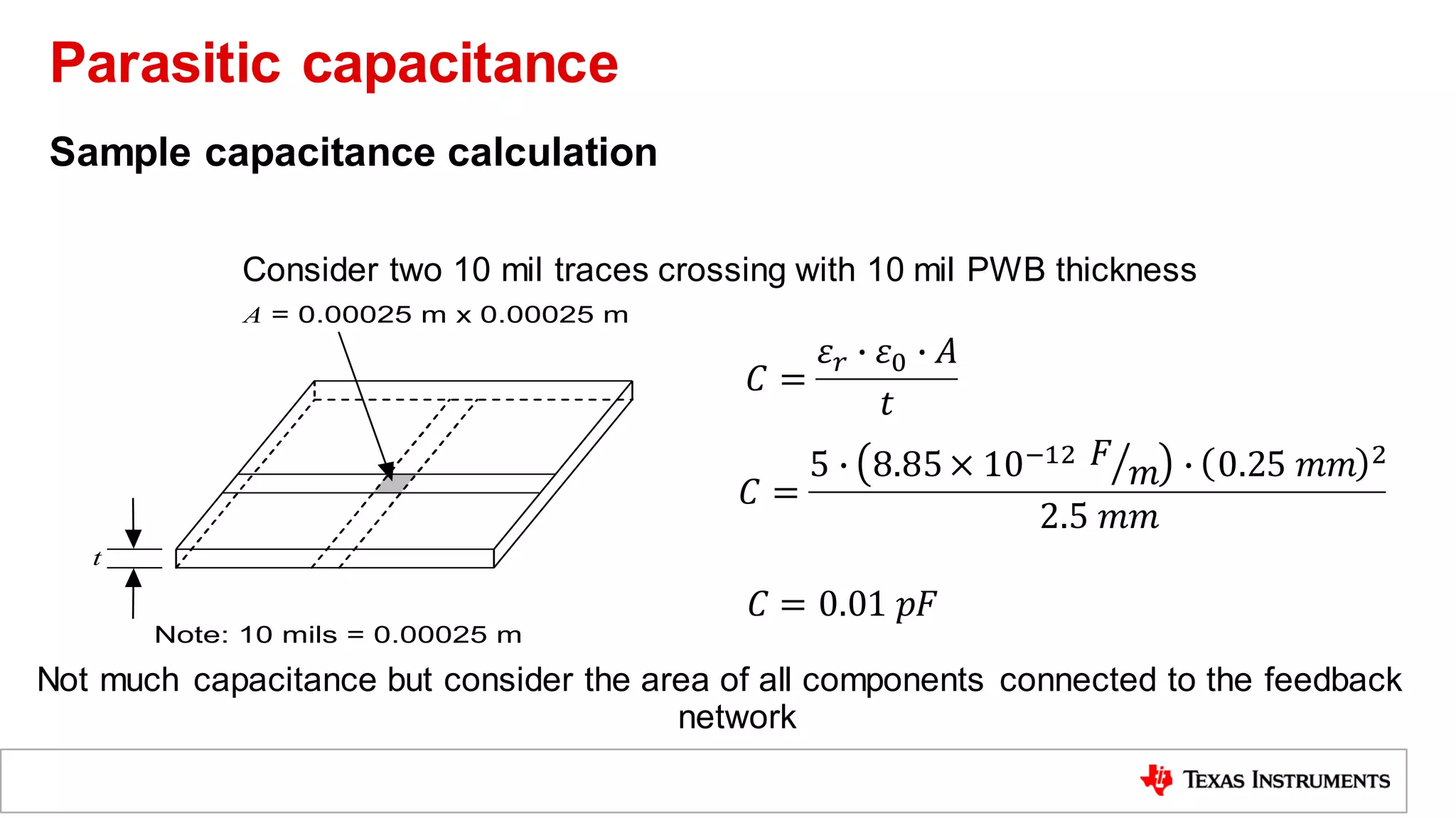

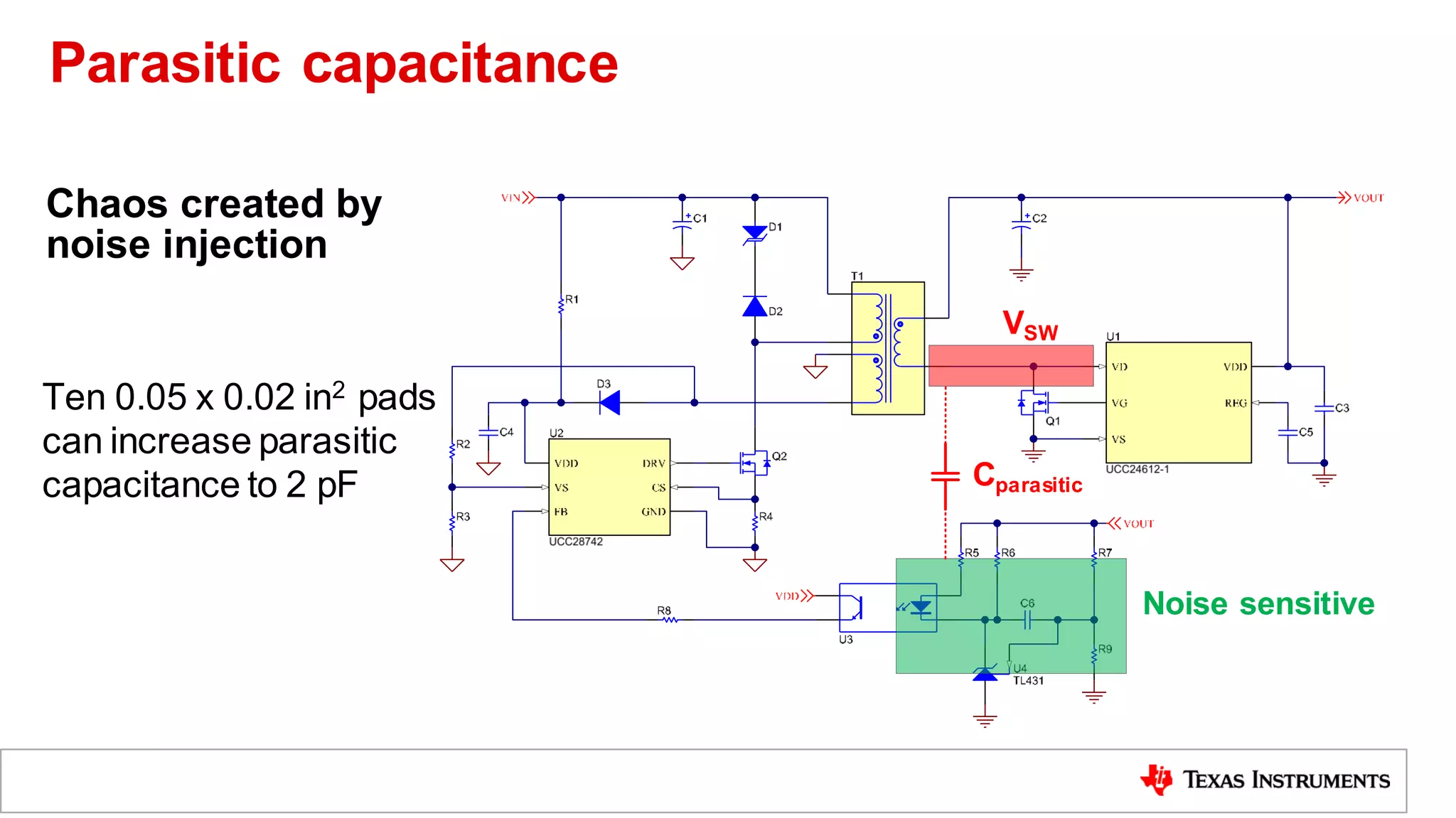

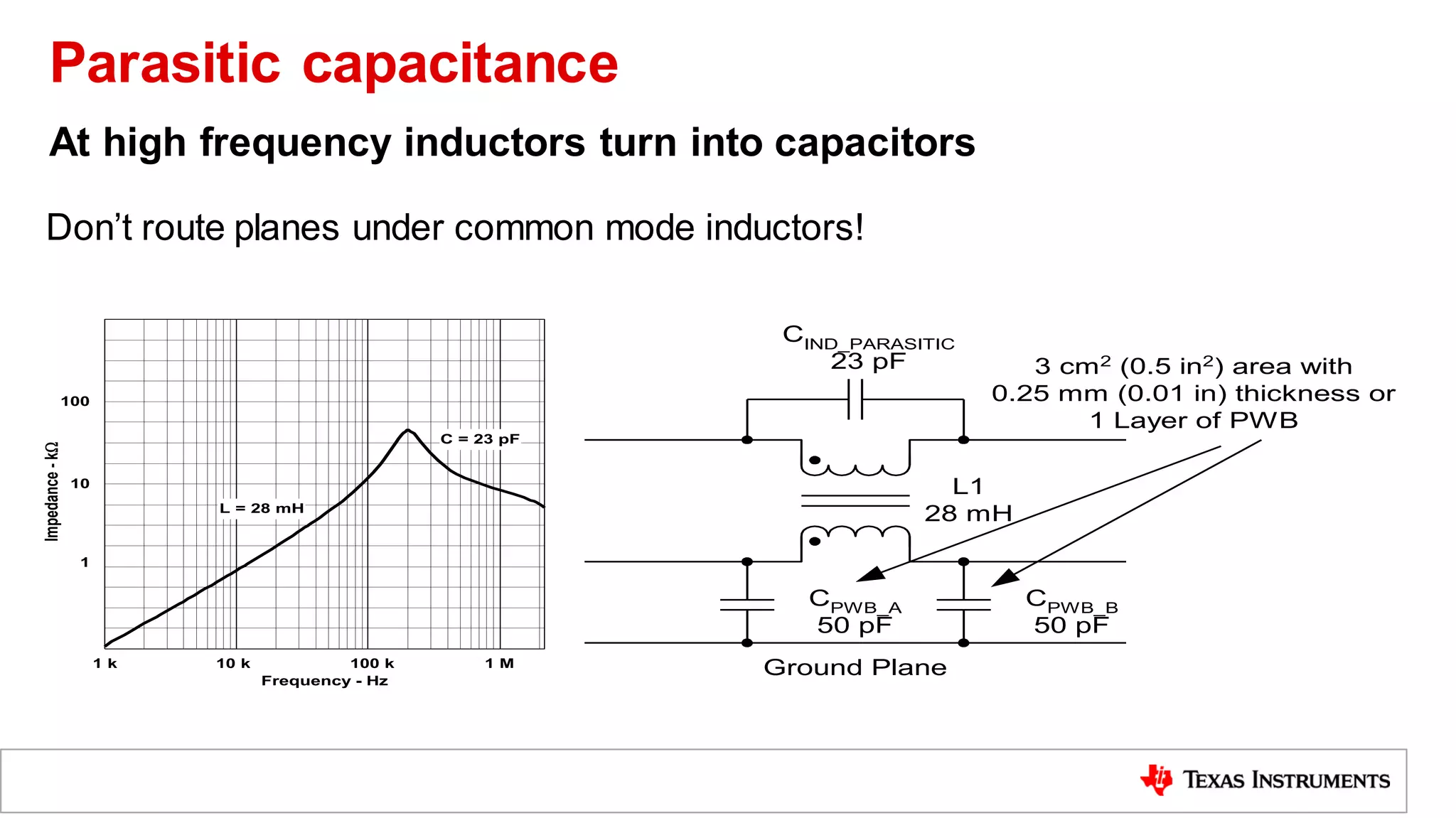

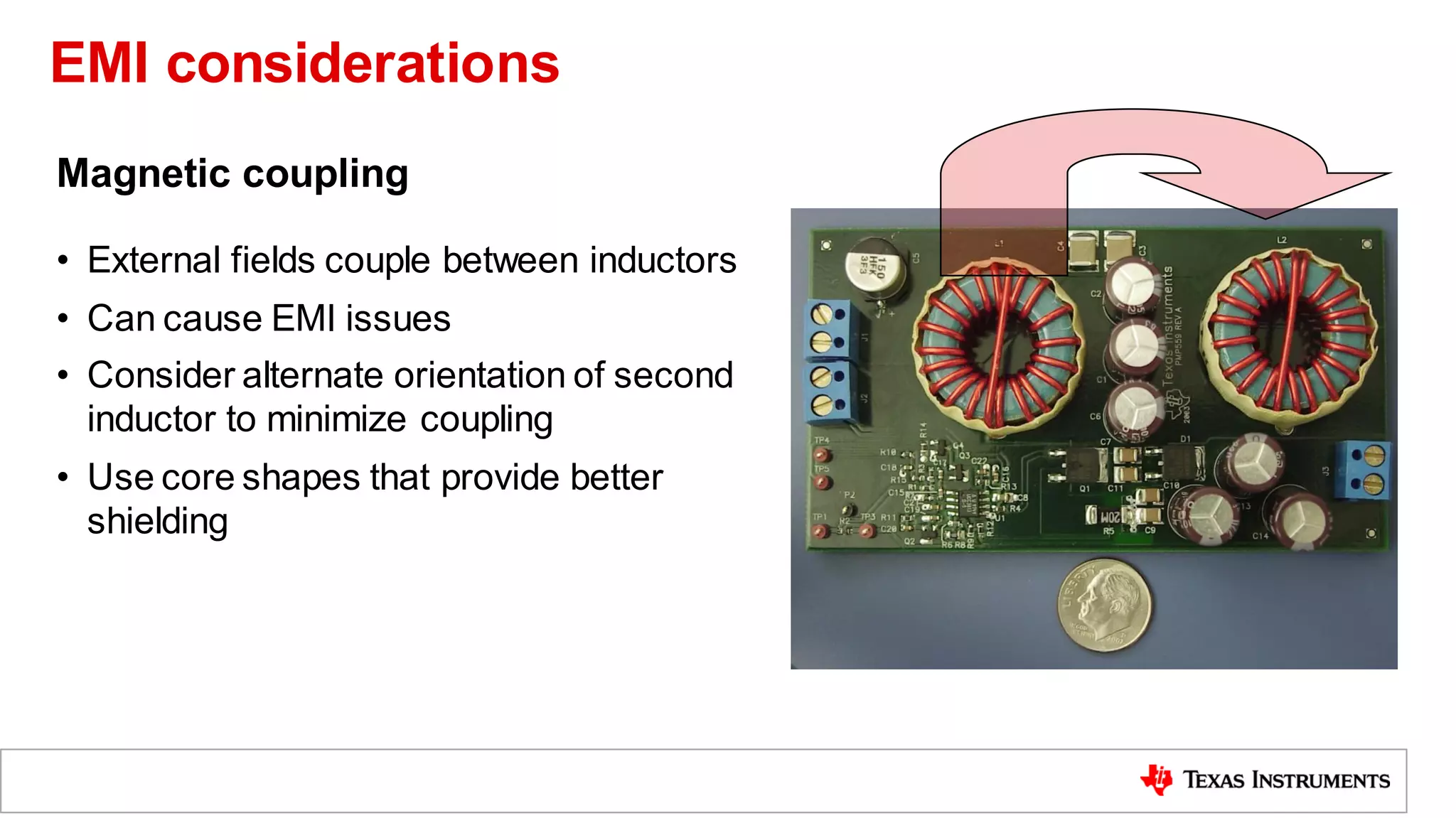

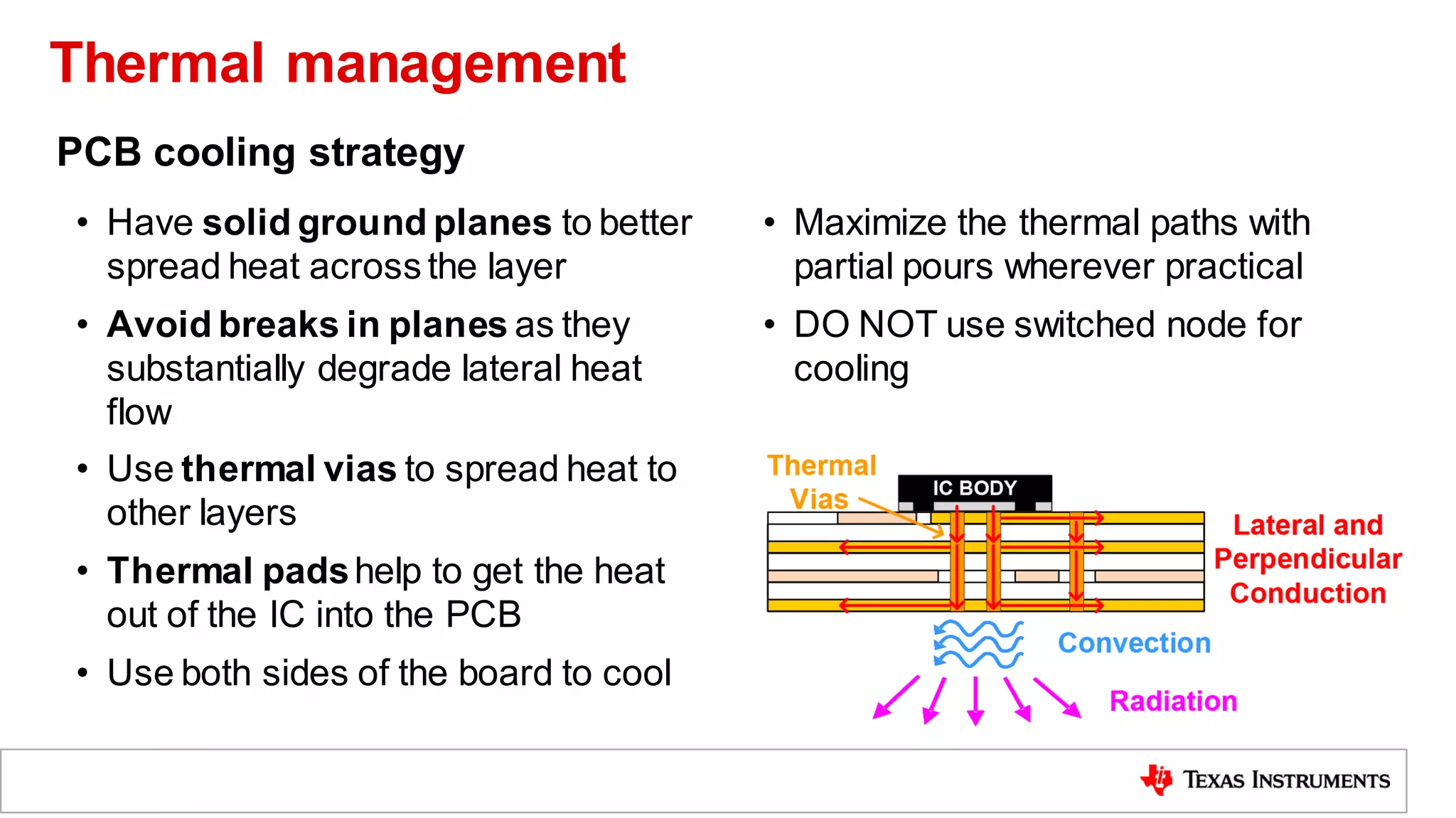

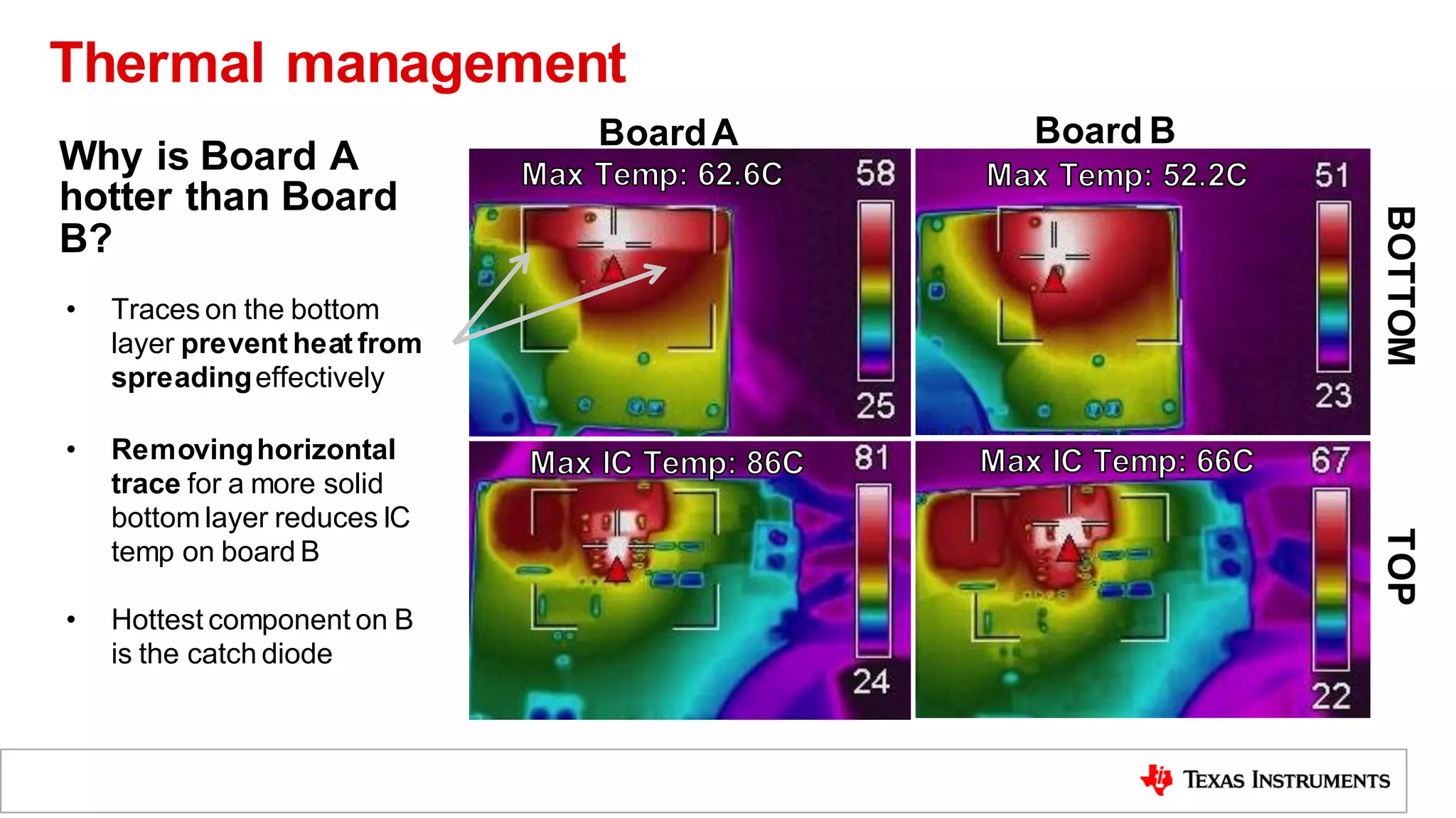

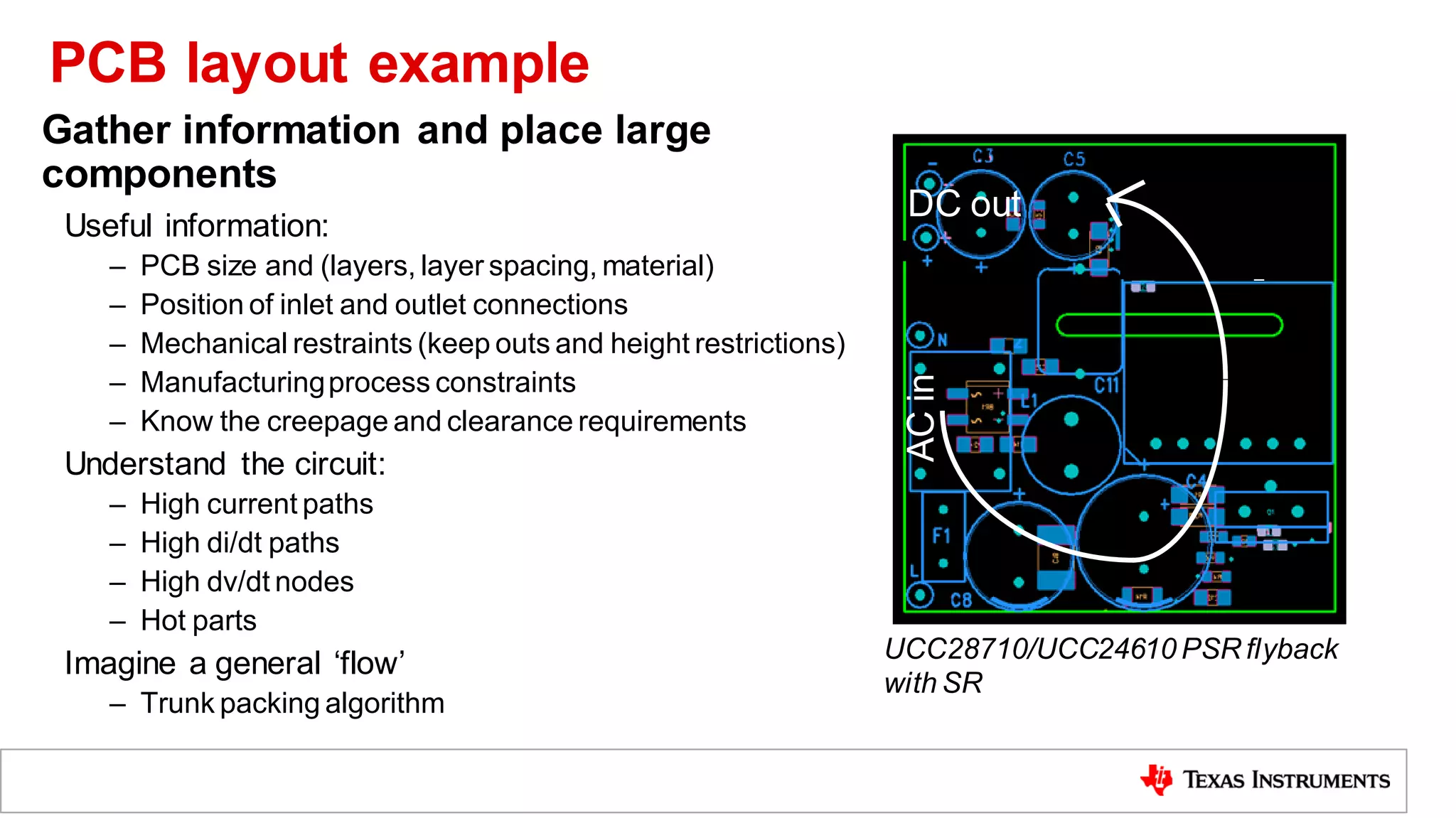

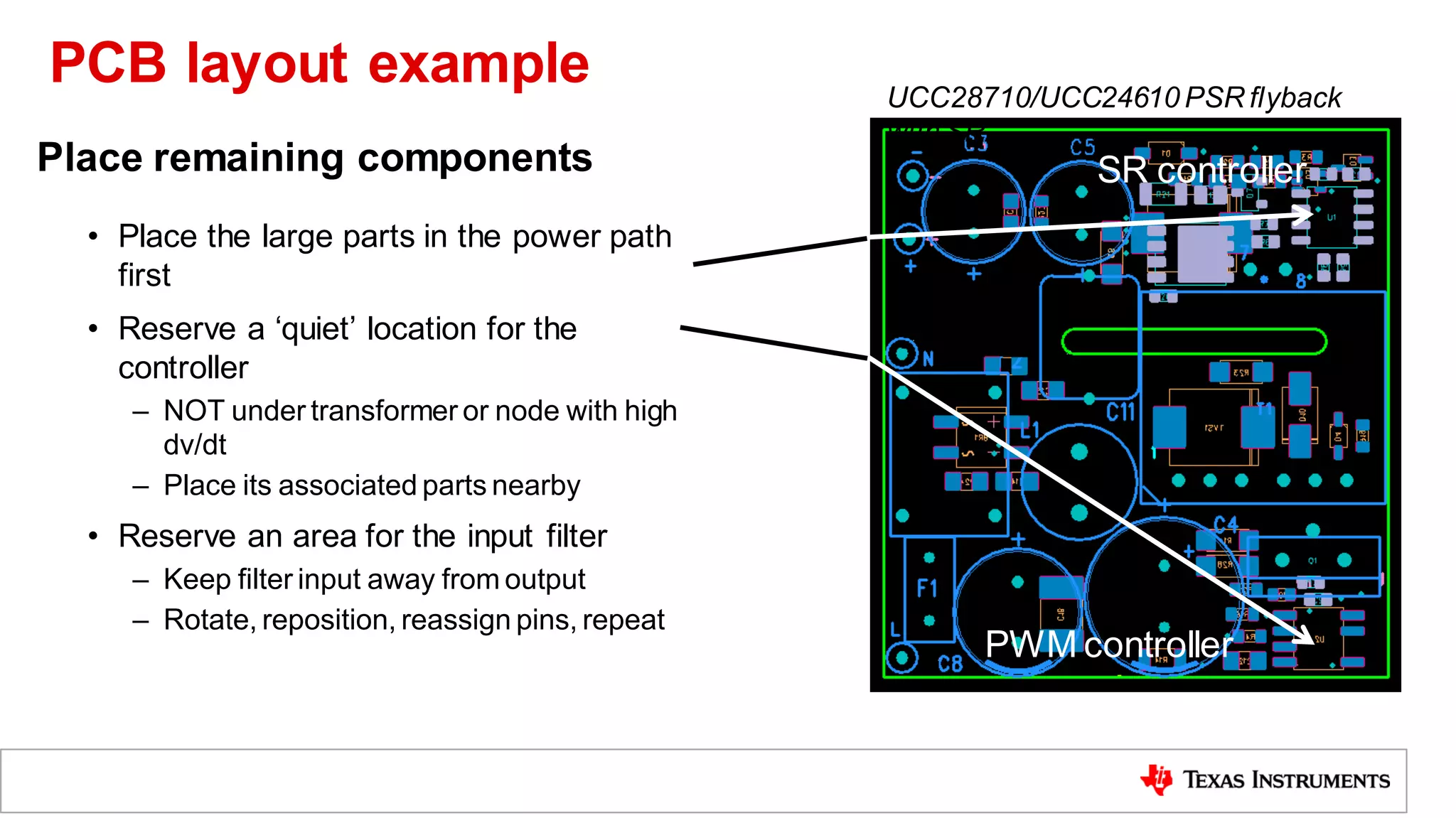

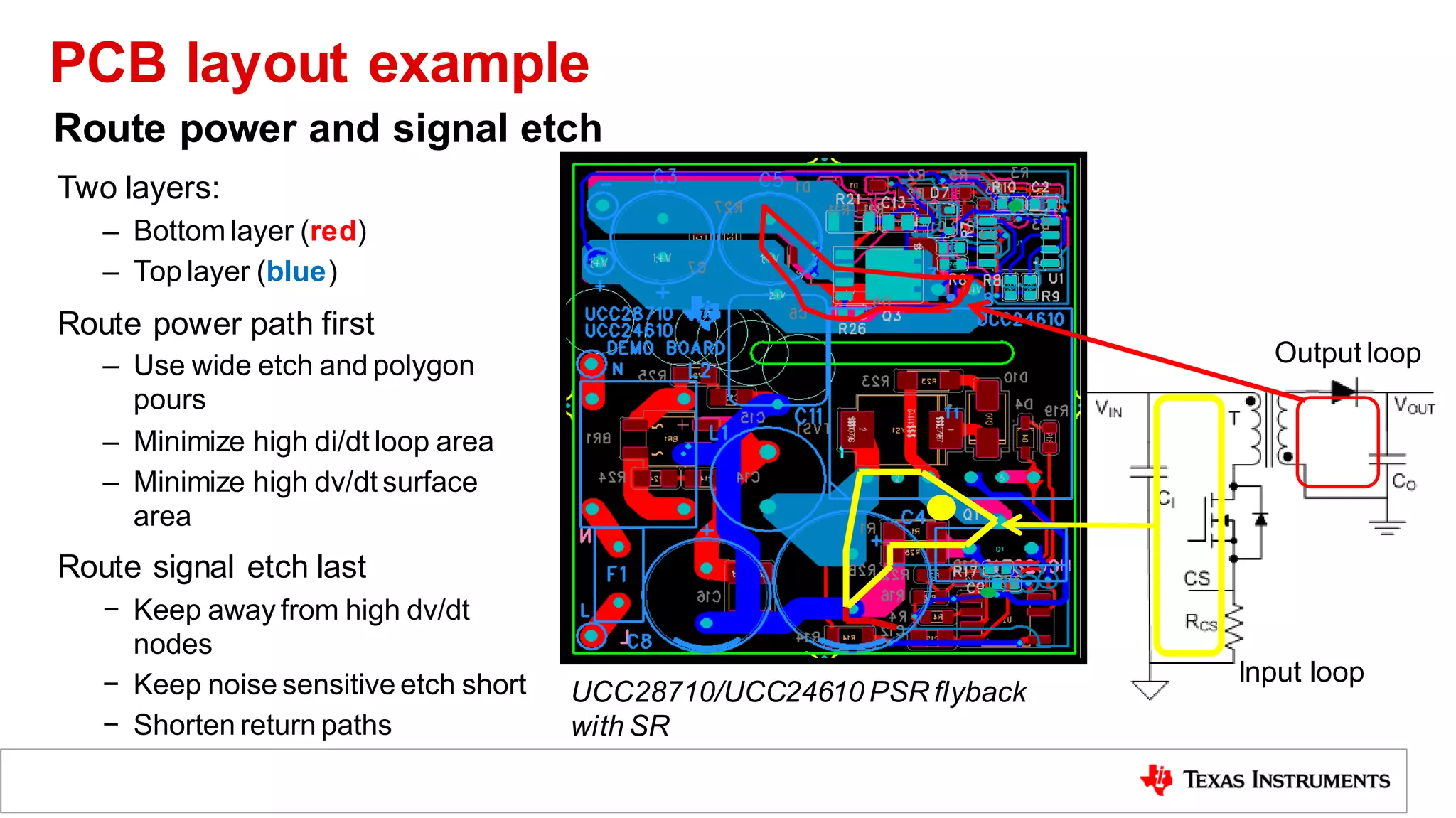

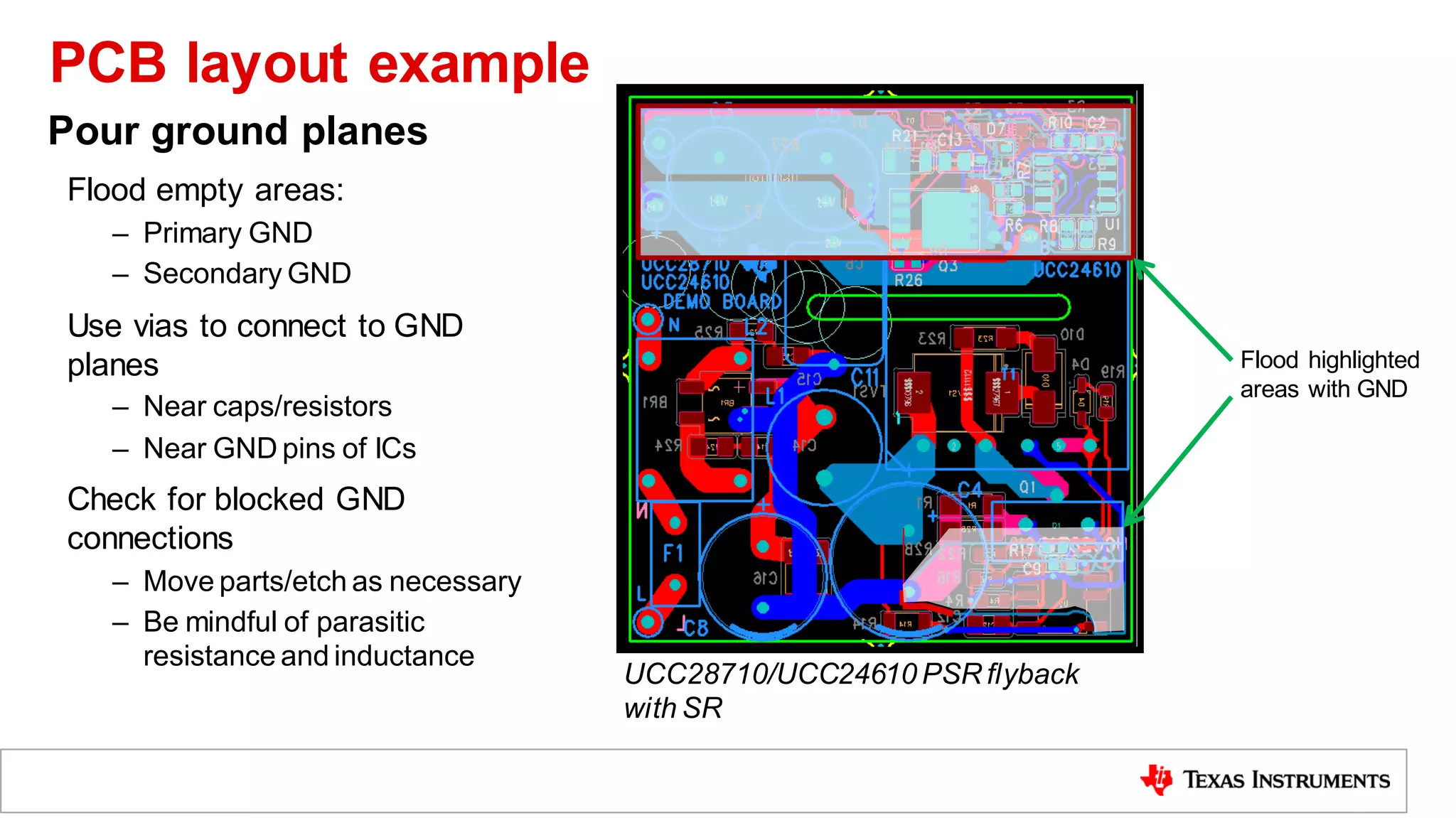

The document discusses key considerations for successfully laying out a printed circuit board for a switched-mode power supply. It covers minimizing parasitic inductance and capacitance, routing high current and high switching node paths, following EMI best practices like separating noisy and sensitive traces, implementing proper grounding techniques, and managing thermal performance. The presentation uses an example layout of a flyback converter to demonstrate these concepts in practice. It emphasizes understanding the circuit operation and identifying critical paths before systematically placing components and routing traces to achieve an optimal PCB layout.