Online quesion deldunit-1-to_unit-4

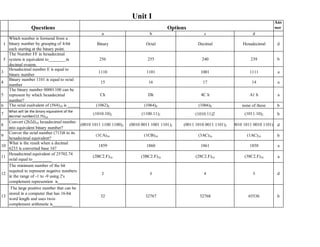

- 1. Questions Ans wer a b c d 1 Which number is formend from a binary number by gruoping of 4-bit each starting at the binary point. Binary Octal Decimal Hexadecimal d 2 The Number FF in hexadecimal system is equivalent to________in decimal system. 256 255 240 239 b 3 Hexadecimal number E is equal to binary number________ 1110 1101 1001 1111 a 4 Binary number 1101 is equal to octal number________ 15 16 17 14 a 5 The binary number 00001100 can be represent by which hexadecimal number? Ch Dh 4C h A1 h a 6 The octal eualvalent of (564)10 is ______ (1062)8 (1064)8 (1066)8 none of these b 7 What will be the binary equivalent of the decimal number(12.75)10 (1010.10)2 (1100.11)2 (1010.11)2 (1011.10)2 b 8 Convert (2b2d)16 hexadecimal number into equivalent binary number? (0010 1011 1100 1100)2 (0010 0011 1001 1101)2 (0011 1010 0011 1101)2 0010 1011 0010 1101)2 d 9 Conver the octal number (713)8 to its hexadecimal equivalent? (1CA)16 (1CB)16 (3AC)16 (1AC)16 b 10 What is the result when a decimal 6233 is converted base 16? 1859 1860 1861 1858 a 11 Hexadecimal equivalent of 25702.74 octal equal to_________ (2BC2.F)16 (3BC2.F)16 (28C2.F)16 (38C2.F)16 a 12 The minimum number of the bit required to represent negative numbers in the range of -1 to -9 using 2's complement represention is_________ 2 3 4 5 d 13 The large positive number that can be stored in a computer that has 16-bit word length and uses twos complement arithmetic is_________ 32 32767 32768 65536 b Options Unit I

- 2. 14 The greatest negative number which can be stored in a computer that has 8- bit word length and uses two's complement arithmatic is_________ -256 -255 -128 -127 c 15 2's complement of -15 decimal is_____ 10010 10001 10000 O1111 b 16 In a digital computer binart substraction is performed___________ in the same way as we perform substraction in the decimal number using 2's complement method using 9's complement method using 10's complement method b 17 For the electrical symbol illustrated below represents a_________ one input "on",the other "off" both input "on" both input "off" first input "off",the second "on" c 18 For a three input NAND gate the output is 0 only when______ all input logic 1 all input logic 0 any one input logic 1 a 19 The 14 pin TTL integretedcircuit with four,two input______ gates inside, is IC 7400 OR AND NAND c 20 In a 3 input NOR gate,the number of states in which output is 1 equals_____ 1 2 3 4 a 21 Ex-OR gate can work as 'NOT' gate provided______ one input is fixed at logic level 1 one input is fixed at logic level 0 by shorting both inputs none of the above a 22 what logic function corresponds to the following arrangement? F=S1 OR (S2 AND S3) OR S4 F=S1 AND (S2 OR S3)AND S4 F=(S1 OR S2) AND (S3 OR S4) F=(S1 AND S2)OR (S3 AND S4)b 23 The____ and _____ gates are known as "Universal Gates". NAND, NOR NAND, EX-OR OR, AND a 24 The output of a logic gate is 0 when all its input are at logic 1. The gate is either _____ a NAND or an AND a NAND or an EX-OR a NOR or an EX-NOR a NAND or an EX-NOR b

- 3. 25 Which of the following statement is true? AND and NOT gates are not sufficient for the realization of any logical function OR and NOT gates are sufficient for the realization of any logical function NOR gate are sufficient to realize of any logical function NAND gate are not sufficient to realize of any logical function d 26 The NAND-NAND logic is equivalent to ____ AND-NOT logic AND-OR logic OR-AND logic NOT-OR logic b 27 (FA)16 XOR (CB)16 is equal to_______ (30)16 (31)16 (32)16 (21)16 b 28 (1010 1100)2 XOR (1100 1010)2 is equal to______ (0110 0110)2 (66)16 (146)8 all of these d 29 The circuit shown below is functionally equivalent to______ NOR gate OR gate EX-OR gate NAND gate c 30 (A.B) .C= A.(B.C) represents________ law commutative associative distributive b 31 A+ĀB=______ + + + b 32 + + =__________ 0 1 A a 33 The expression AB + BC + C when simplified is_______ A.B C AB+C None c 34 Which of the following statement is an example of the associate Law of Boolean algebra ? X+(Y+Z)=(X+Y)+Z X(Y+Z)=XY+XZ X+Y=Y+Z (W+X)(Y+Z)=WY+ WZ+XY+XZ a 35 A code in which each digit position of the number represents a specific weight is called______ non-weighted code weighted code Alphanumaric code error detecting code c 36 In _codes each succeeding code is one binary number greater than preceding code. BCD Reflective alphanumeric sequential c

- 4. 37 Which of the following statement is true about excess-3 code? It is non weighted code It is sequential code It is self complementing code. All of these d 38 Gray code is_. reflecting code cyclic code non-weighted code all of these d 39 Which of the following is a weighted code? 3321 4221 5211 all of these d 40 In 5311 code,the decimal 7 is represented by_. 1010 1111 O111 1011 d 41 The BCD equivalent of excess-3 1100 1010 is_. 1100 1010 1001 1010 1001 0111 1010 1100 c 42 THE Gray code equivalent Of binary 10111011_. 11100110 11100111 11100101 11100100 a 43 In"Sign and Magnitude"method,if operands have different sign then how is the product considered? Positive Negative Sign of bigger number None of these b 44 Which of the following statement is not true about excess-3? In excess-3,9's complement and complement of any number is same It is a weighted code It is reflective code. It is a sequential code b 45 In a negative logic system the voltages corresponding to LOW and HIGH levels respectively are given below.Identify the voltages which correspond to negative logic system. 0 V and5 V 1 V & 5 V 5 V & 0 V 1V & 8 V c 46 A very large scale integration (VLSI)chip has _. 12 to 99 gates 100 to 9,999 gates 10,000 to 99,999 gates more than 100,000 gates d 47 Faster switching OFFof a p-n junction _. requires zero current in the reverse direction requires reverse saturation current in the reverse direction requires a large current in the reverse direction is independent of the reverse current c 48 Which is the best figure of merit from the options given below? 1pJ 10pJ 50pJ 100pJ a 49 TTL logic families use____. junction field-effect transistors p-n junctions n-p-n transistors MOSFETs c 50 Two input TTL NAND gate consists of_transistors. 1 2 3 4 d 51 An open input terminal of a TTL gate _. will behave as if it is connected to logic 0 level will behave as if it is connected to logic 1 level will assume some voltage between logic 0 and 1 levels none of these b 52 Wired logic is not possible in_. ECL TTL with active pull-up open-collector TTL TTL with passive pull-up b 53 The main disadvantage of TTL with totem-pole output is_. high power dissipation low fan-out that wire-ANDing operation is not allowed low noise margin b

- 5. 54 Which TTL family is used for commercial applications? 74XX 74LSXX 54XX None of these c 55 Schottky TTL is a_. non-saturated bipolar logic saturated bipolar logic current source logic high threshold logic a 56 CMOS logic consists of _. only n-channel MOS devices only p-channel MOS devices MOS devices and capacitors p-channels and n- channelsMOS devices d 57 The most commanly used configuration of a transistor as a CB CC CE CE or CC c 58 _devices do not have the problem of storage and removal of minority charge carriers. FET MOSFET BJT both a and b d

- 6. Q.No Questions Answer 1 Each individual term in standard SOP form is called_. literal maxterm minterm c 2 The maxterm,designator of the term Ā+ + C +D is_______ 2 3 10 none of these b 3 A swiching function f(A,B,C,D)=ĀBCD+ĀBCD+ĀBC D+ ABCD+ABCD can also be written as____ Σ (1,3,5,7,9) Σ (3,5,7,9,11) Σ (3,5,9,11,13) Σ (5,7,9,11,13) b 4 If a three variable switching function is expressed as the product of maxterms by f(A,B,C)=∏(0,3,5,6), then it can also be expressed as the sum of minterms by ∏(1,2,4,7) ∑(0,3,5,6) ∑(1,2,4,7) ∑(1,2,3,7) c 5 A SOP form of logic expression consists of only minterms is known as____ SOP form POS form standard SOP form Standard POS form c 6 The boolean expression in the POS from is most suitable for desining logic circuits using only____ EX-NOR gates AND gates NAND gates NOR gates d 7 The boolean expression Y=∑ m((0,3,6,7,10,12) is equivalent to________ Y=∏ M(0,3,6,7,10,12,15)Y= ∏M(1,2,4,5,8,9,11,13,14,15) Y =∑ m(1,2,4,5,8,9,11,13,14,15 ) Y=∑ m(0,3,10,12) b 8 The Boolean Expression Y=(A+B+C).(A+ B +C)+(A+ B +C ) is known as_______ standard SOP form SOP form POS form standard POS form d 9 The minimized expression for the K-map fo Fig.1 is________ ĀC BC ĀC+AB ĀC+BC+AB c Options Unit II

- 7. 10 The Logic opration of two circuits shown in ig. Are_________ different idential complementary dual b 11 The code used for labelling the cells of the K-map is________ natural BCD Hexadecimal gray octal c 12 In 4-variable K-map, a group of eight adjacent ones leads to a term with____ 1 variable 2 variable 3 variable 0 variable a 13 In K-map simplification,a group of four adjacent ones leads to a term with one litaral less than the total number of variables two litaral less than the total number of variables three litaral less than the total number of variables four litaral less than the total number of variables b 14 Karnaugh map is used ______ to minimize the number of FILP-FOLPs in a digital circuit to minimize the number of gates only in a digital circuit to minimize the number of gates and the fan-in requirment of the gates in a digital circuit to design gates c 15 The sum and carry output fo H.A. are 1 and 0,then its inputs are both(b)and( c) 0,1 1,0 1,1 a 16 Sum output fo half adder is= ĀB + A AB Ā + AB a 17 Sum output fo full adder is= Sum =A(B Cin) Sum =A B Cin Sum =A (B+C) b 18 A 3 binary adder should be _______ 3 full adders 2 full adder and half adder 1 full adder and 2 half adder 3 half adder b 19 A full adder can be relized using: one half-adder,two OR gatestwo half adder,one OR gatestwo half adder,two OR gates none of these b 20 The half adder circuit has input AB=11. The logic levels of the S and C outputs will be_______ S=1,C=1 S=0,C=0 S=1,C=0 S=0,C=1 d 21 Which of these expression are correct for half adder? 1.SUM=A.B+Ā 2.SUM=A. +Ā.B 3.CARRY=A.B 4.CARRY=A+B 1 and 3 2 and 3 2 and 4 1 and 4 b

- 8. 22 For a half -adder, which of the following statements is /are correct? 1.Is a half - substractor also. 2.Has two output CH=a,y and SH = x y for two input x and y 3.Has two output CH=x+y and SH= x y for two input x and y. 4.Is a combinational circuit. 1,3 and 4 1,2 and 4 4 only 2 and 4 d 23 Which of the following simplification method is most suitable when input variables exceeds five variables? K-map Boolean algebra Quine McCluskey All of these c 24 The difference bit output of a half- substraction is the same as: difference bit output of a full substractor sum bit output of a half addersum bit output of a full-addercarry bit output of a half-adder b 25 The half adder circuit in the given figure has input AB=11. The logic level of P and Q output will be_____ P = 0 and Q = 0 P= 0 and Q =1 P =1 and Q = 0 P = 1 and Q =1 b 26 A________ Is a digital circuit which selects one of the n data inputs and routes it to the output. multiplexer Demultiplexer Decoder a 27 if multiplexer has x select lines, it has _____output(s) one X 2 x a 28 The result of binary addition 1+1 is ____ carry0,sum0 carry 0,sum 1 carry 1, sum 0 carry 1,sum 1 c 29 The Boolean equations can be implemented using____ adder subtractor multiplexer c 30 Which device changes parallel data to serial data? Decoder multiplexer Demultiplexer Flip-Flop b 31 Two 16:1 and one 2:1 multiplexer can be connected to form a_________ 16:1 multiplexer 32:1 multiplexer 64:1 multiplexer 8:1 multiplexer b 32 For an n:1 multiplexer the number of select line are 2 n log2n log10n b

- 9. 33 A demultiplexer has one data input,m control input and n output ,then____ 2m =m 2m =n nm =2 m2 =2 b 34 A decoder circuit does not have the____input select data control b 35 A demultiplexer has________. one data input and a number selection inputs, and they have several output one input and one outputseveral input and several outputseveral input and one output a 36 An encoder conver________ noncoded information into coded form coded information into noncoded form HIGHs to LOW LOWS to HIGHs a 37 A 4-variable logic expression can be used to relized by using only one ____. NAND gate NOR gate demultiplexer 16:1 multiplexer d 38 A multiplexer can be used as a_______ logic element FLIP-FLOP counter 7-segment LED driver a 39 Which of the following statement are correct related to multiplexer? 1.selects one of the several inputs and transmit it to a single output. 2.Routes the data form single input to one of many output. 3.Can be used to convert parallel data into serial data. 4.Is a combinational circuit 1,2 and 4 2,3 and 4 1,3 and 4 1,2, and 3 c 40 Which of these come under the class of combinational circuit? 1.multiplexer 2.Read only memories 3.D-latch 4.Circuit as shown 1 and 2 3 and 4 1,2 and 3 1,2,3 and 4 a 41 Which of following is a combinational circuit? Shift Register Decoder Counter Ring counter b

- 10. 42 Consider the following statements: A 4:16 decoder can be constructed (with enable)by: 1.Using four 2:4 decoder(each with an enable input)only. 2.Using five 2:4 decoders (each with an enable input)only 3.Using five 3:8 decoders (each with an enable input)only 4.Using five 3:8 decoders (each with an enable input)and inverter. which of the statment given above is / are correct. 2 and 3 1 only 2 and 4 none of the above c 43 When two 16-bit input multiplexer drive a 2 input MUX,what is the result? 2-input MUX 4-input MUX 16-input MUX 32-input MUX d 44 A digital multiplexer can be used for which of the following? 1.Decoder 2.Many to one switch. 3.Implementation of combinational circuit 4.For code conversion. select the correct answer using the code giving below: 1,,3,and 4 2,3 and 4 1 and 2 only 2 and 3 only b 45 The IC 74153 is a_________ Multiplexer comparator parity generator and checker demultiplexer a 46 IC 74151 is a________ 4:1 mux 8:1 mux 16:1 mux 32:1 mux b 47 The______ is a 3:8 decoder. IC 74153 IC 74138 IC 74147 IC 7483 b 48 The______ is a decimal to BCD encoder. IC 74153 IC 74138 IC 74147 IC 7483 c 49 The ____is a dual 4:1 multiplexer. IC 74153 IC74138 IC 74147 IC7483 c 50 Which one of the following can be used as parallel to serial converter? Decoder Digital counter multiplexer demultiplexer c

- 11. Unit III Q.No Questions Answer 1 The output of a________ circuit at any instant of time dependant only on the input present at that instant of time combinational sequential combinational and sequential none of the above a 2 In the________ circuit,the output at any instant of time dependant on the present input as well as the past input/outputs. sequential combinational none of these a 3 sequential citcuits contain_________ no memory element at least one memory element all input applied simulteneously none of the above b 4 The data store by the memory element at any given instant of time is called the_____ state of the sequential circuit. next present tri b 5 _______ is not a sequential circuit. Flip-flop counter code converter shift register c 6 A counter is a_______ sequential circuit combinational circuit both combinational and sequential circuit none of above a 7 _____is also known as 1-bit memory cell. Flip-flop sets no change in a 8 By placing inverter between two inputs of an S-R flip-flop,we get______ flip- flop. D inverted SR JK a 9 Qn represents the _____value of a FF present state previous state next state a 10 The regester that shifts data in only right direction is called a______ shift register right left bidirectinal a 11 SISO stands for______ serial input and serial output sequential input and sequential output buffered serial input serial output clocked serial input and serial output a 12 SIPO stands for_______ clocked serial input and parallel output clocked sequential input and parallel output sequential input and parallel output serial input and parallel output d 13 The PIPO mode requires_____clock pulses to load a 8-bit number into register. 1 2 8 a 14 In a shift register,shifting right a bit by one bit means______ division by 2 multiplication by 2 substraction by 2 any of above a 15 The type register, in which data is entered into it only one bit at a time,but has all data bits available as output,is_______. serial in/parallel out register serial in /serial out register parallel in /serial out register parallel in /parallel out register a Options

- 12. 16 The number of state that binary counter goes through are_____,where n is equal to the number of flip-flop. 1/2n 2n 2n -1 c 17 A decade counter has ____number of states. 9 10 16 b 18 A counter has modulus of 10.the number of flip-flop are______ 10 5 4 3 c 19 A mod 4 counter will count________ from 0 to 4 from 0 to 3 form any number to n+4 none of above b 20 The ripple counter are also known as_____counter synchronous asynchronous none of these b 21 The output frequency of adecade counter, which is clocked from a 50 kHz signal is 5kHz 50kHz 500kHz 5000kHz a 22 A 4-bi synchronous counter uses flip- flop with propagation delay time of 15 ns each.the maximum possible time required for change of atate will be______. 15 ns 30 ns 45 ns 60 ns a 23 A 4-bit dwon counter can count from____ 0000 to 1111 1111 to 0000 000 to 111 111 to 000 b 24 The clock is used in sequential logic design for_____ less space performance speed synchronization d 25 In synchronouns digital system,the exact instance at which one more outputa can change the state is determined by the______. clock signal preset signal clear signal set and reset input a 26 The following is triggering method used in disital sytem______ positive edge triggering negative edge triggering positive level triggering above all d 27 In negative level triggering method,flip- flop is triggered when_____ clock is low clock is high preset is low clear is low a 28 The following is application of flip- flop____ register bounce elimination switch counters above all d 29 How are the Q and Q outputs of a flip- flop affected by setting the active low asynchronouns RESET input to a logic zero? Q=1 and Q=0 Q=0 and Q=1 Q=1 and Q=1 No change b 30 How many flip-flop are required to implement a divide-by-4 circuit? 4 3 2 1 c 31 What is the minmum number of flip- flop needed to build a mod 12 synchronous counter? 2 3 4 5 c

- 13. 32 Aflip-flop is used to store______. one bit of imformation two bit of information one nibble of information one byte of information a 33 In a J-K flip-flop,when J=K=1 and clock is appied the output Q will______ not change become 0 become 1 be complement of ht eoutput before the clock was applied d 34 The output Qn of a J-K flip-flop is 1.it change to 0 when a clock pulse is applied. The inputs Jn and Kn are______ respectively. 0 and X 1 and X X and 1 X and 0 c 35 The output Qn of a J-K flip-flop is 0.it change to 1 when a clock pulse is applied. The inputs Jn and Kn are______ respectively. 1 and X 0 and X X and 0 X and 1 a 36 The output Qn of a J-K or S-R flip-flop is 0,Its output does not change when a clock pulses is applied. The inputs Jn and Kn(or Sn and Rn)are________ respectively X and 0 X and 1 1 and X 0 and X d 37 The output Q and Q of a master-slave S-R flip-flop are connected to its R and S inputs respectively.its oputput Q when clock pulses are applied will be____ permanently 0 permanentaly 1 fixed 0 or 1 complementing with every clock pulse d 38 The output Qn of a T flip-flop is 1. it change to 0 when a clock pulse is applied . The input T is______ 0 1 X all of these b 39 ______flip-flop is also called delay flip-flop. SR D T JK b 40 If complement inputs are applied to S and R input of SR flip-flop,behaves like_____ T flip-flop D flip-flop J K flip-flop none of these b 41 The fig.1shows the circuit of____flip- flop D SR T JK a

- 14. 42 The below circuit illustrates a typical application of the J-K flip-flops. What does this represent? A shift register A data storege device A friquency divider circuit A decoder citcuit c 44 Which of the following statement is/are true? Master-slave JK flip-flop is free from race-around condition. Master slave uses two J-K flip-flops Both a and b Only a and not b c 45 Consider the following J-K flip-flop : In the above J-K flip-flop,J=Q and K=1.Assume that the flip-flop was initially cleared and then clocked for 6 pulse. What is the sequence at at the Q output? O1OOO O11OO1 O1OO1O O1O1O1 D 46 which one of the following equetion satisfies the J-K flip-flop truth tables? a 47 master-slave flip-flop is triggered______ when the clock input ia at HIGH logic level when the clock input is at the clock input. when a pulse Is applied at the clock input. when the clock input is at LOW logic level c 48 ______consists of dual D flip-flops. IC 7473 IC 7474 IC 7476 None of these b 49 IC_______ has divide by 2 and divide by five counters 74191 7490 74163 74169 b 50 which of the following statement(s) is/are true about IC 74191? It is a synchronounce counter it is an up/down counter it has parallel load capability All of these d

- 15. Q.No Questions Answer 1 The initial contents of the 4-bit serial-in-parallel-out,right shift, shift register shown are 0110. After three clock pulses are applied the contents of the shift register will be_______ 1111 c 2 The output of a Moore sequential machine is a function of______ all present states of the machine all the input a few combination of input and the present state all the combination of input and the present state a 3 Minimum number of J-K flip-flops needed to construct a BCD counter is____ 2 3 4 5 c 4 The number of unused states in a 4- bit Johnson counter is_____ 2 4 8 12 c 5 The total number of 1s in a 15-bit shift register is to be counted by clocking into the counter which is preset to 0.The counter must have which one of the following 4-bit 5-bit 16-bit 6-bit a 6 12 MHz clock frequency is applied to cascaded counter of mudulus-3 counter, modulus-4 counter and modulus-5counter.what are the lowest output frequency and overall modulus, respectively? 200 kHz,60 1 MHz,60 3 MHz,12 4 MHz,12 a Options Unit IV

- 16. 7 The circuit given below is that of a___ Mod-5 counter Mod-6 counter Mod-7 counter Mod-8 counter a 8 Which of the following capabilities are available in a universal shift register? Shift left shift right Parallel load All of these d 9 A ring counter consisting of five flip- flops will have 5 states 10 states 32 states infinite states a 10 The initial state of MOD-16 down counter is 0110. After 37 clock pulses,the state of the counter will be____ 1011 O110 O101 OOO1 d 11 The sequence detector is required to give a logical output of 1 whenever the sequence 1011 is detected in the incoming pulse stream. Minimum number of flip flops needed to build the sequence detector is _____ 4 3 2 1 b 12 The counter using four JK flip flops, all the flip flops get triggered simulteneously. This counter circuit _____ is a combinational circuit is an asynchronous circuit is an synchronous circuit may be a combinational or sequential circuit c 13 Data can be changed from temporal code to spacial code by using Timer circuits Synchronous counters Shift registers Combinational circuits c 14 Data can be changed from spacial code to temporal code by using Shift registers Counters Combinational circuits A/D Converters a 15 An universal registers ______ accepts serial input accept parallel input given serial and parallel outputs Is capable of all of the above d 16 A Twisted-ring counter consisting of five flip flops will have 5 states 10 states 25 states 125 states b

- 17. 17 The number of states in a decates counter are ____ 4 8 10 16 c 18 In a four bit Binary Ripple counter, for every input clock pulses ____ all the flip flops get clocked simulteneously Only one flip flop get clocked at a time Two of the flip flops get clocked at a time all the above statements are false d 19 A 3-bit binary ripple couter uses flip- flop with propagation delay time of 25 ns each. The maximum possible time required for change of state will be____ 25 ns 50 ns 75 ns 100ns c 20 A 3-bit synchronous couter uses flip- flop with propagation delay time of 25 ns each. The maximum possible time required for change of state will be____ 25 ns 50 ns 75 ns 100ns a 21 The maximum possible number of state in a ripple counter consisting of three flip-flops is_____. 4 8 10 16 b 22 The maximum number of flip-flops required for a synchronous decade counter are___. 1 2 4 10 c 23 The maximum number of flip-flops required for a divide-by-13 circuit are___. 4 8 12 16 a 24 A mod-2 counter followed by a mod- 5 counter is_____. same as a mod-5 counter followed by a mod-2 counter a decade counter a mod-7 counter none of the above b 25 Symmetrical squarewave of time period 100 us can be abtined form squarewave of time period 10 us by using a____ Divide-by-5 circuit divide-by-2 circuit divide-by -5 circuit followed by a divide- by-2 circuit 4-bit binary counter c 26 A 4-bit presettable UP counter has prest input 0100. The presetting opretion takes place as soon as the counter becomes maximum,i.e. 1111. The modulus of this countr 15 10 11 12 c

- 18. 27 In genersl, a sequential logic gircuit consist of____. only flip-flops only gates flip-flops and combinatinal logic circuits only combinational logic circuit c 28 The fig. shows the wave form of_____ counter. Asynchronounce synchronounce ring Johnson c 29 The Fig.2 shows the waveform of ____counter. Asynchronounce synchronounce ring Johnson d 30 The IC 74194 is a_______ up counter down counter flip-flop universal shift-register d 31 When S1S0=00,the IC 74194 is in_____Mode shift left shift right hold parallel load c 32 When S1S0=01,the IC 74194 is in ____mode shift left shift right hold parallel load b 33 When S1S0=10,the IC 74191 is in___ mode shift left shift right hold parallel load a 34 When S1S0=11,the IC 74191 is in____mode. shift left shift right hold parallel load d

- 20. 50