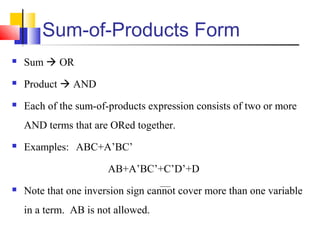

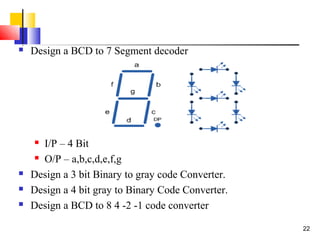

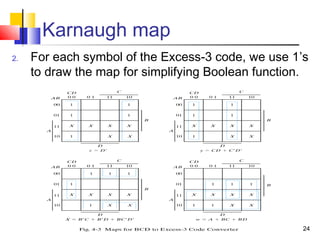

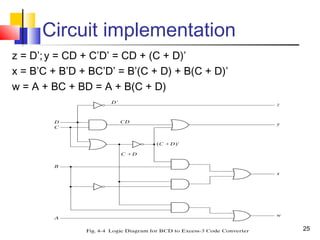

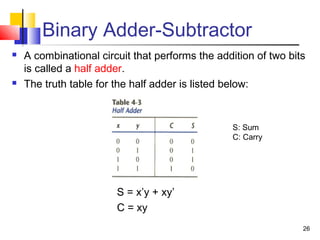

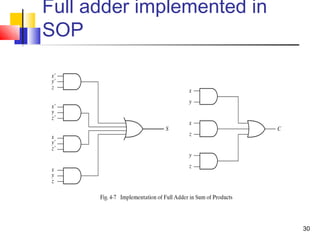

The document discusses combinational logic circuits. It covers sum-of-products and product-of-sums forms for representing logic functions. Methods for analyzing and simplifying logic circuits are presented, including Boolean algebra, Karnaugh maps, and deriving truth tables from logic diagrams. Examples of common logic circuits like adders, decoders, and converters are provided along with steps for designing combinational logic circuits.