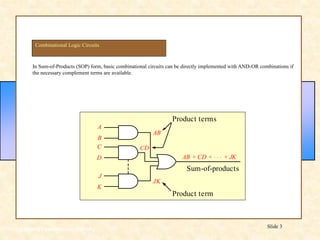

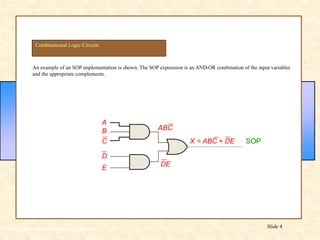

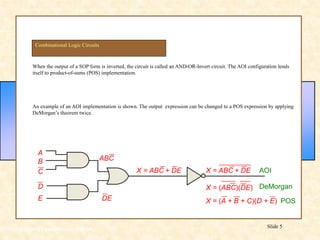

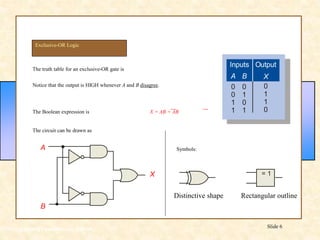

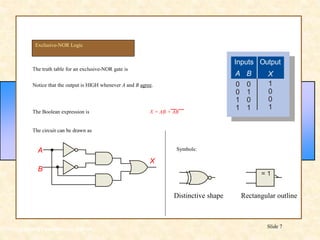

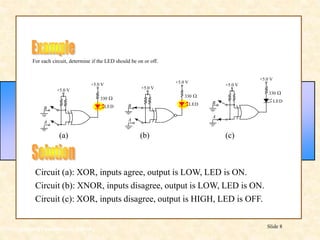

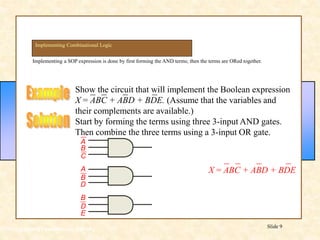

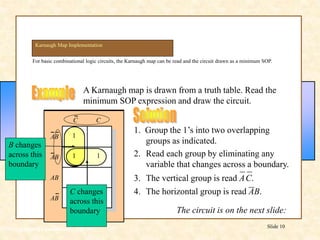

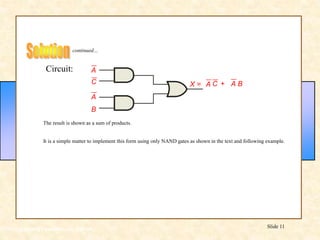

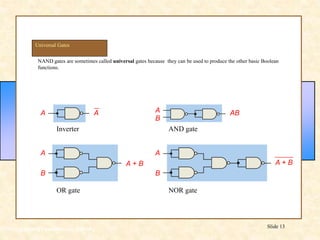

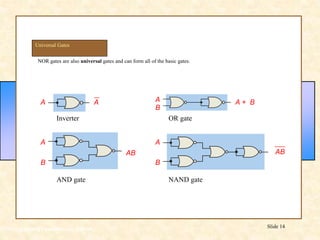

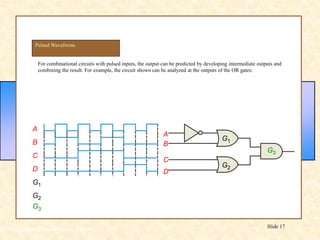

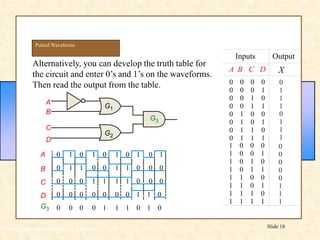

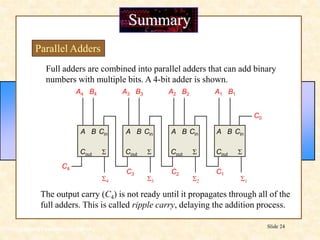

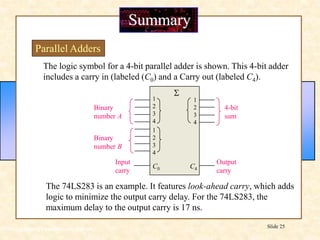

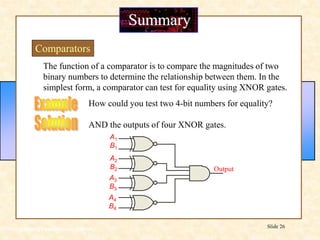

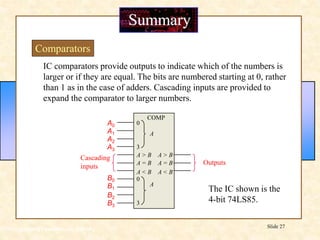

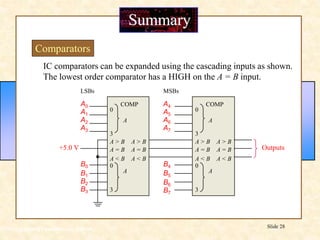

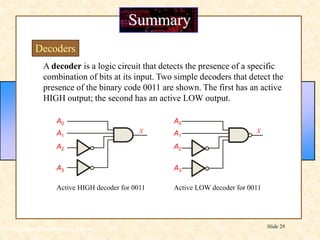

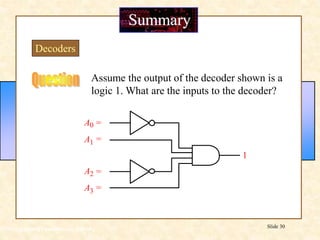

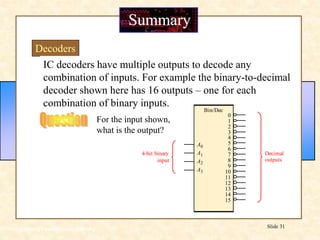

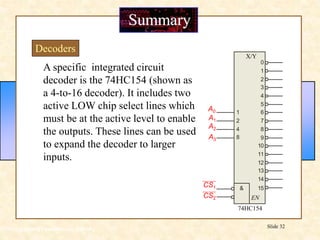

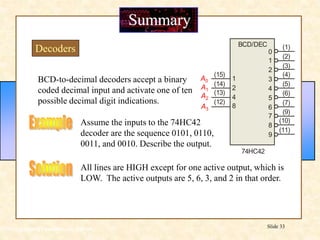

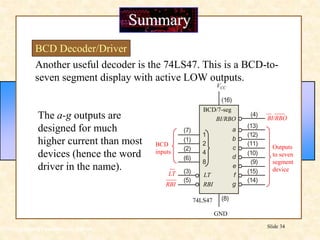

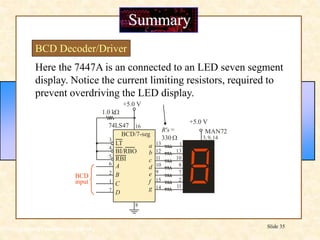

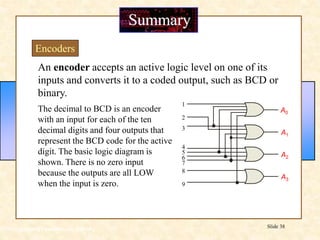

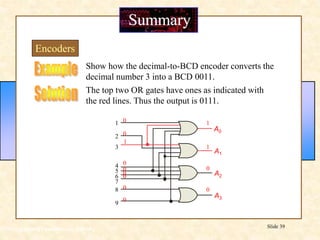

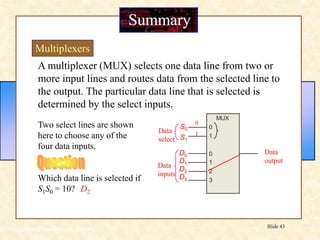

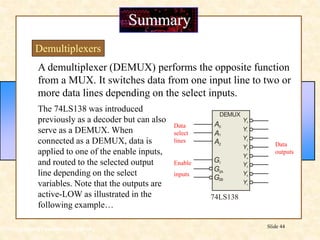

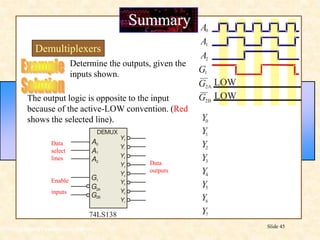

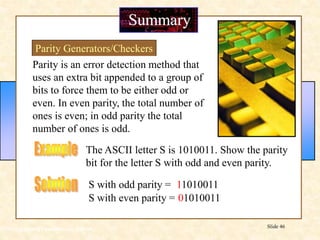

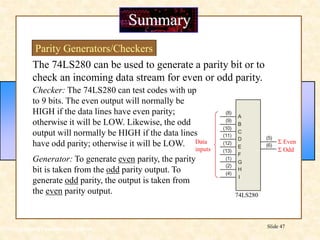

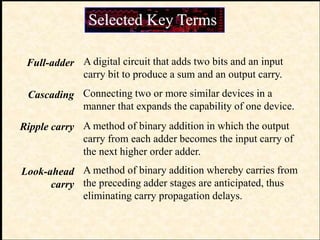

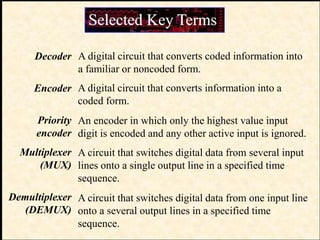

The document provides information about a course on digital electronics and combination logic circuits. It includes the course details, topics to be covered such as number systems, Boolean algebra, combinational logic circuits, and sequential logic circuits. It also lists recommended textbooks. The topics will cover number representations, logic gates, Boolean expressions, logic simplification techniques including Karnaugh maps, and basic combinational logic circuits such as adders, decoders, multiplexers. Sequential logic circuits including flip-flops will also be introduced. Worked examples applying concepts like Boolean algebra, logic gates, and circuit analysis are provided.