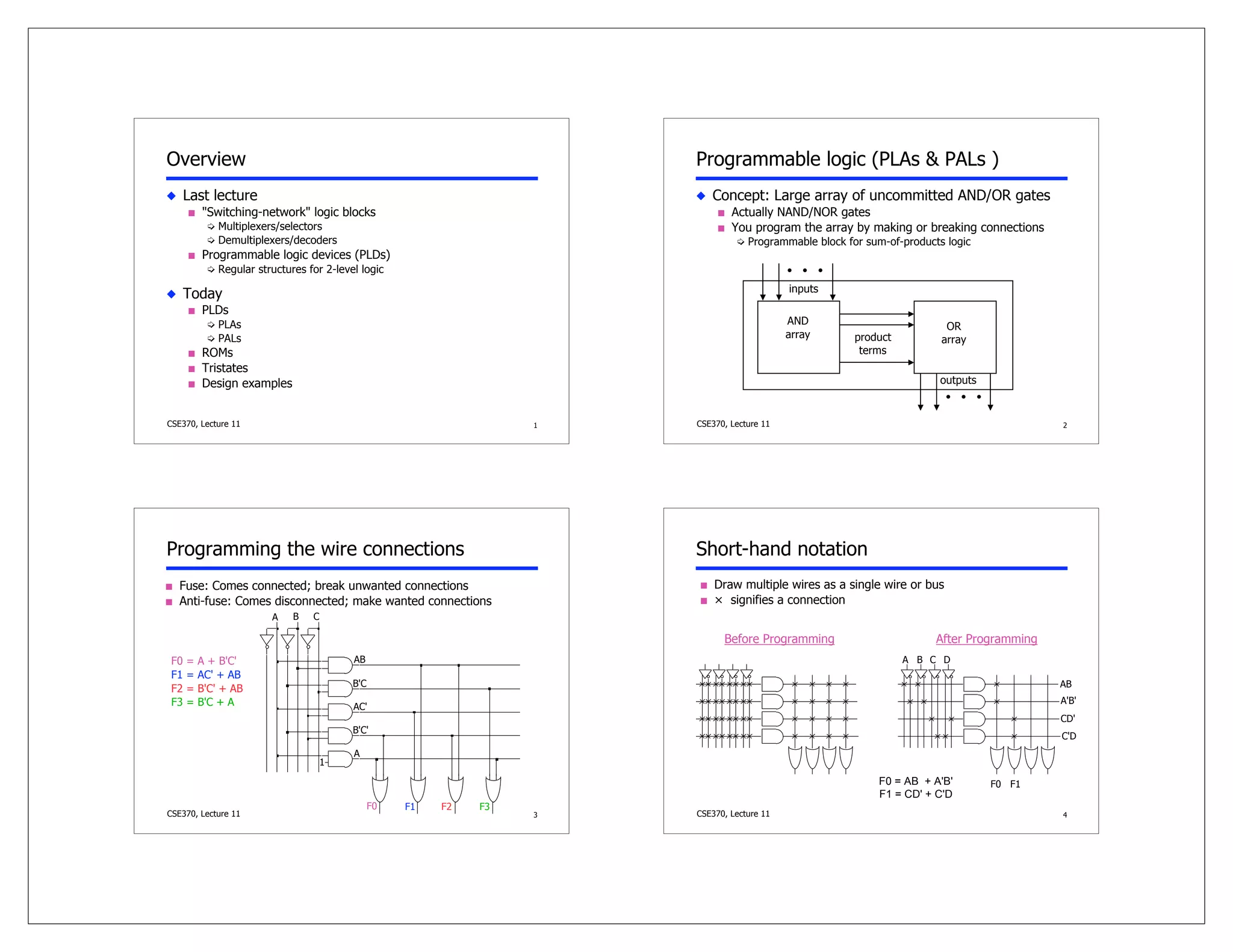

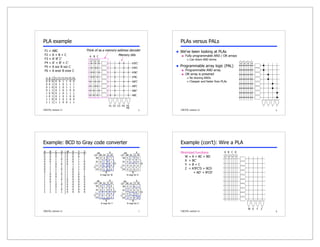

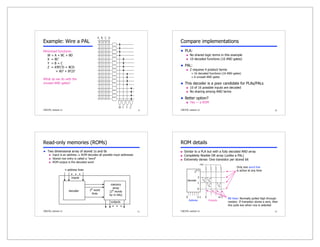

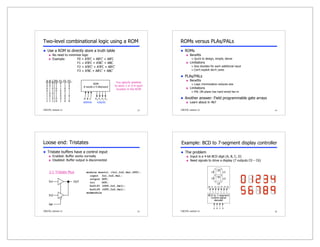

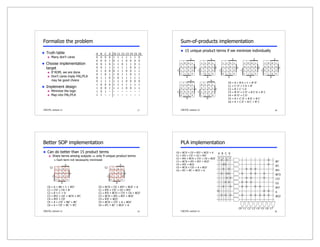

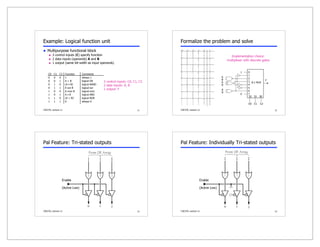

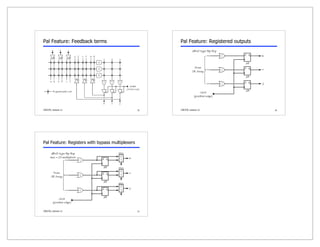

The document provides an overview of programmable logic devices including PLAs and PALs. It discusses how PLAs and PALs use programmable AND and OR gates to implement sum-of-products logic. It also covers ROMs as an alternative implementation and compares the tradeoffs between PLAs, PALs and ROMs. Examples are provided to illustrate designing logic functions using PLAs and PALs as well as implementing a BCD to 7-segment display decoder.