Report

Share

Recommended

Introduction to VHDL

Yaser Khalifa introduces you to VHDL (VHSIC Hardware Description Language), a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits.

Recommended

Introduction to VHDL

Yaser Khalifa introduces you to VHDL (VHSIC Hardware Description Language), a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits.

How to design Programs using VHDL

This Presentation covers most of VHDL designing basic from scratch.

click the below link for contents

http://eutectics.blogspot.com/2014/01/how-to-design-programs-using-vhdl-all.html

Introduction to VHDL

Overview on VHDL

Skills gained:

1- VHDL History and usage

2- VHDL design flow

3- Understand concurrency

This is part of VHDL 360 course

Programs of VHDL

This file is according to the syllabus of VHDL lab manual of Kurukshetra University, Kurukshetra.

VHDL-Behavioral-Programs-Structure of VHDL

VHDL-Behavioural Modelling-Structure of VHDL-Syntax and example programs

Introduction to VHDL

Introduction to VHDL presentation was given by Farzan Dehbashi and Parham Alvani

VHDL Packages, Coding Styles for Arithmetic Operations and VHDL-200x Additions

Describes the VHDL arithmetic packages and functions available. It also shows the new VHDL-200x packages and functions.

Session1

description of what FPGA consist of and how to programming it with VHDL hardware description language

More Related Content

What's hot

How to design Programs using VHDL

This Presentation covers most of VHDL designing basic from scratch.

click the below link for contents

http://eutectics.blogspot.com/2014/01/how-to-design-programs-using-vhdl-all.html

Introduction to VHDL

Overview on VHDL

Skills gained:

1- VHDL History and usage

2- VHDL design flow

3- Understand concurrency

This is part of VHDL 360 course

Programs of VHDL

This file is according to the syllabus of VHDL lab manual of Kurukshetra University, Kurukshetra.

VHDL-Behavioral-Programs-Structure of VHDL

VHDL-Behavioural Modelling-Structure of VHDL-Syntax and example programs

Introduction to VHDL

Introduction to VHDL presentation was given by Farzan Dehbashi and Parham Alvani

VHDL Packages, Coding Styles for Arithmetic Operations and VHDL-200x Additions

Describes the VHDL arithmetic packages and functions available. It also shows the new VHDL-200x packages and functions.

What's hot (20)

VHDL Packages, Coding Styles for Arithmetic Operations and VHDL-200x Additions

VHDL Packages, Coding Styles for Arithmetic Operations and VHDL-200x Additions

Similar to Vhdl

Session1

description of what FPGA consist of and how to programming it with VHDL hardware description language

Practical file

It contains file for Cad of Electronics lab. it have 5 practicals written with its vhdl code and test bench

Kroening et al, v2c a verilog to c translator

This is best book to learn verilog coding for electronics students.

VHDL summer training (ppt)

very high speed integrated circuit (VHDL) and hardware design, description

Building Hierarchy

1- Modeling Hierarchy

2- Creating Testbenches

Skills gained:

1- Reuse design units several times in a design hierarchy

2- Automate testing of design units

This is part of VHDL 360 course

Session 02 _rtl_design_with_vhdl 101

This course for someone with no previous experience with VHDL to learn VHDL language and write codes targeting hardware.

This course is focusing on syntax of VHDL, basic design circuits.

For all course videos and material visit YouTube channel

www.youtube.com/channel/UCcecv3gqLQCRT8MS3_aRn9Q

Similar to Vhdl (20)

Recently uploaded

Final project report on grocery store management system..pdf

In today’s fast-changing business environment, it’s extremely important to be able to respond to client needs in the most effective and timely manner. If your customers wish to see your business online and have instant access to your products or services.

Online Grocery Store is an e-commerce website, which retails various grocery products. This project allows viewing various products available enables registered users to purchase desired products instantly using Paytm, UPI payment processor (Instant Pay) and also can place order by using Cash on Delivery (Pay Later) option. This project provides an easy access to Administrators and Managers to view orders placed using Pay Later and Instant Pay options.

In order to develop an e-commerce website, a number of Technologies must be studied and understood. These include multi-tiered architecture, server and client-side scripting techniques, implementation technologies, programming language (such as PHP, HTML, CSS, JavaScript) and MySQL relational databases. This is a project with the objective to develop a basic website where a consumer is provided with a shopping cart website and also to know about the technologies used to develop such a website.

This document will discuss each of the underlying technologies to create and implement an e- commerce website.

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

CFD analysis is incredibly effective at solving mysteries and improving the performance of complex systems!

Here's a great example: At a large natural gas-fired power plant, where they use waste heat to generate steam and energy, they were puzzled that their boiler wasn't producing as much steam as expected.

R&R and Tetra Engineering Group Inc. were asked to solve the issue with reduced steam production.

An inspection had shown that a significant amount of hot flue gas was bypassing the boiler tubes, where the heat was supposed to be transferred.

R&R Consult conducted a CFD analysis, which revealed that 6.3% of the flue gas was bypassing the boiler tubes without transferring heat. The analysis also showed that the flue gas was instead being directed along the sides of the boiler and between the modules that were supposed to capture the heat. This was the cause of the reduced performance.

Based on our results, Tetra Engineering installed covering plates to reduce the bypass flow. This improved the boiler's performance and increased electricity production.

It is always satisfying when we can help solve complex challenges like this. Do your systems also need a check-up or optimization? Give us a call!

Work done in cooperation with James Malloy and David Moelling from Tetra Engineering.

More examples of our work https://www.r-r-consult.dk/en/cases-en/

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

Advancements in technology unveil a myriad of electrical and electronic breakthroughs geared towards efficiently harnessing limited resources to meet human energy demands. The optimization of hybrid solar PV panels and pumped hydro energy supply systems plays a pivotal role in utilizing natural resources effectively. This initiative not only benefits humanity but also fosters environmental sustainability. The study investigated the design optimization of these hybrid systems, focusing on understanding solar radiation patterns, identifying geographical influences on solar radiation, formulating a mathematical model for system optimization, and determining the optimal configuration of PV panels and pumped hydro storage. Through a comparative analysis approach and eight weeks of data collection, the study addressed key research questions related to solar radiation patterns and optimal system design. The findings highlighted regions with heightened solar radiation levels, showcasing substantial potential for power generation and emphasizing the system's efficiency. Optimizing system design significantly boosted power generation, promoted renewable energy utilization, and enhanced energy storage capacity. The study underscored the benefits of optimizing hybrid solar PV panels and pumped hydro energy supply systems for sustainable energy usage. Optimizing the design of solar PV panels and pumped hydro energy supply systems as examined across diverse climatic conditions in a developing country, not only enhances power generation but also improves the integration of renewable energy sources and boosts energy storage capacities, particularly beneficial for less economically prosperous regions. Additionally, the study provides valuable insights for advancing energy research in economically viable areas. Recommendations included conducting site-specific assessments, utilizing advanced modeling tools, implementing regular maintenance protocols, and enhancing communication among system components.

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.

Thank me later.

samsarthak31@gmail.com

Cosmetic shop management system project report.pdf

Buying new cosmetic products is difficult. It can even be scary for those who have sensitive skin and are prone to skin trouble. The information needed to alleviate this problem is on the back of each product, but it's thought to interpret those ingredient lists unless you have a background in chemistry.

Instead of buying and hoping for the best, we can use data science to help us predict which products may be good fits for us. It includes various function programs to do the above mentioned tasks.

Data file handling has been effectively used in the program.

The automated cosmetic shop management system should deal with the automation of general workflow and administration process of the shop. The main processes of the system focus on customer's request where the system is able to search the most appropriate products and deliver it to the customers. It should help the employees to quickly identify the list of cosmetic product that have reached the minimum quantity and also keep a track of expired date for each cosmetic product. It should help the employees to find the rack number in which the product is placed.It is also Faster and more efficient way.

Top 10 Oil and Gas Projects in Saudi Arabia 2024.pdf

Saudi Arabia stands as a titan in the global energy landscape, renowned for its abundant oil and gas resources. It's the largest exporter of petroleum and holds some of the world's most significant reserves. Let's delve into the top 10 oil and gas projects shaping Saudi Arabia's energy future in 2024.

Architectural Portfolio Sean Lockwood

This portfolio contains selected projects I completed during my undergraduate studies. 2018 - 2023

一比一原版(SFU毕业证)西蒙菲莎大学毕业证成绩单如何办理

SFU毕业证原版定制【微信:176555708】【西蒙菲莎大学毕业证成绩单-学位证】【微信:176555708】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

◆◆◆◆◆ — — — — — — — — 【留学教育】留学归国服务中心 — — — — — -◆◆◆◆◆

【主营项目】

一.毕业证【微信:176555708】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【微信:176555708】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

学历顾问:微信:176555708

Runway Orientation Based on the Wind Rose Diagram.pptx

Runway Orientation Based on the Wind Rose Diagram

Standard Reomte Control Interface - Neometrix

About

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

• Remote control: Parallel or serial interface.

• Compatible with MAFI CCR system.

• Compatible with IDM8000 CCR.

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

• Easy in configuration using DIP switches.

Technical Specifications

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

Key Features

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

• Remote control: Parallel or serial interface

• Compatible with MAFI CCR system

• Copatiable with IDM8000 CCR

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

Application

• Remote control: Parallel or serial interface.

• Compatible with MAFI CCR system.

• Compatible with IDM8000 CCR.

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

• Easy in configuration using DIP switches.

Recently uploaded (20)

Final project report on grocery store management system..pdf

Final project report on grocery store management system..pdf

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

Fundamentals of Electric Drives and its applications.pptx

Fundamentals of Electric Drives and its applications.pptx

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

Cosmetic shop management system project report.pdf

Cosmetic shop management system project report.pdf

Top 10 Oil and Gas Projects in Saudi Arabia 2024.pdf

Top 10 Oil and Gas Projects in Saudi Arabia 2024.pdf

block diagram and signal flow graph representation

block diagram and signal flow graph representation

Runway Orientation Based on the Wind Rose Diagram.pptx

Runway Orientation Based on the Wind Rose Diagram.pptx

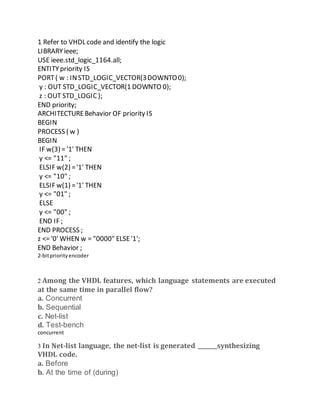

Vhdl

- 1. 1 Refer to VHDL code and identify the logic LIBRARYieee; USE ieee.std_logic_1164.all; ENTITYpriority IS PORT( w : INSTD_LOGIC_VECTOR(3DOWNTO0); y : OUT STD_LOGIC_VECTOR(1 DOWNTO 0); z : OUT STD_LOGIC); END priority; ARCHITECTUREBehavior OF priority IS BEGIN PROCESS ( w ) BEGIN IF w(3) = '1' THEN y <= "11" ; ELSIF w(2) ='1' THEN y <= "10" ; ELSIF w(1) ='1' THEN y <= "01" ; ELSE y <= "00" ; END IF ; END PROCESS ; z <= '0' WHEN w = "0000" ELSE'1'; END Behavior ; 2-bitpriorityencoder 2 Among the VHDL features, which language statements are executed at the same time in parallel flow? a. Concurrent b. Sequential c. Net-list d. Test-bench concurrent 3 In Net-list language, the net-list is generated _______synthesizing VHDL code. a. Before b. At the time of (during)

- 2. c. After d. None of the above After 4 Which data type in VHDL is non synthesizable & allows the designer to model the objects of dynamic nature? a. Scalar b. Access c. Composite d. File access 5 In the simulation process, which step specifies the conversion of VHDL intermediate code so that it can be used by the simulator? a. Compilation b. Elaboration c. Initialization d. Execution Elaboration 6 Hold time is defined as the time required for the data to ________ after the triggering edge of clock. a. Increase b. Decrease c. Remain stable d. All of the above remainstable 7 An Antifuse programming technology is predominantly associated with _____. a. SPLDs b. FPGAs c. CPLDs d. All of the above FPGAs 8 In fusible link technologies, the undesired fuses are removed by the pulse application of _____voltage & current to device input. a. Low b. Moderate

- 3. c. High d. All of the above High 9 The utilization of CAD tools for drawing timing waveform diagram and transforming it into a network of logic gates is known as ________. a. Waveform Editor b. Waveform Estimator c. Waveform Simulator d. Waveform Evaluator waveformeditor 10 State box without decision and conditional box is A. ASM block B. defined block C. simple block D. both a and b Simple block 11 Table that is not a part of asynchronous analysis procedure is a. transition table b. state table c. flow table d. excitation table d