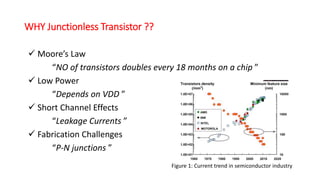

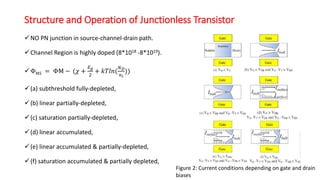

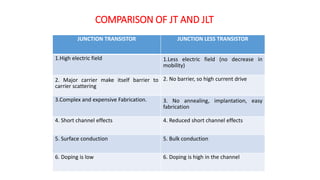

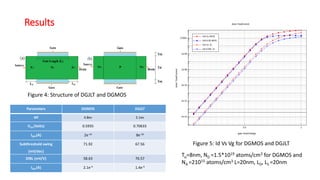

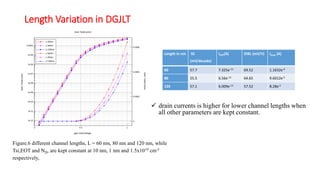

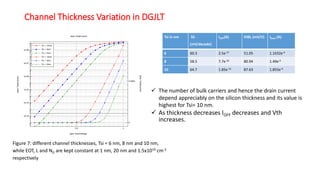

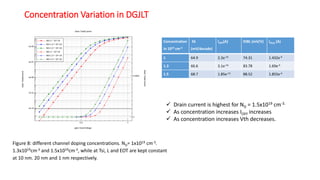

This presentation summarizes research on junctionless transistors and their applications. It introduces junctionless transistors as an alternative to traditional junction transistors that can help address challenges from Moore's Law like power consumption and short channel effects. The presentation describes the structure and operation of junctionless transistors. It then compares junctionless transistors to junction transistors, highlighting advantages like lower electric fields, easier fabrication, and reduced short channel effects. Several applications are discussed, with a focus on using junctionless transistors in DRAM to improve retention time and sense margin. Results are presented on optimizing the performance of double-gate junctionless transistors by varying length, thickness, and doping concentration. The conclusion discusses the near ideal subthreshold slope and potential for digital applications. Future