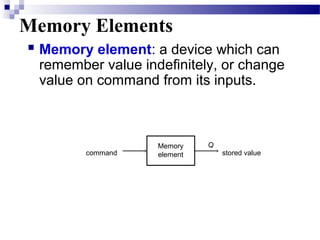

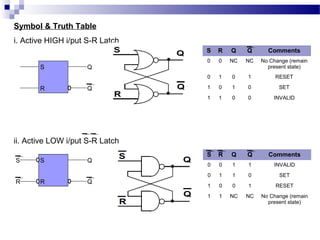

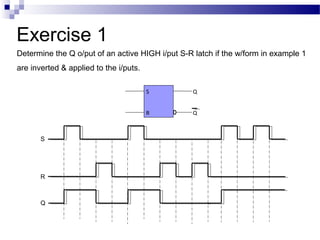

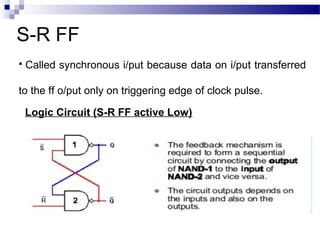

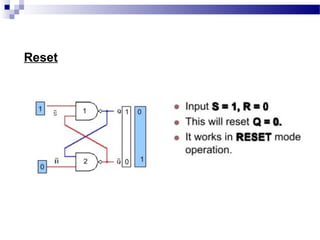

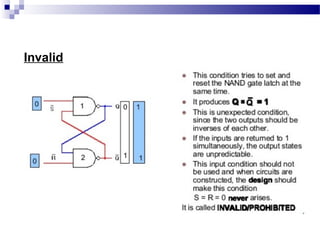

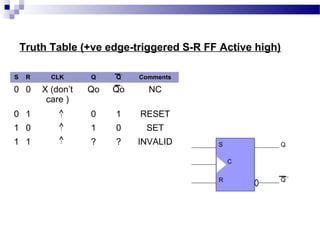

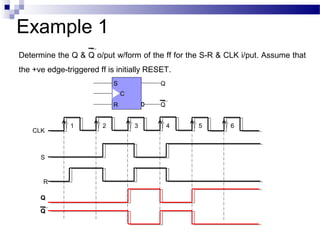

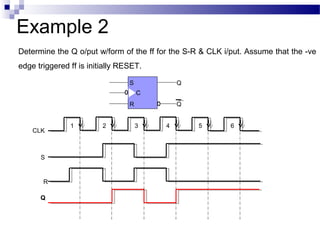

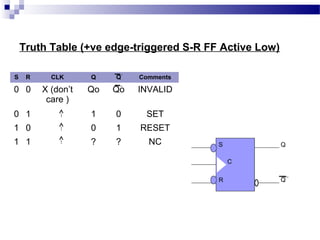

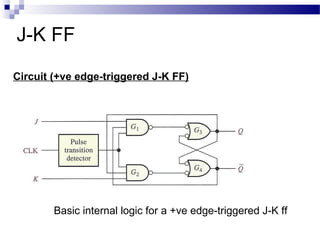

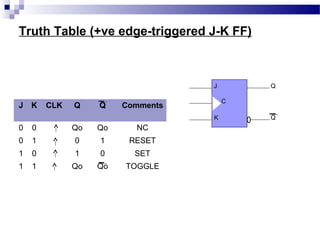

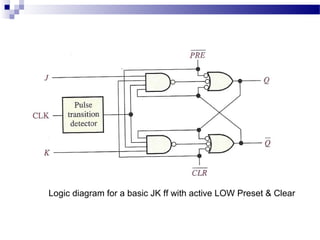

This document discusses sequential logic circuits and memory elements. It describes latches and flip-flops, which are basic memory elements used in sequential circuits. Specifically, it covers the set-reset (SR) latch, D flip-flop, and JK flip-flop. It provides their logic diagrams, truth tables, and examples of how their output changes in response to different input patterns over time. Asynchronous preset and clear inputs are also discussed as additional control inputs for flip-flops.