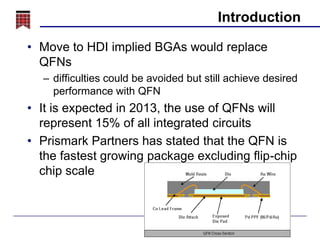

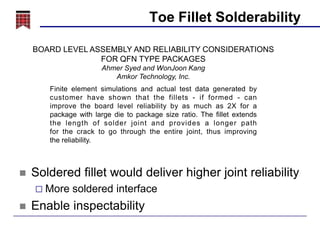

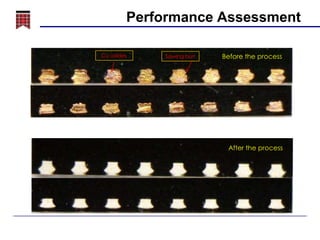

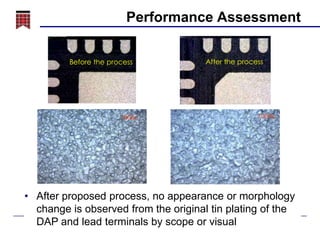

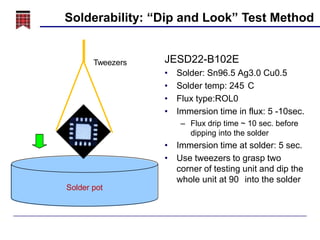

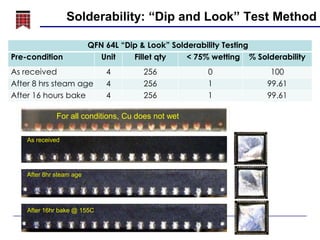

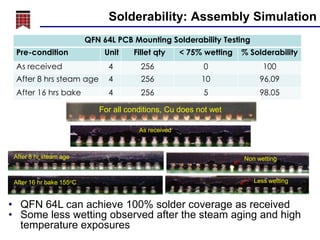

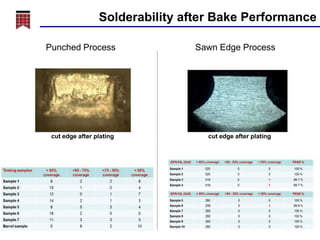

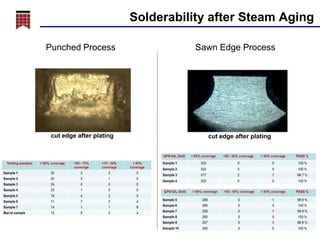

The presentation by Dr. John Ganjei discusses the reliability process improvements for Quad Flat No-lead (QFN) packages, highlighting challenges in solderability and the lack of industry standards. With QFNs expected to represent 15% of all integrated circuits, methods for enhancing solderability and reliability, such as chemical plating, are proposed. The ongoing need for consensus on preconditioning requirements for these components is emphasized to improve reliability and performance in assembly.