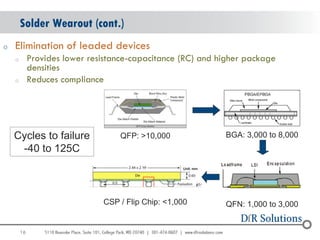

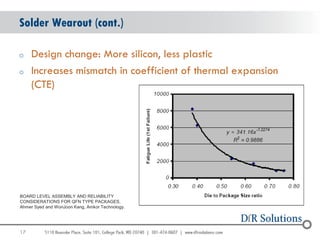

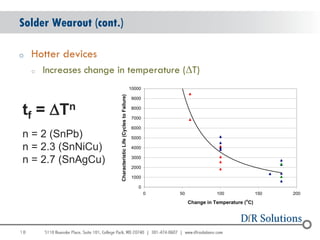

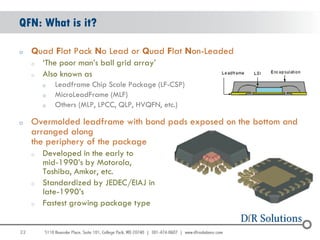

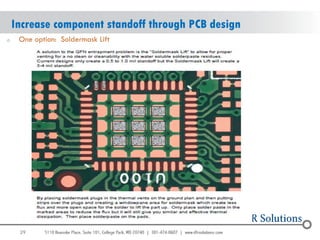

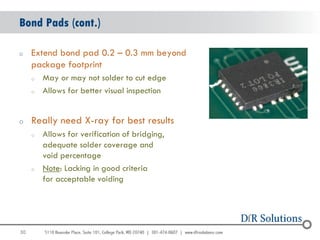

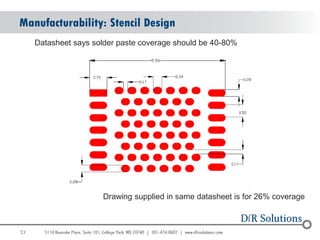

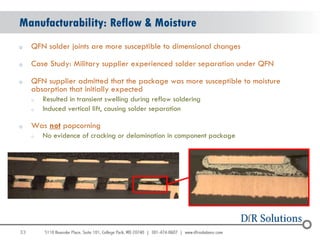

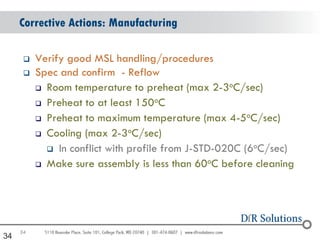

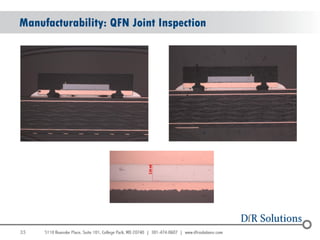

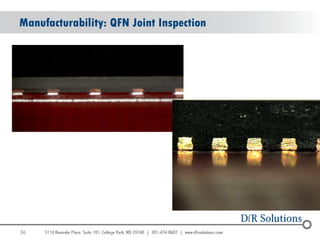

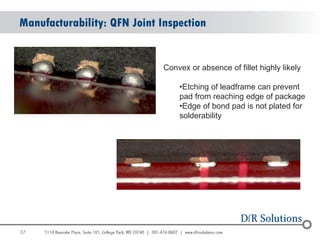

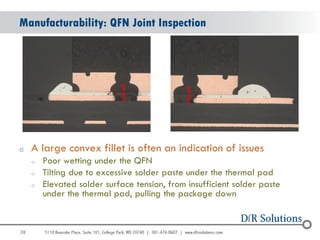

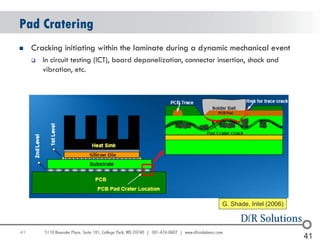

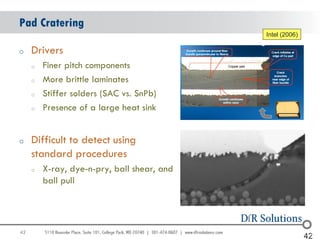

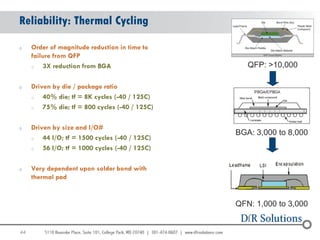

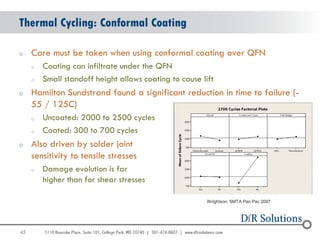

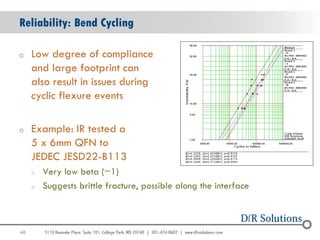

The document discusses the manufacturability and reliability challenges associated with Quad Flat No Leads (QFN) technology, highlighting issues related to solder wearout and testing parameters. It emphasizes the importance of understanding packaging processes and the influence of design on reliability, particularly in high-reliability applications. Additionally, the document outlines best practices for handling, inspection, and design considerations that can impact QFN manufacturing outcomes.