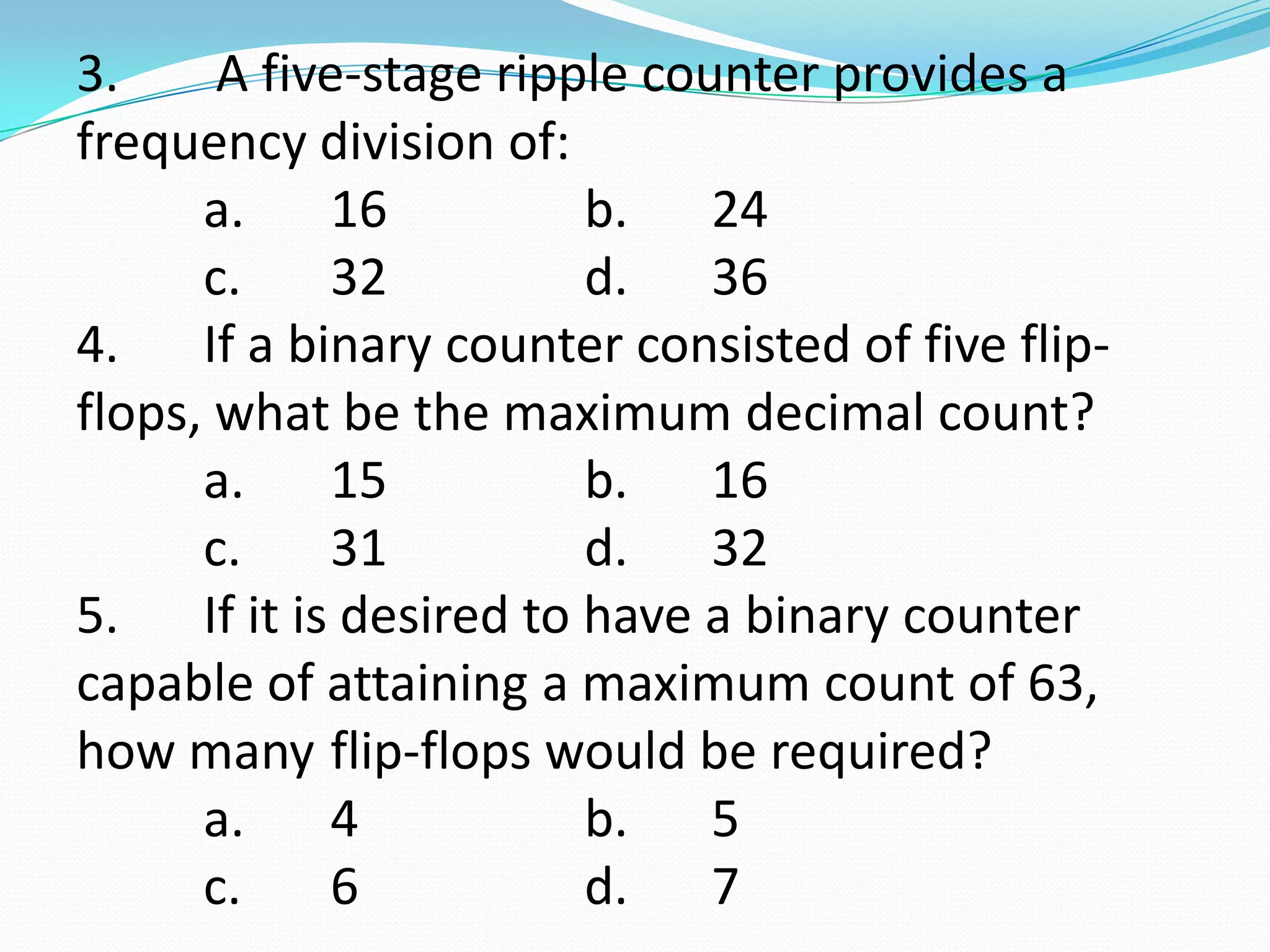

This document discusses ripple counters, which are asynchronous counters composed of multiple flip-flops connected in a chain so that the output of each flip-flop triggers the next. It describes how ripple counters can count up or down by complementing outputs or inputs. Control logic gates allow a counter to count up or down based on a command. Objectives cover identifying a basic up-counter, modifying it to count down, and adding control logic for up/down counting.