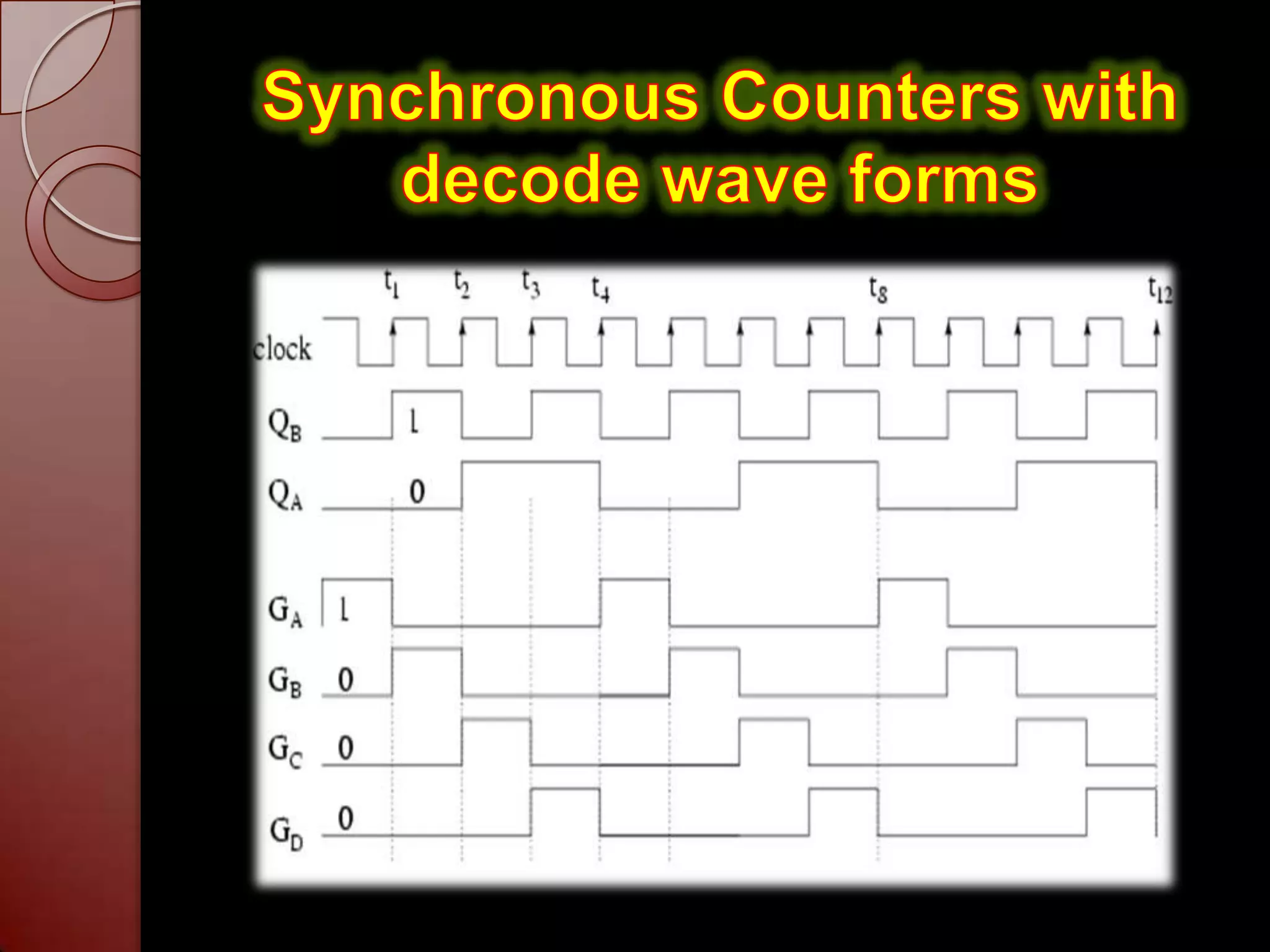

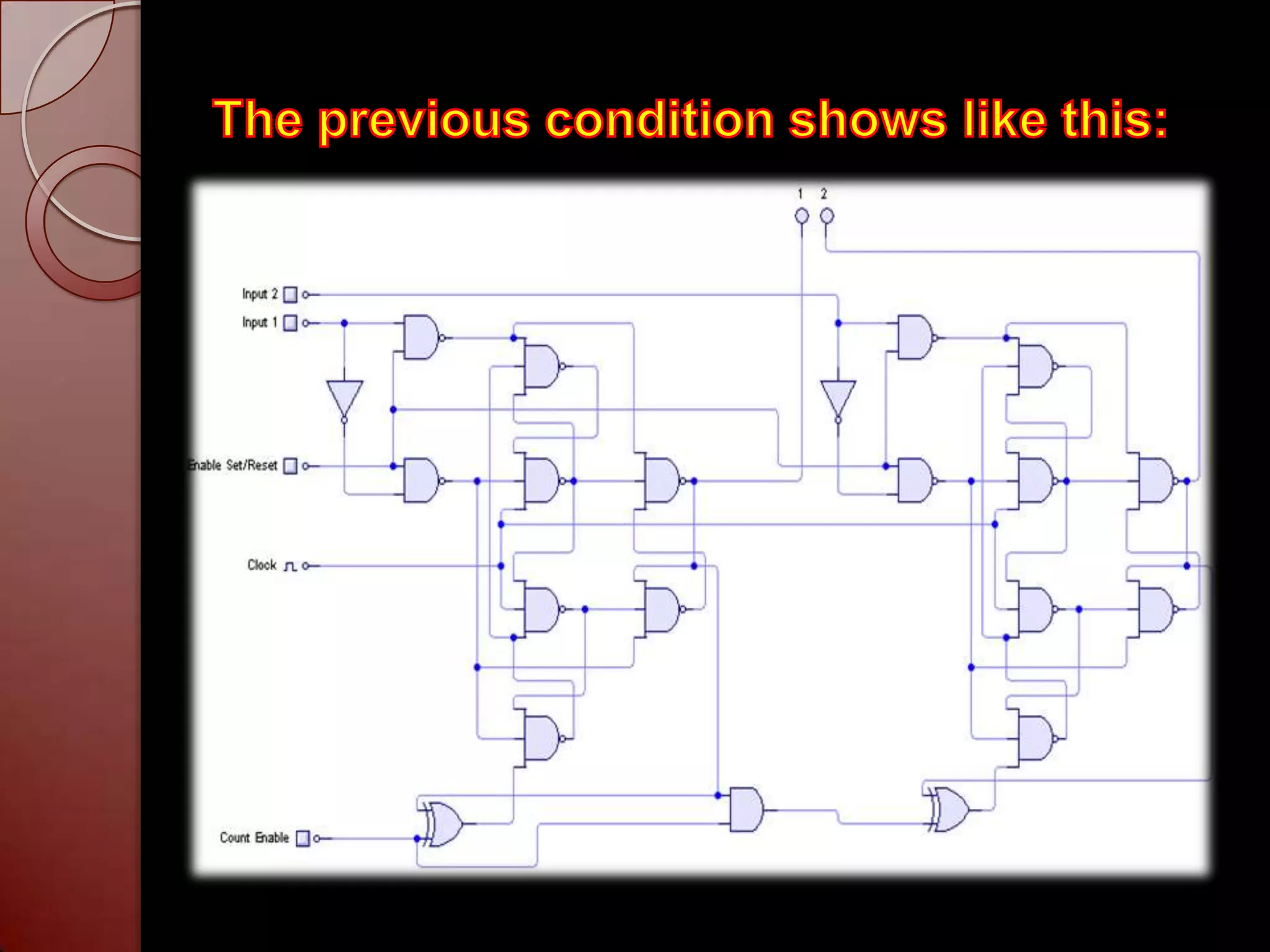

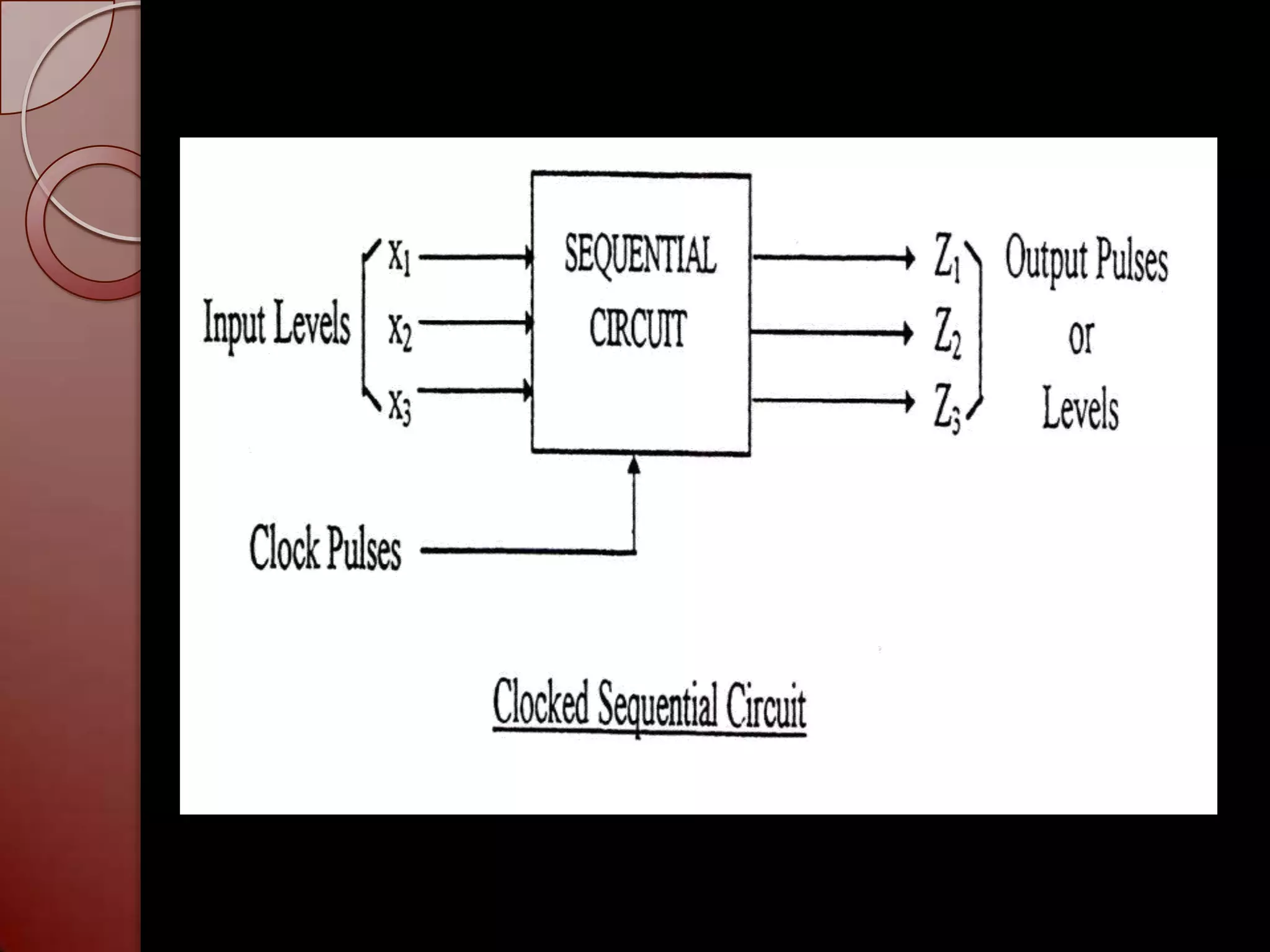

This document discusses synchronous counters and circuits. It defines synchronous as working at the same rate and having the same oscillation period. A synchronous circuit contains combinational gates, nets, and flip-flops connected to a central clock signal. Synchronous counters can be decomposed into flip-flops that store state, and combinational circuits that compute the output and next state based on the clock. The timing of inputs to the flip-flops must satisfy constraints to ensure correct functionality.