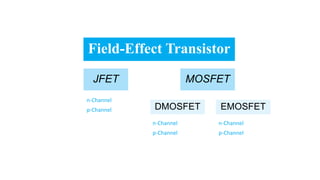

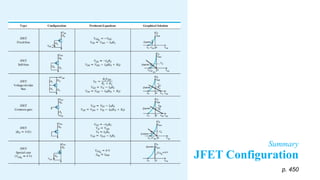

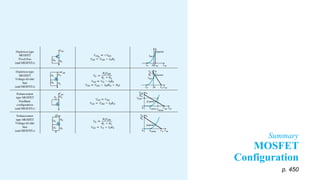

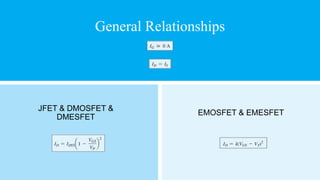

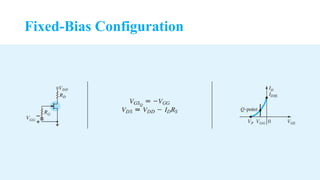

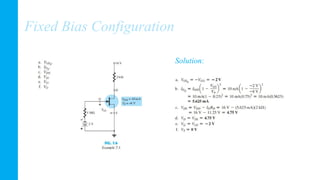

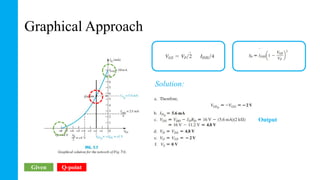

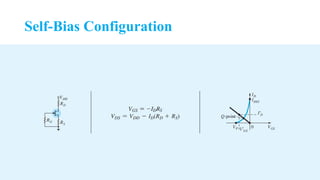

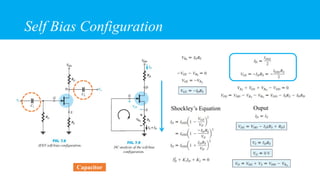

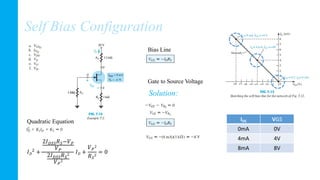

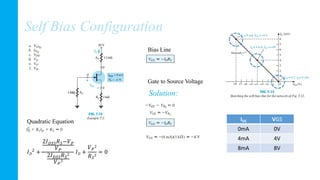

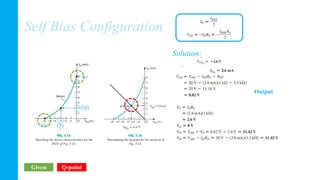

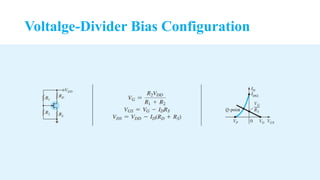

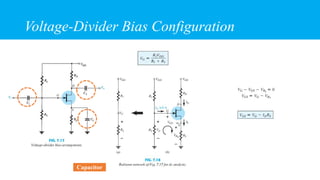

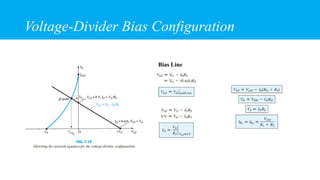

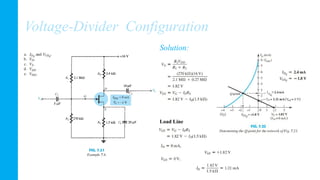

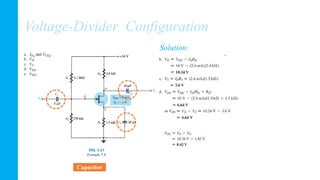

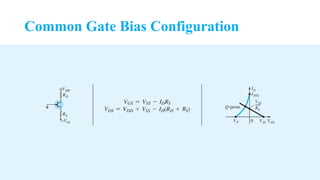

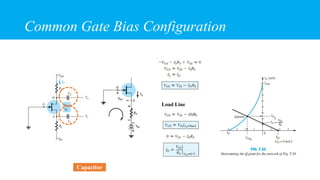

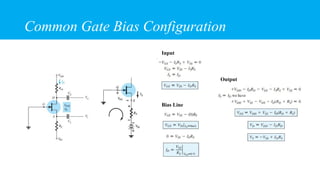

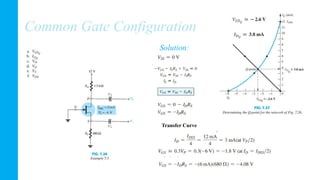

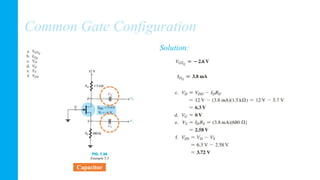

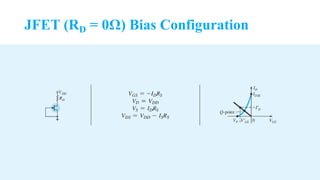

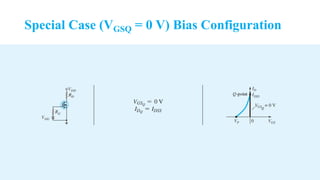

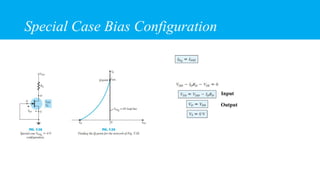

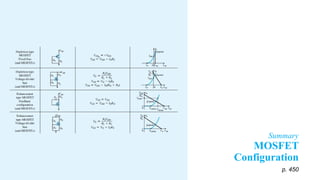

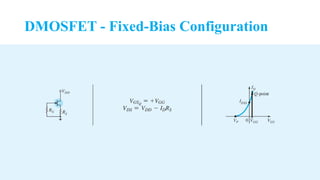

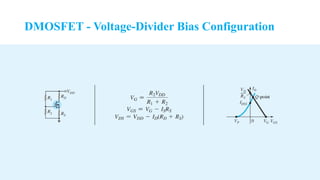

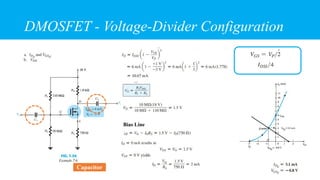

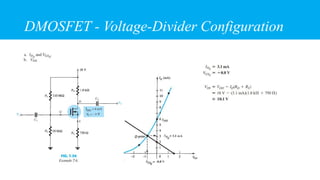

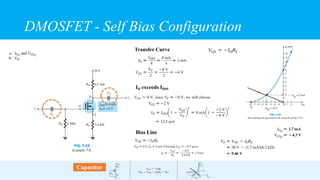

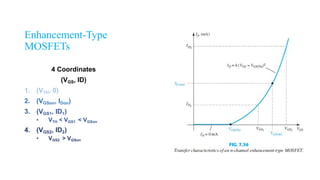

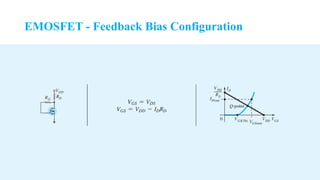

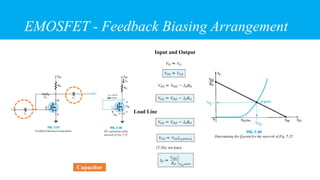

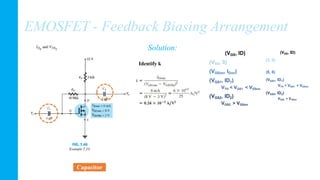

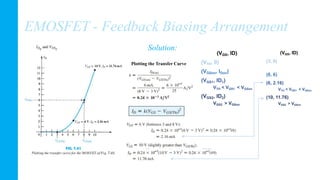

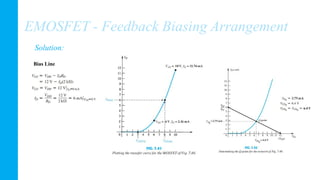

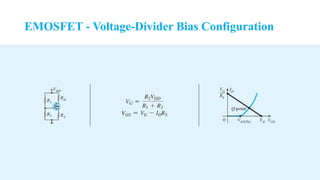

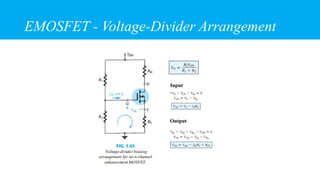

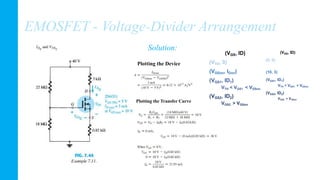

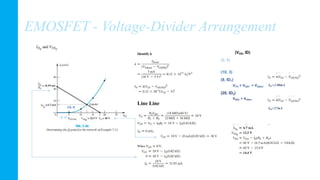

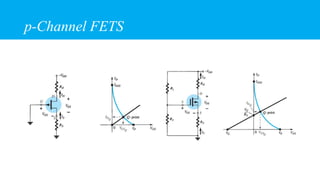

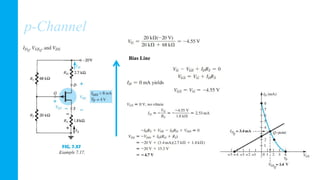

The document discusses various biasing configurations for field-effect transistors (FETs) including MOSFETs and JFETs. It provides examples of fixed bias, self bias, voltage divider bias, and feedback bias configurations. It also covers the differences between n-channel and p-channel devices as well as enhancement-type and depletion-type MOSFETs. Key aspects like the non-linear relationship between drain current and gate-source voltage, bias lines, load lines, capacitors, and transfer curves are examined.