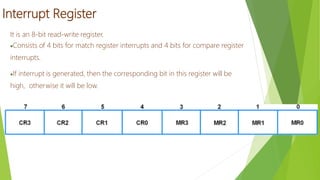

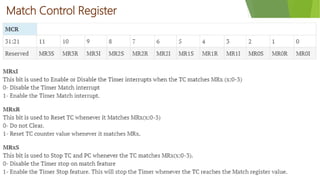

The document provides an overview of the LPC2148 timer unit in embedded and real-time systems, detailing its components such as the prescaler register and timer counter. It explains how the prescaler counter increments on each clock tick, the functionality of the timer control and match registers, and how actions can be triggered based on timer matches. Additionally, the document describes interrupt handling through an interrupt register that manages pending interrupts from various sources.