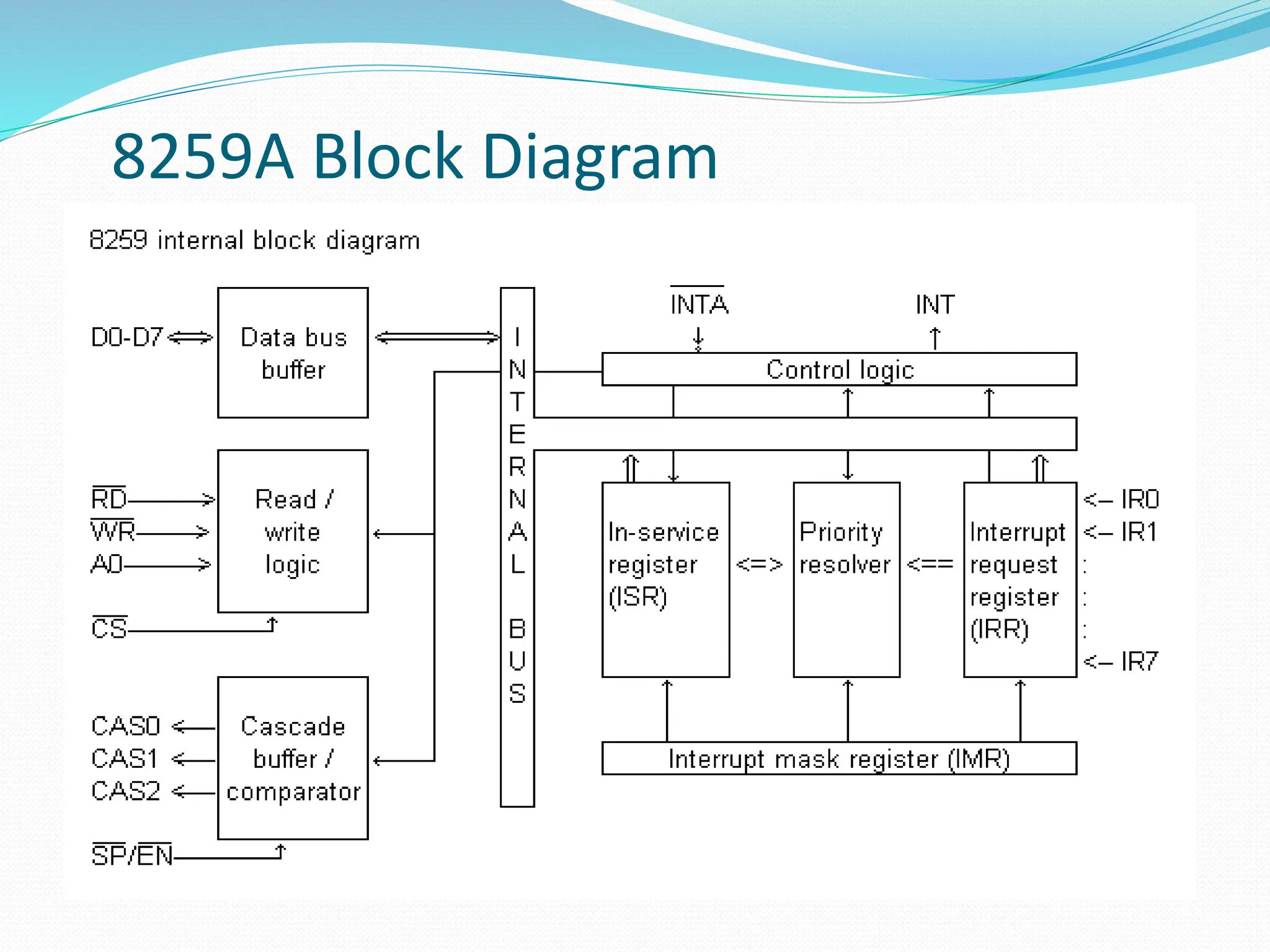

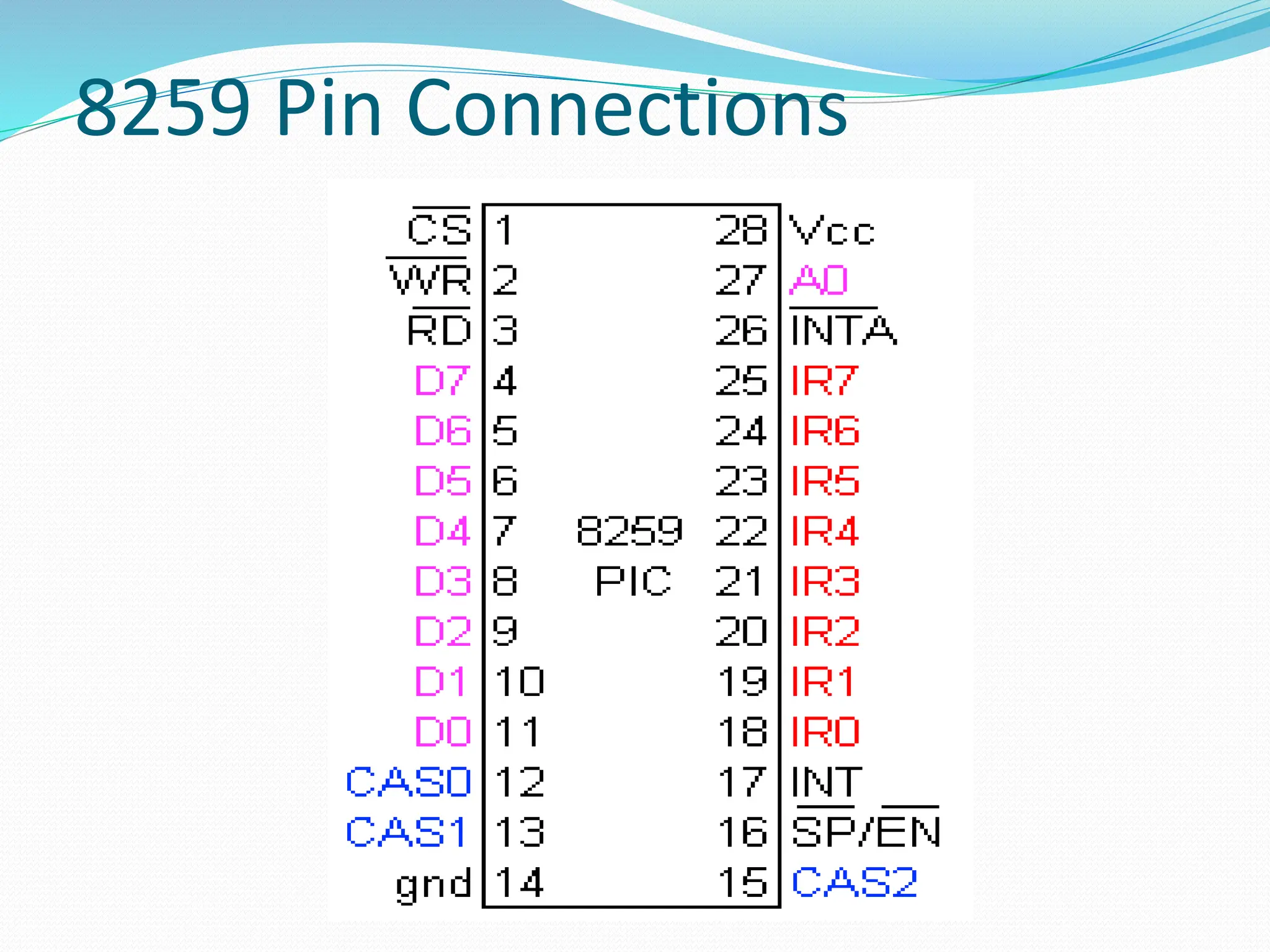

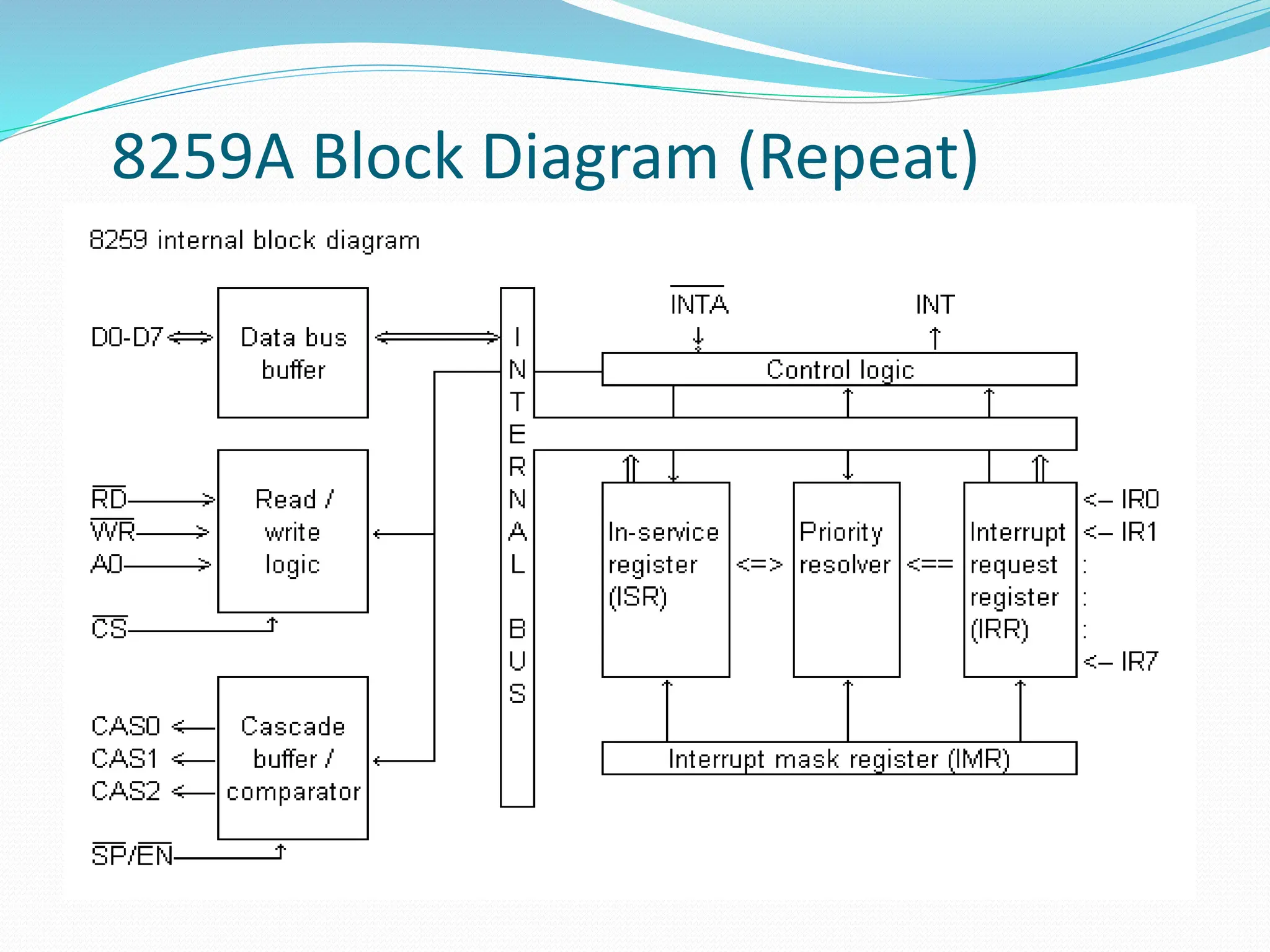

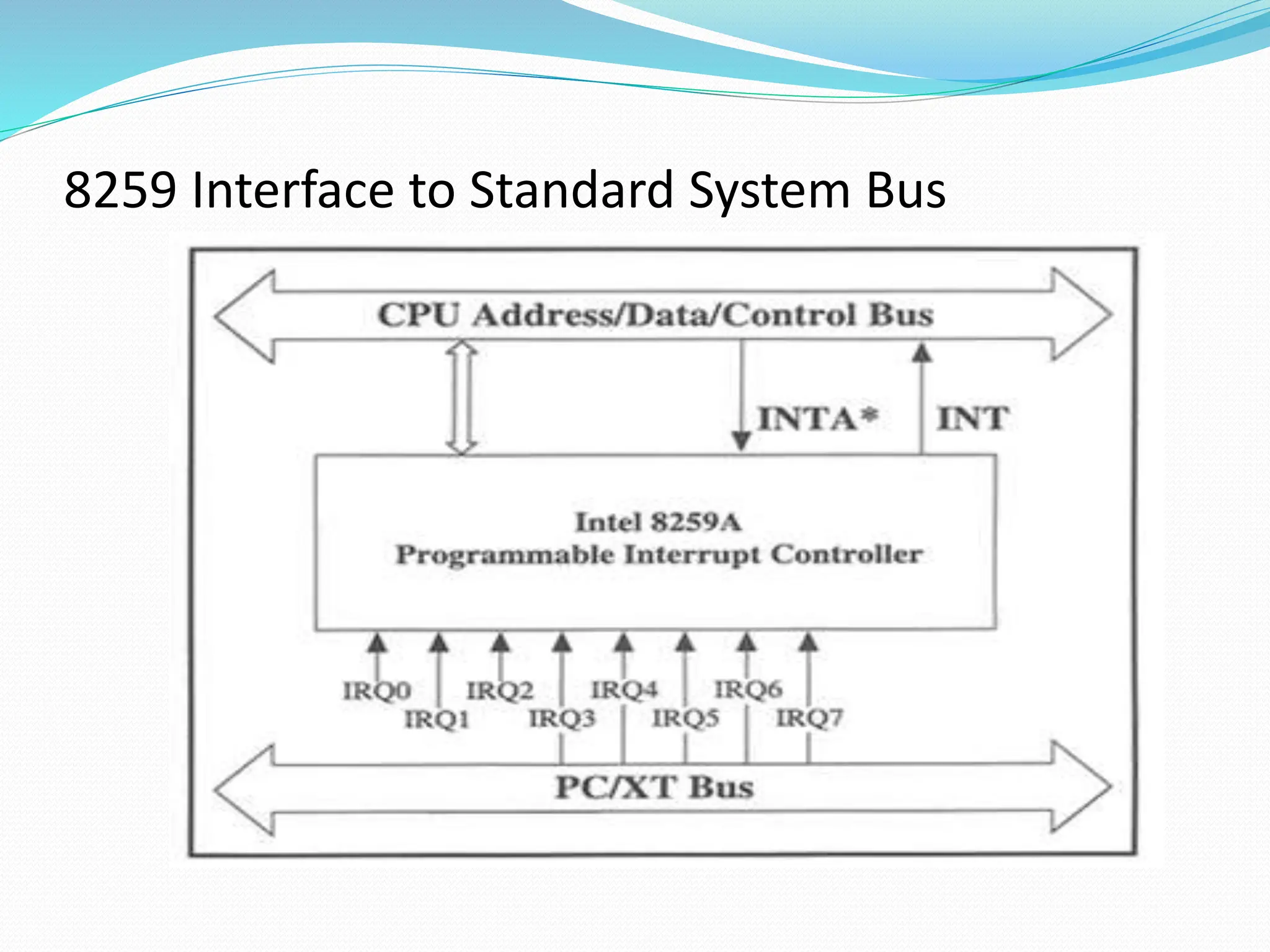

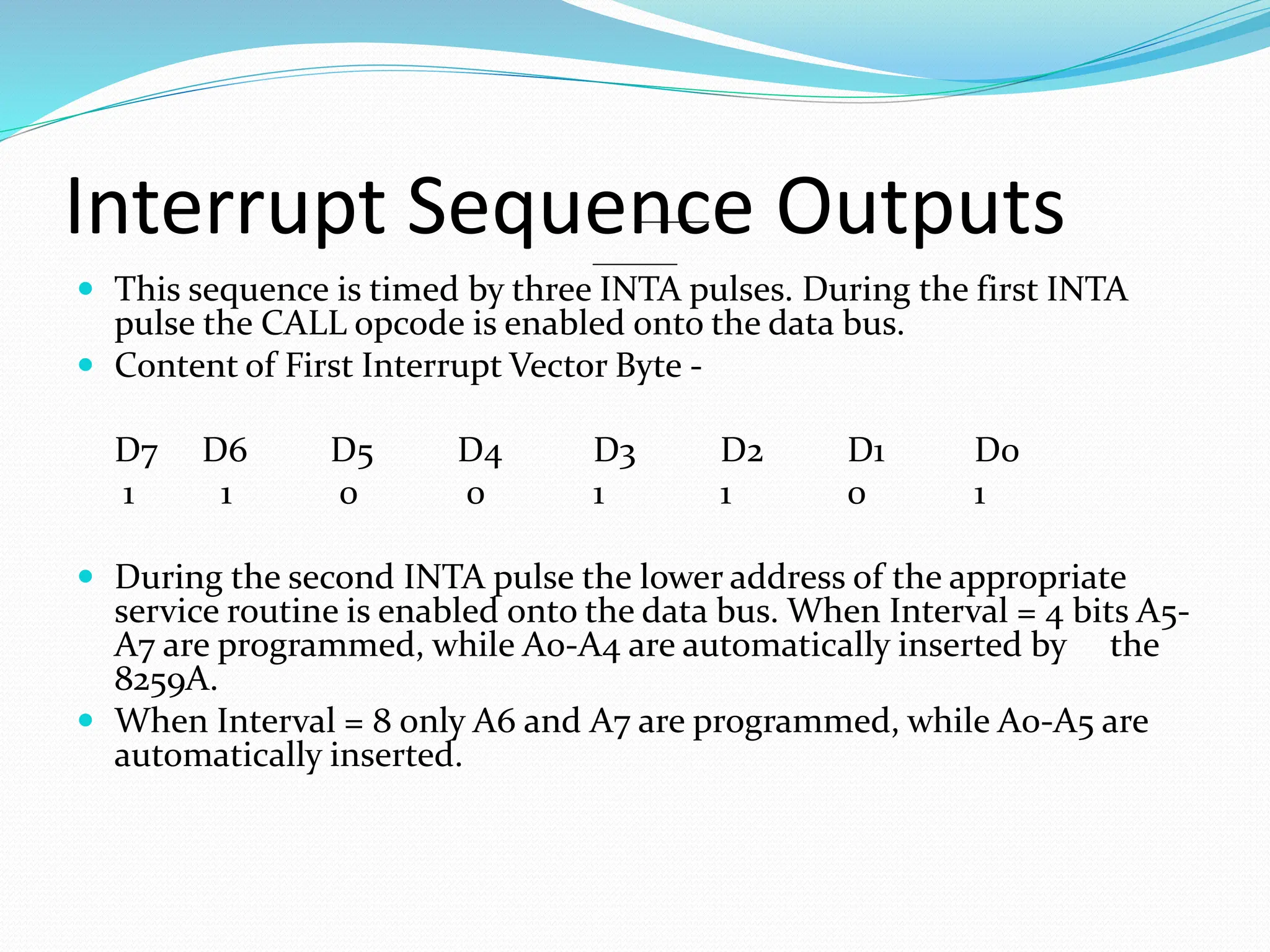

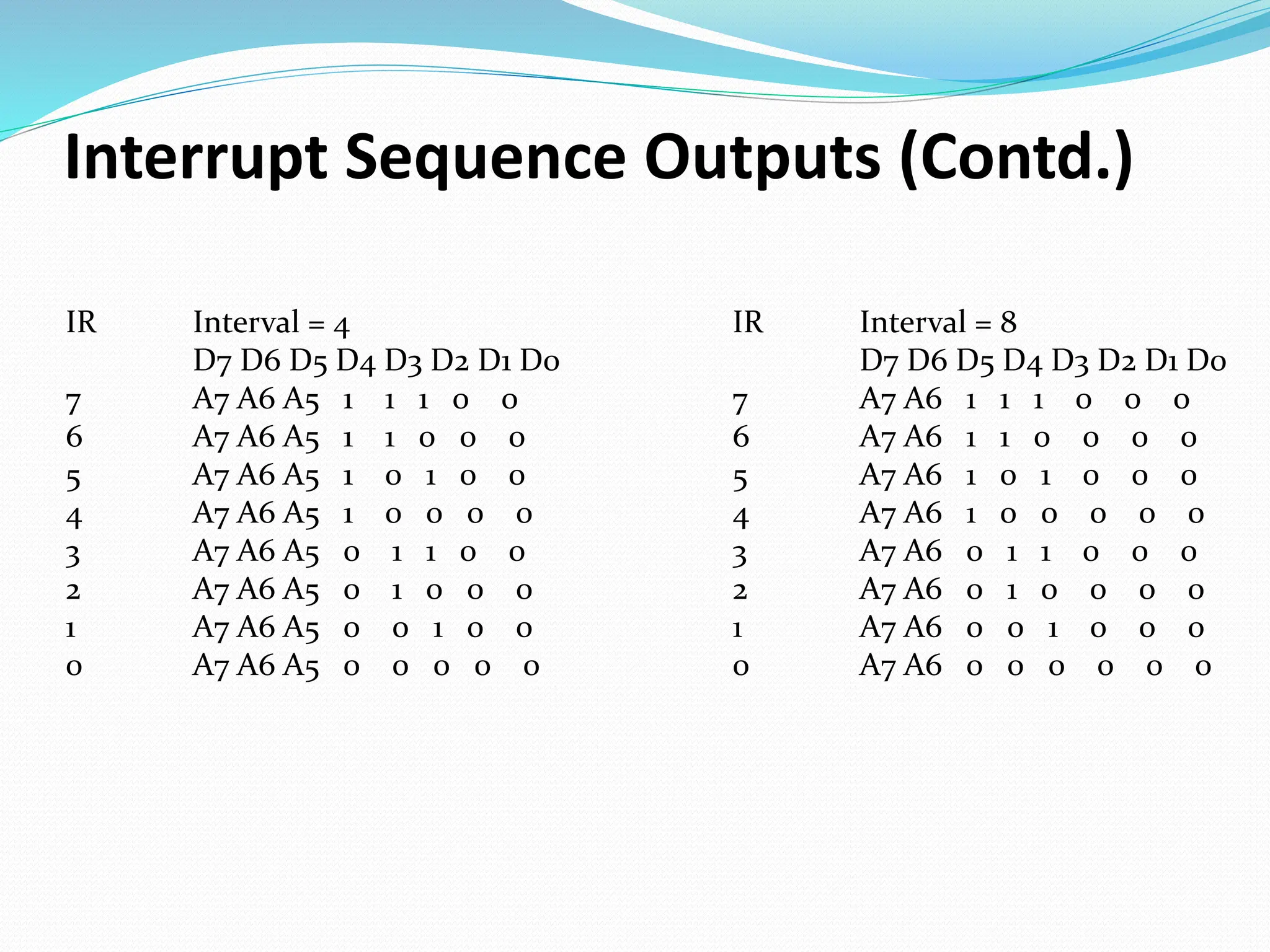

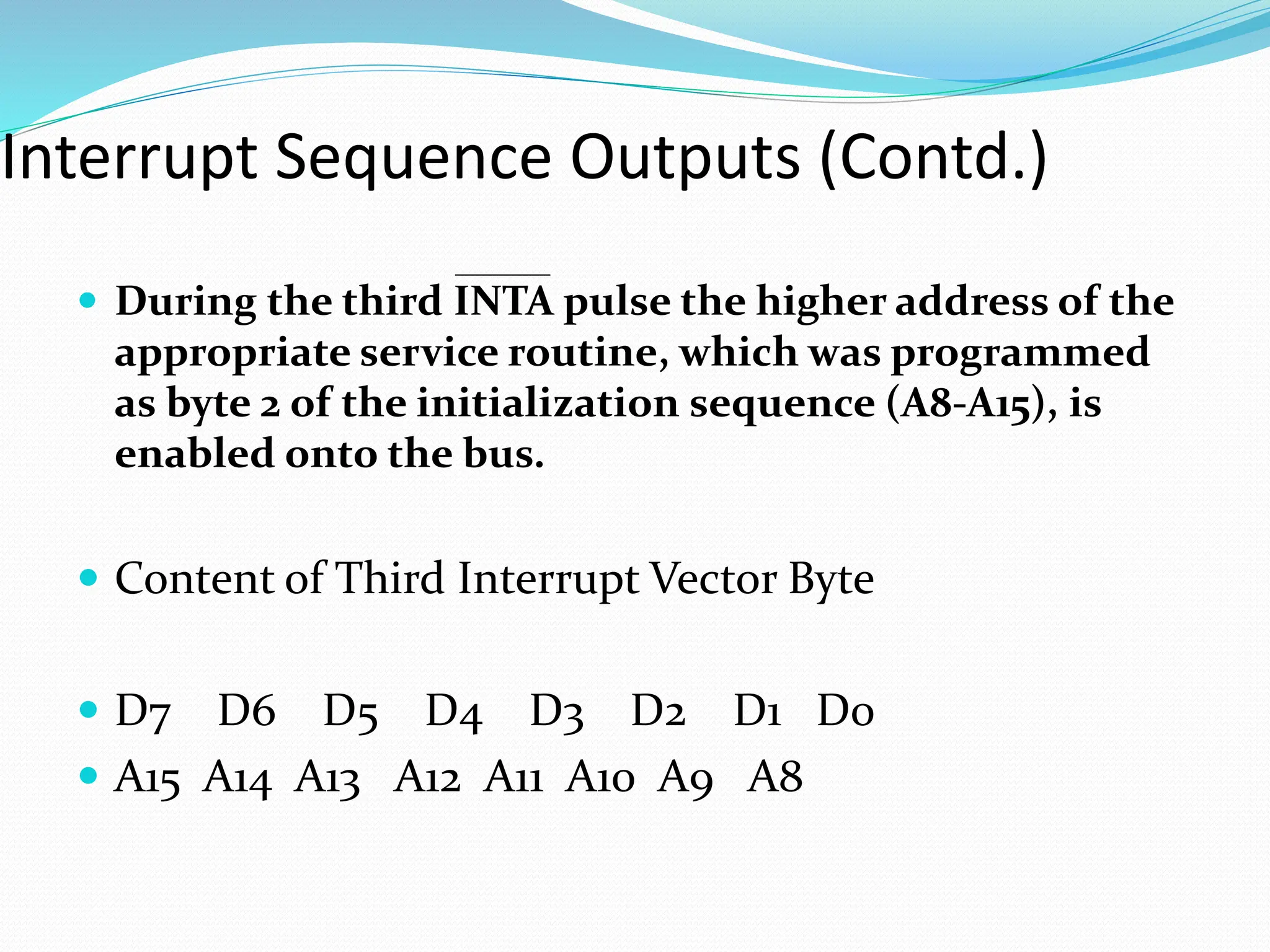

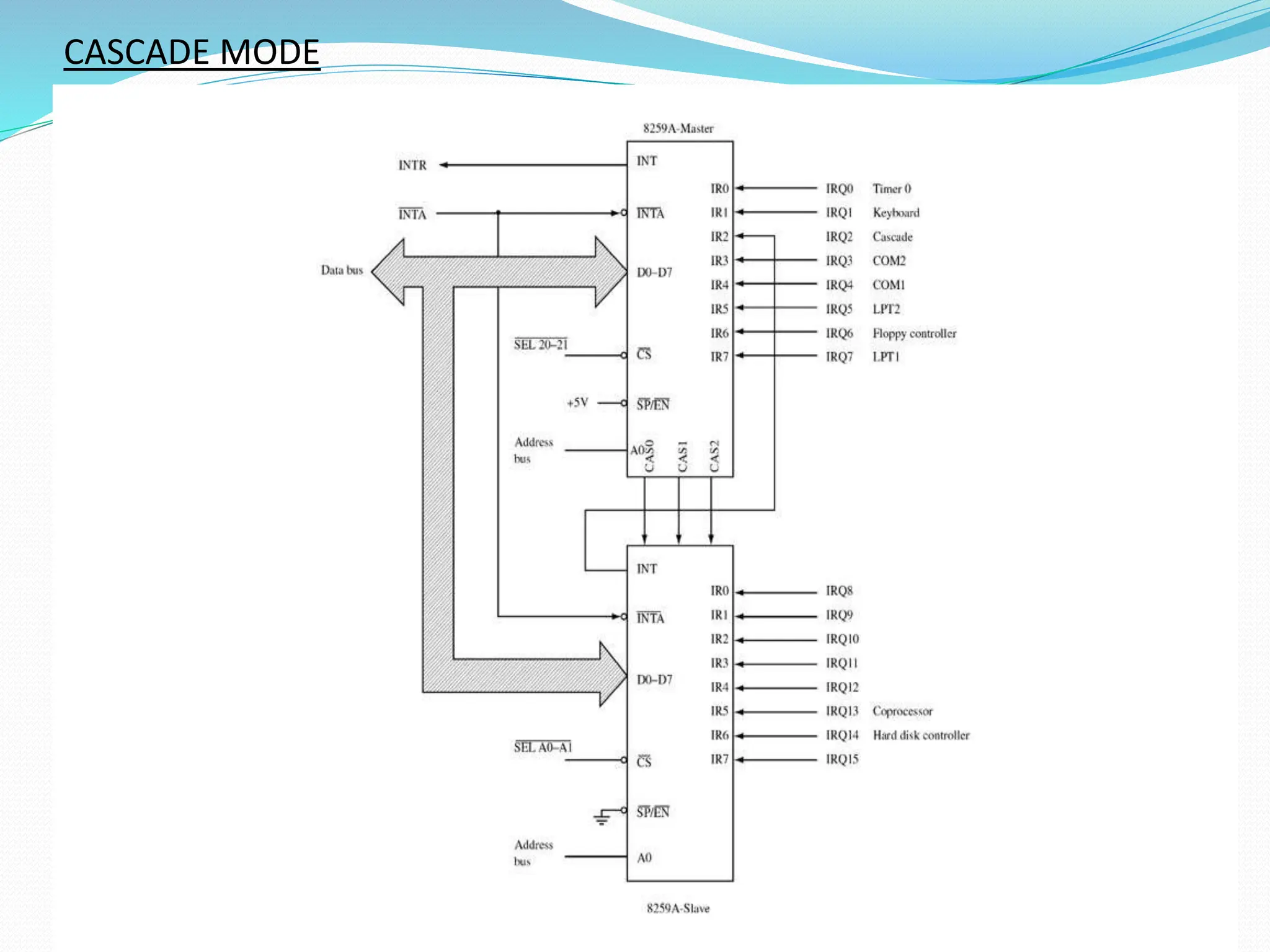

The 8259A is an interrupt controller that manages interrupt requests from peripheral devices connected to a microprocessor. It has 8 interrupt request lines that accept signals from devices. The 8259A prioritizes the interrupt requests, masks some if needed, and issues an interrupt signal to the CPU. It then provides the CPU with the address of the interrupt service routine for the highest priority active interrupt by placing the address bytes on the data bus over 3 interrupt acknowledge pulses from the CPU. This allows efficient interrupt-driven processing of device requests.