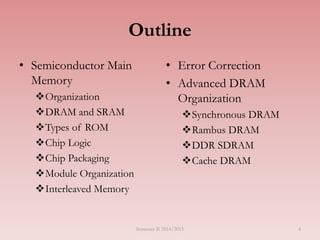

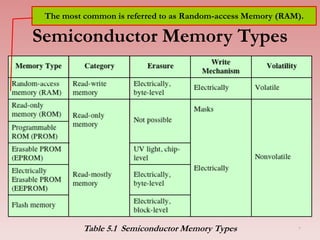

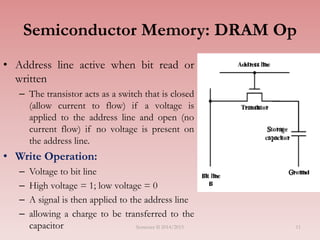

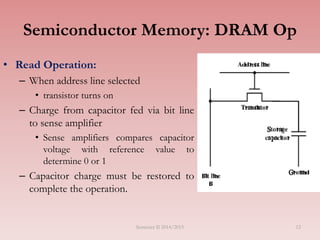

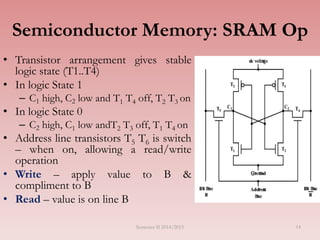

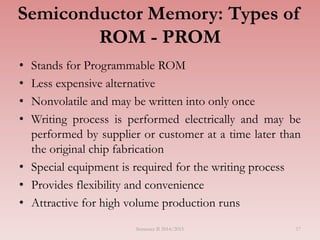

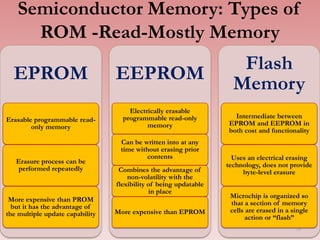

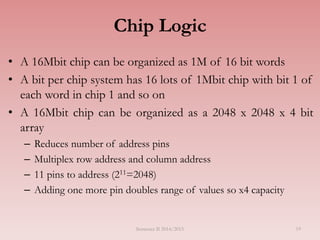

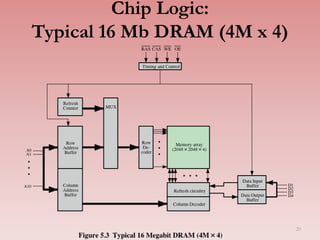

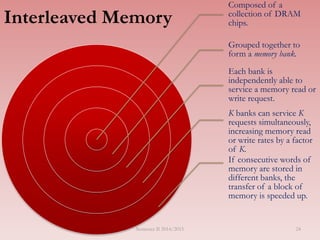

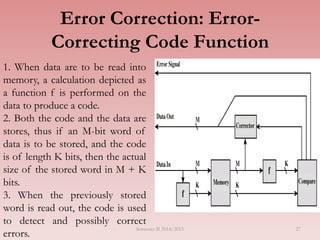

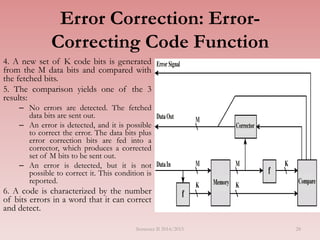

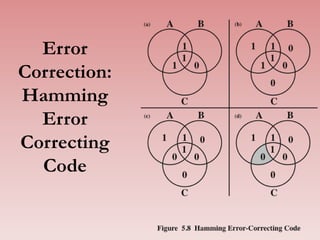

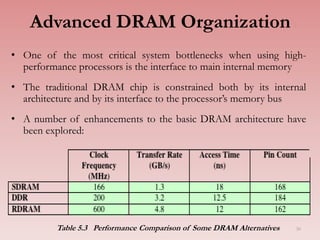

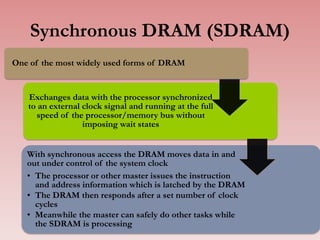

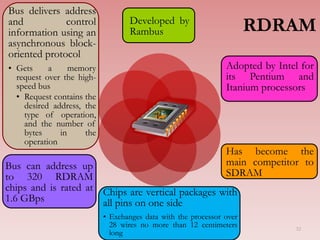

This document discusses internal memory organization and technologies. It begins with an overview of memory cell operation for DRAM and SRAM. It then covers various memory types including DRAM, SRAM, ROM, PROM, EPROM, and EEPROM. Advanced DRAM technologies like synchronous DRAM, Rambus DRAM, and double data rate SDRAM are also summarized. The document concludes with sections on error correction techniques and cache DRAM.