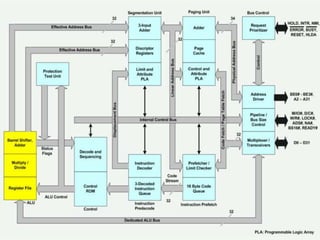

The 80386 processor architecture is divided into three sections - the central processing unit (CPU), memory management unit (MMU), and bus interface unit (BIU). The CPU contains an execution unit with registers for handling data and calculating offsets, and an instruction unit that decodes instructions. The MMU manages memory using segmentation and paging, dividing physical memory into pages and virtual memory into segments and pages. It provides protection of system code and data. The BUI controls access to the system bus. The 80386 also features eight 32-bit general purpose registers that can be used as 16-bit registers, along with extended 32-bit versions of the BP, SP, SI, and DI registers.