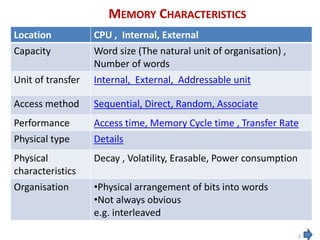

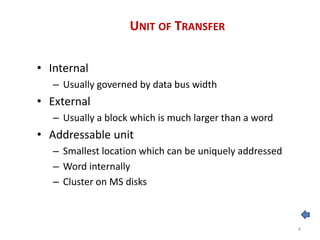

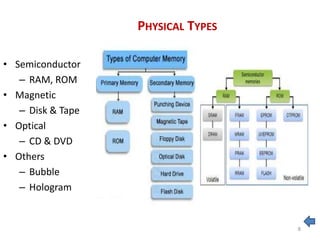

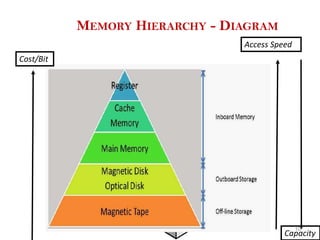

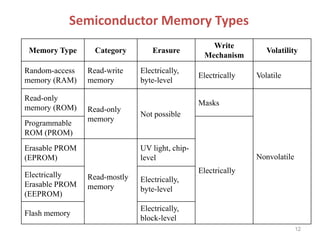

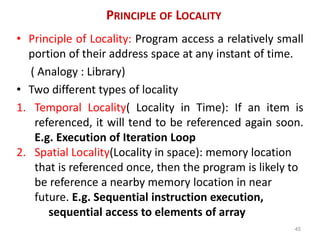

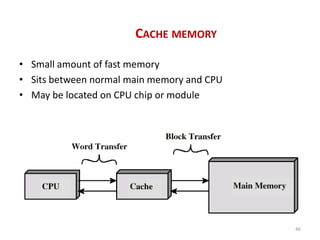

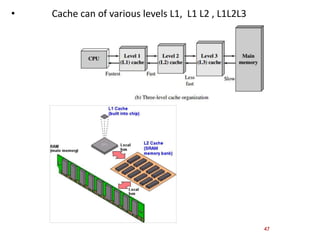

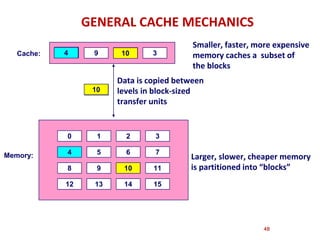

Memory is a device used to store data or programs either temporarily or permanently for use in a computer. There are different types of memory based on their characteristics such as location, capacity, unit of transfer, access method, performance, physical type and organization. Common memory types include RAM, ROM, and external memory such as magnetic disks. The memory hierarchy consists of registers, cache, main memory and external storage. Cache memory uses the principle of locality to improve memory access time by storing recently accessed data from main memory.