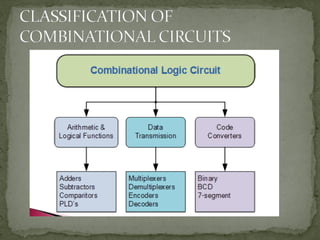

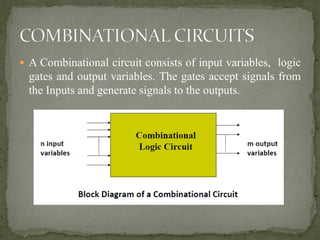

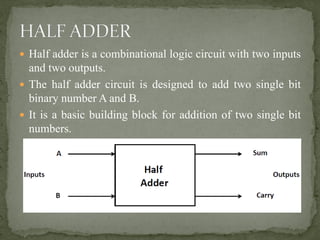

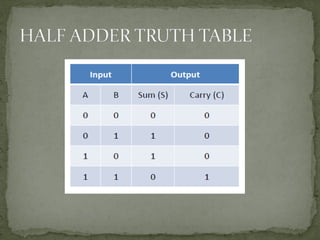

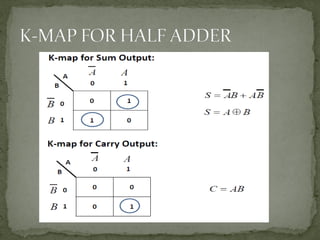

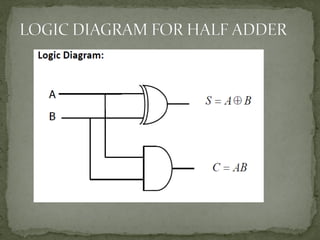

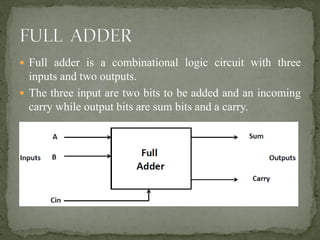

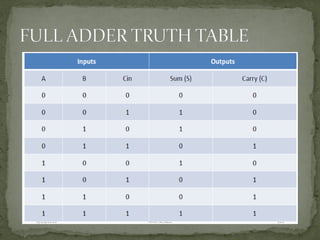

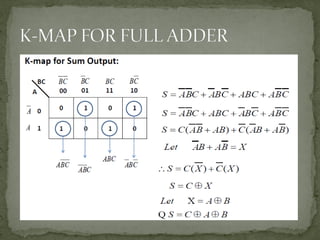

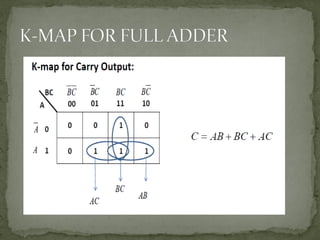

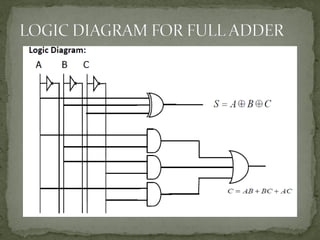

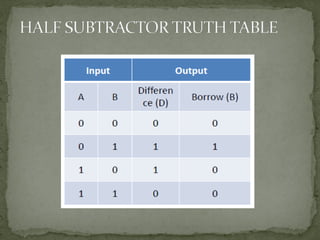

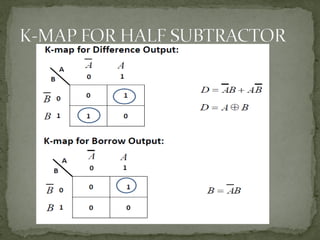

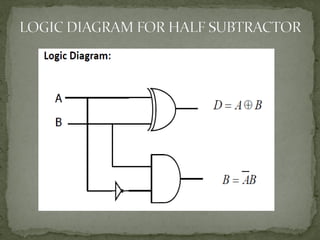

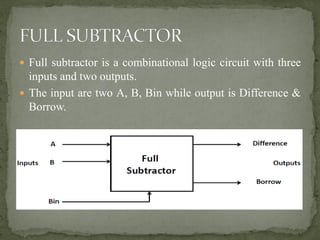

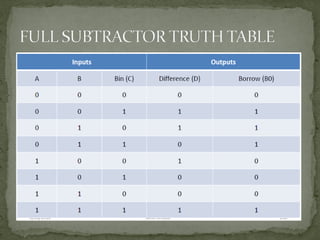

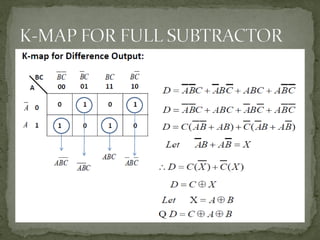

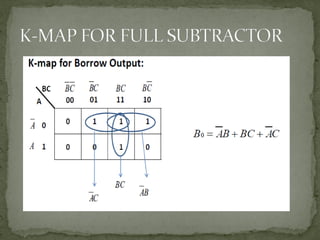

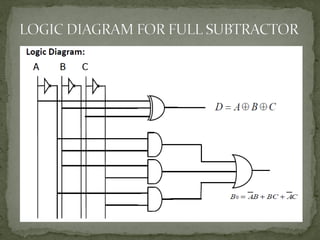

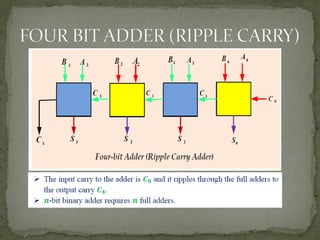

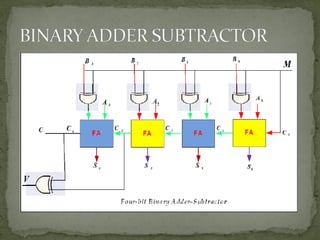

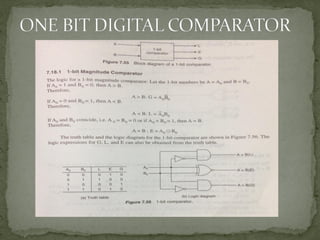

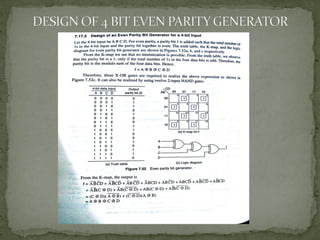

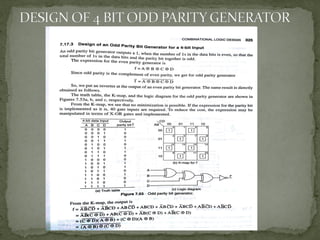

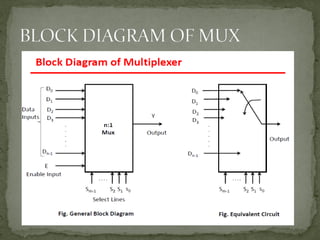

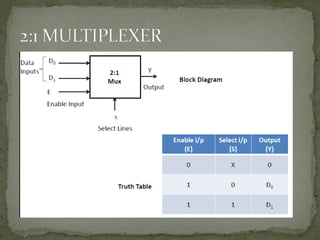

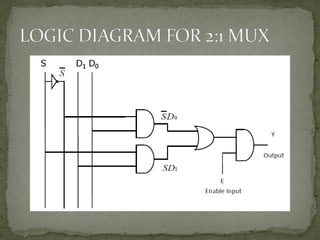

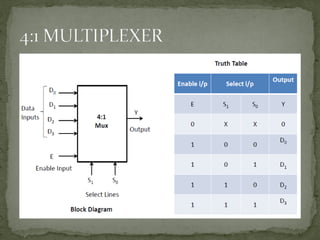

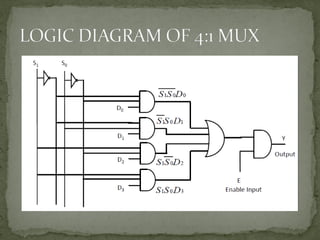

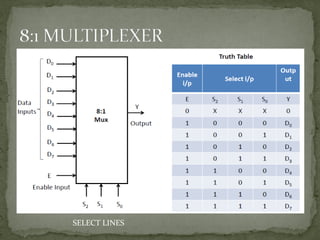

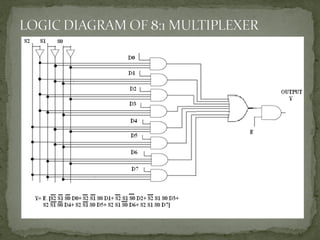

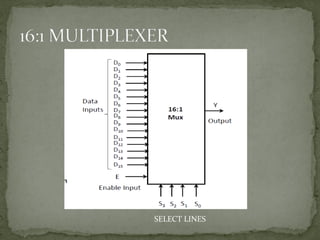

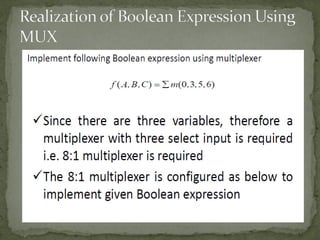

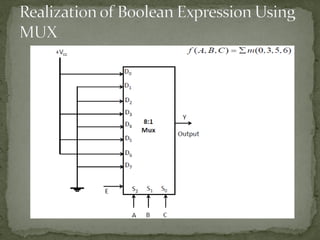

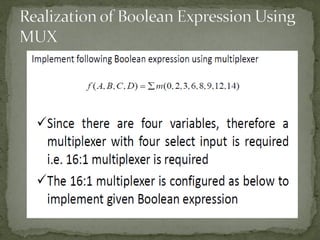

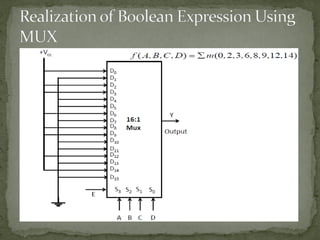

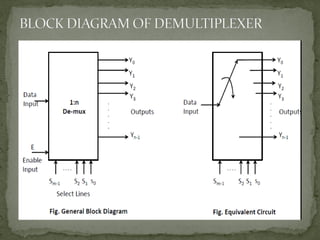

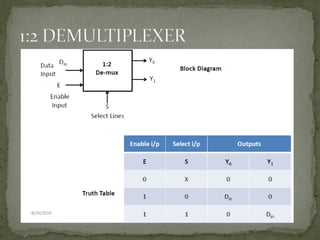

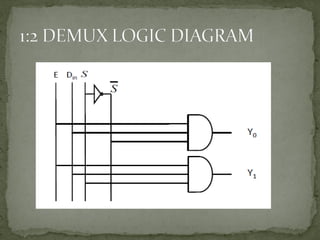

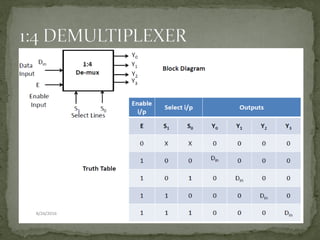

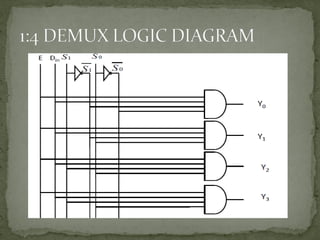

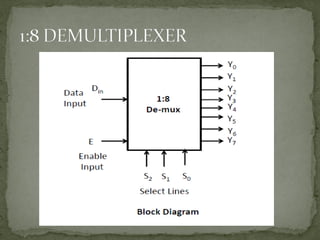

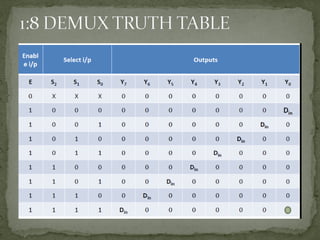

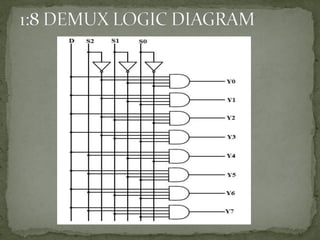

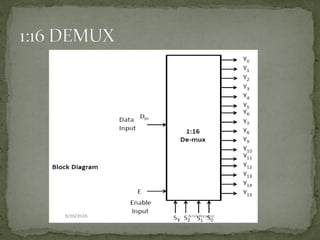

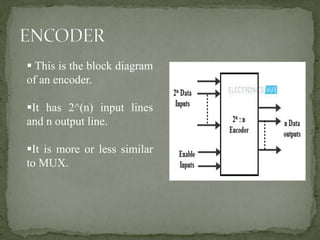

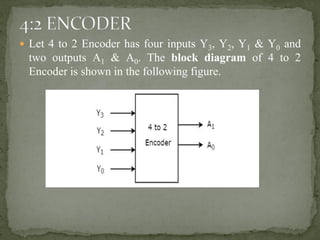

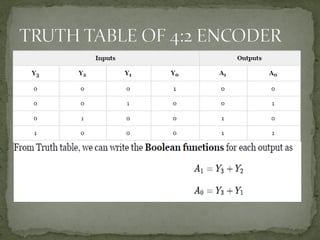

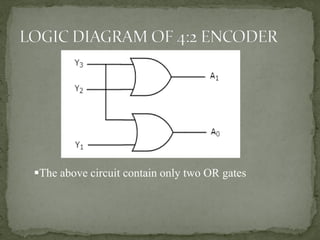

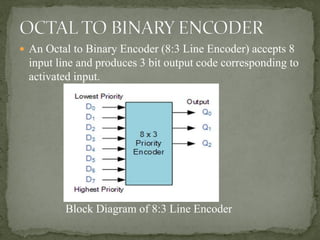

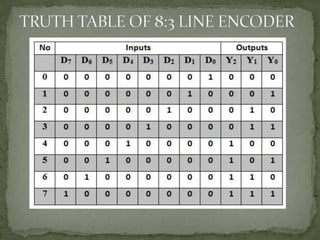

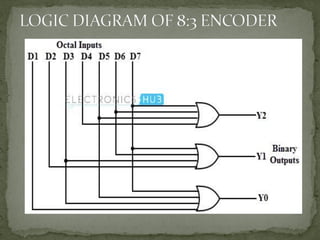

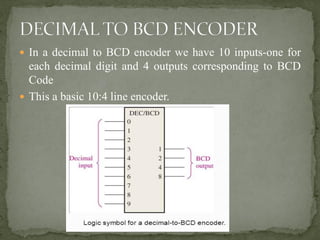

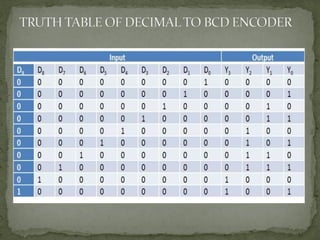

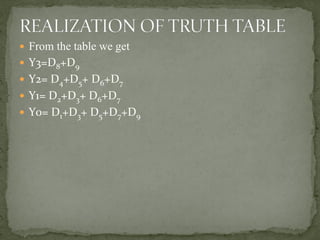

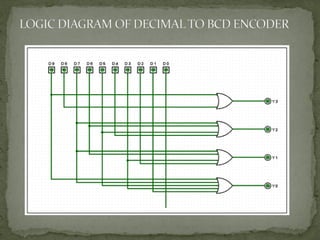

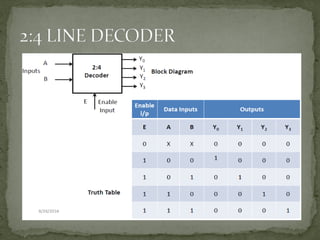

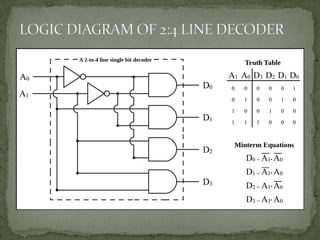

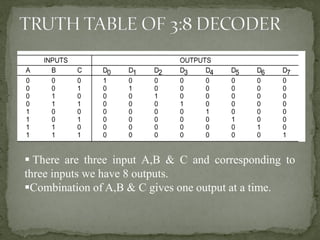

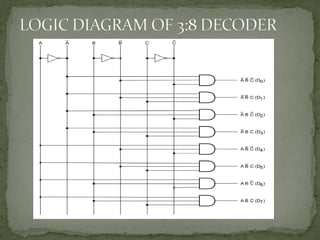

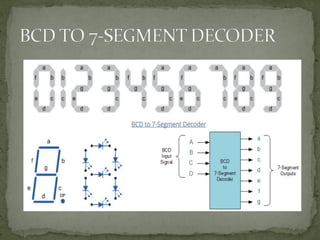

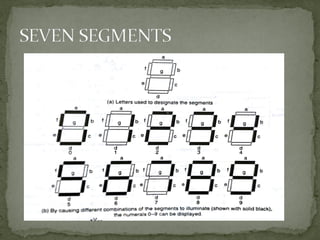

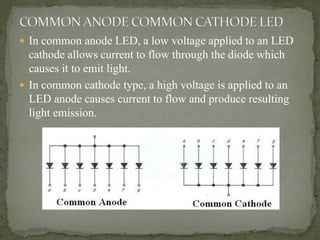

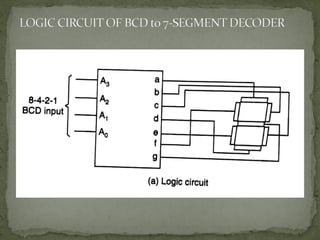

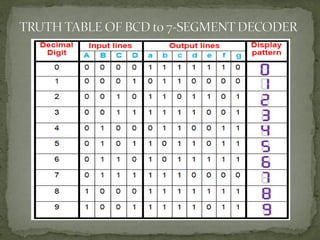

The document discusses digital circuits including combinational and sequential circuits. It describes various combinational logic circuits such as half adders, full adders, comparators, multiplexers, encoders, decoders. It also discusses sequential circuits and how they employ memory elements. Arithmetic circuits, binary adders, subtractors, and BCD to 7-segment decoders are explained in detail through diagrams and examples.