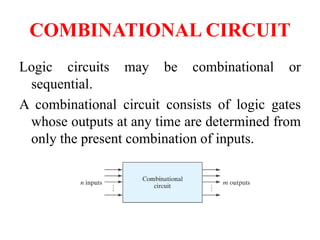

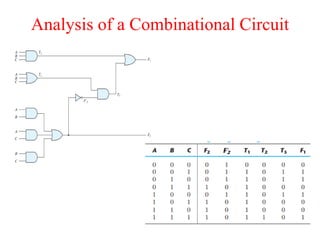

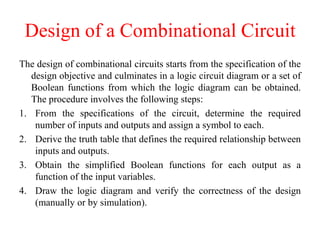

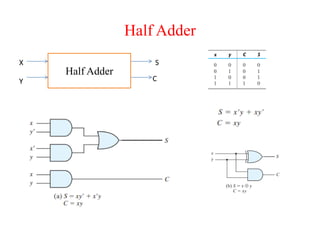

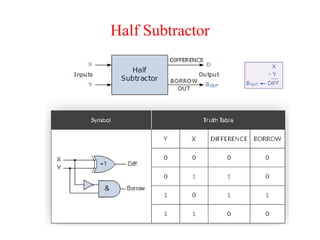

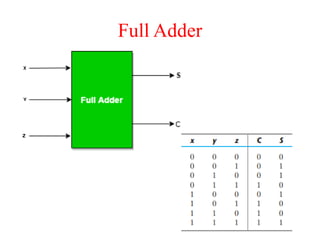

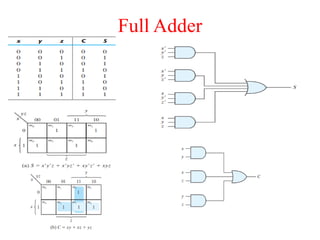

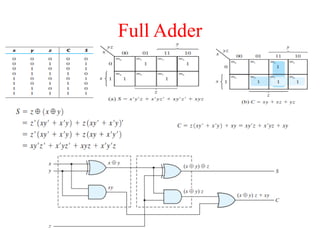

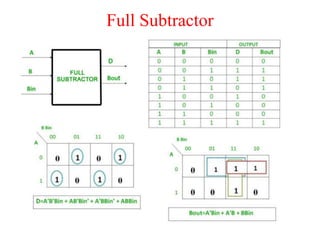

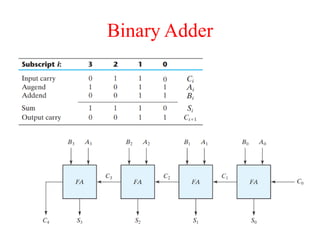

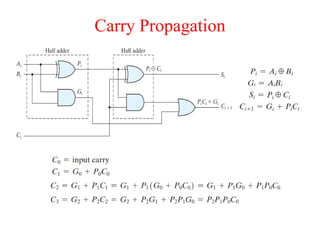

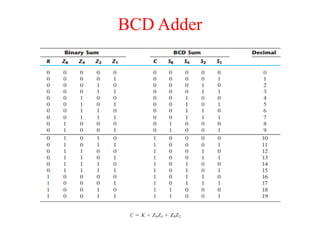

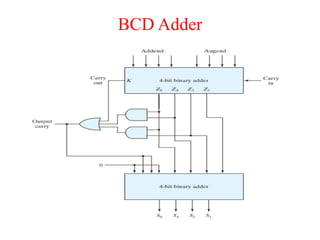

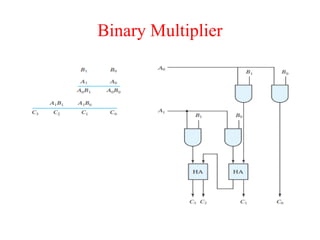

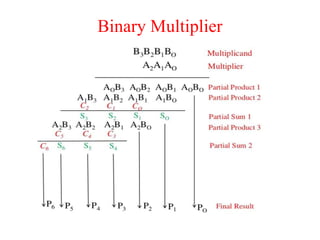

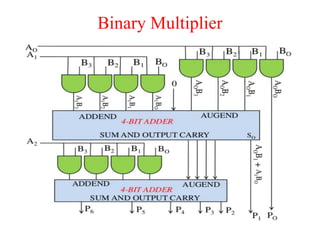

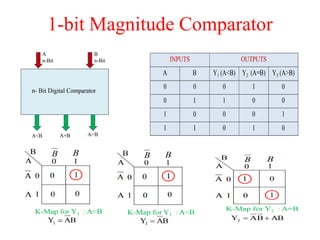

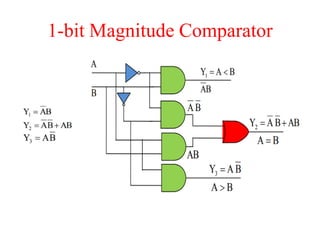

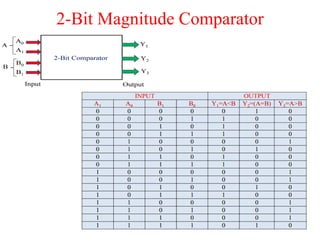

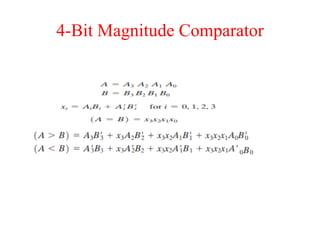

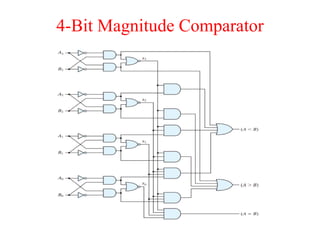

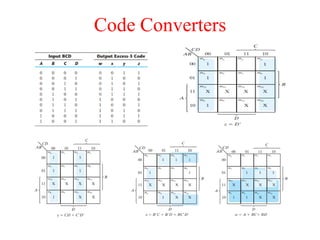

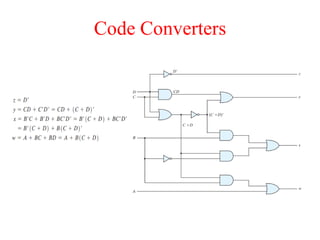

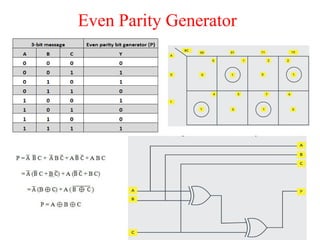

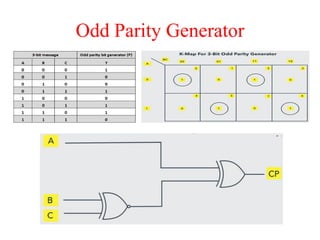

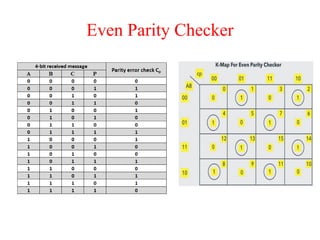

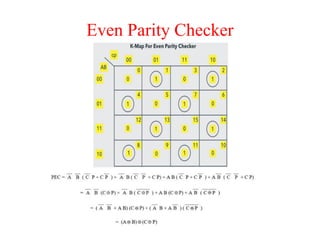

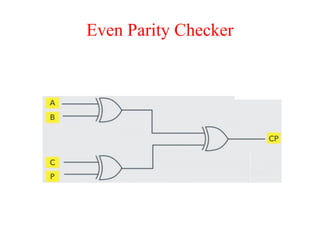

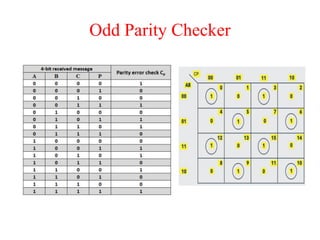

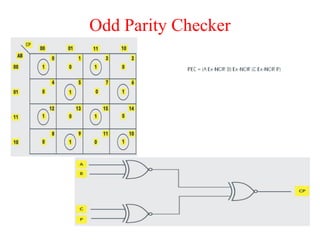

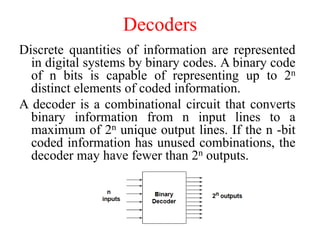

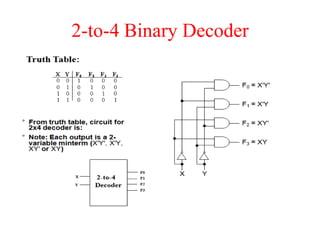

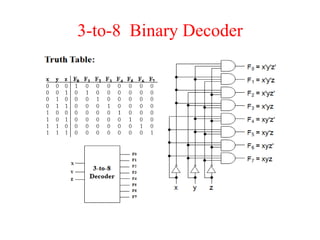

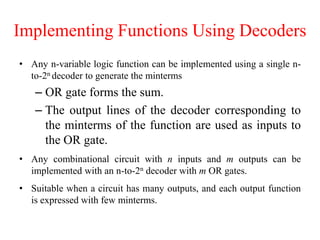

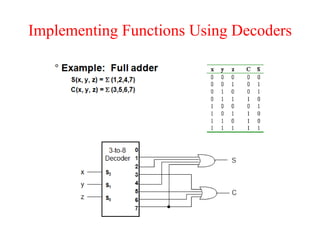

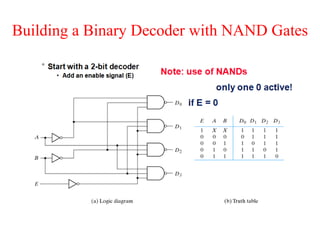

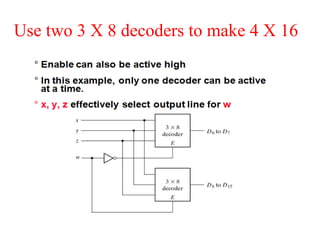

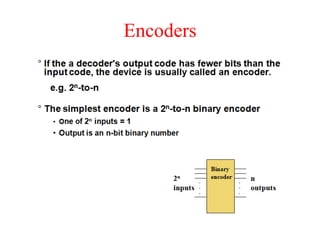

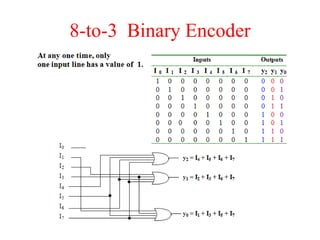

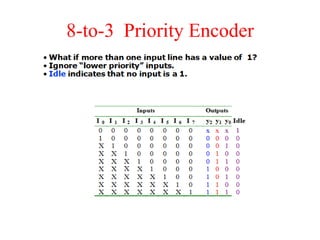

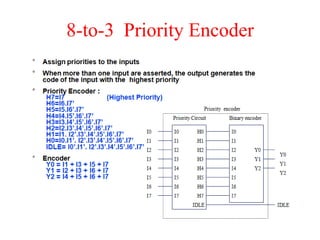

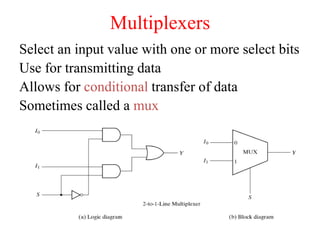

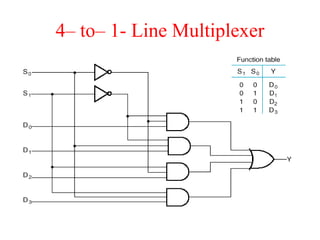

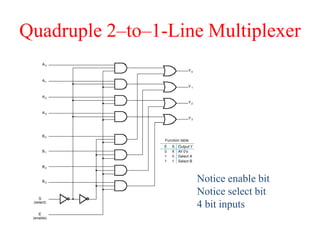

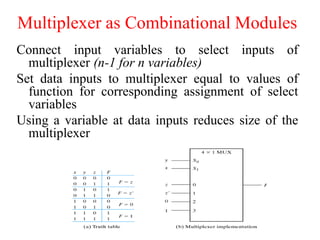

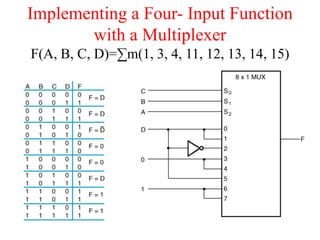

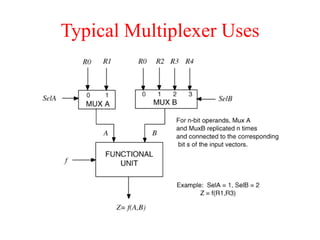

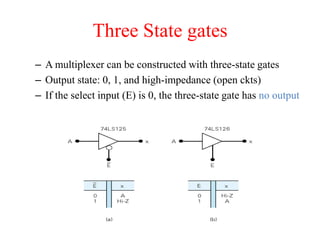

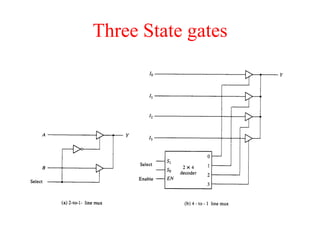

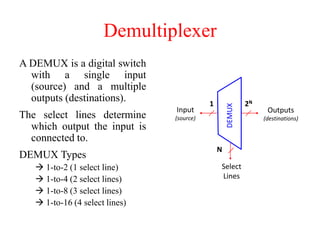

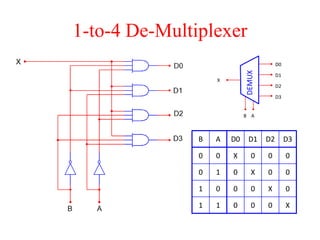

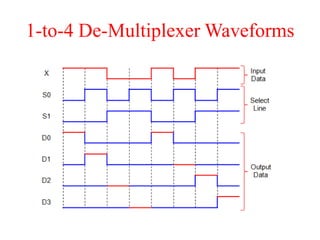

The document presents a course outline for digital electronics, focusing on digital fundamentals, combinational circuit design, and sequential circuits. Key topics include the analysis and design of various logic circuits such as adders, comparators, encoders, and multiplexers. It also covers the implementation of functions using decoders and the roles of parity generators and checkers in error detection.