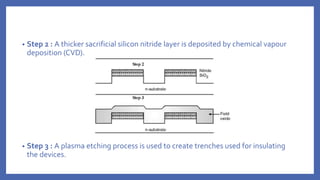

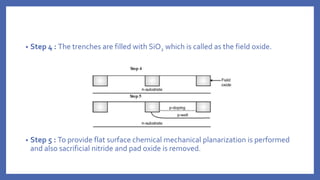

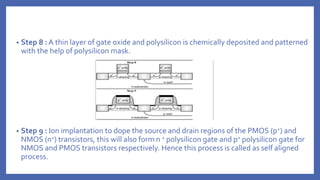

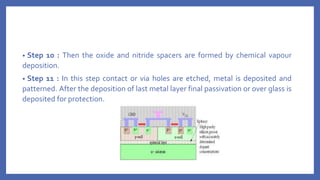

The document outlines the p-well process for CMOS fabrication, emphasizing its steps which parallel the n-well process with key modifications. It details processes such as the deposition of layers, trench creation, implantation, and doping to form pMOS and nMOS transistors. Overall, the p-well method is described as a technique for enhancing transistor performance with a focus on power dissipation and circuit speed.