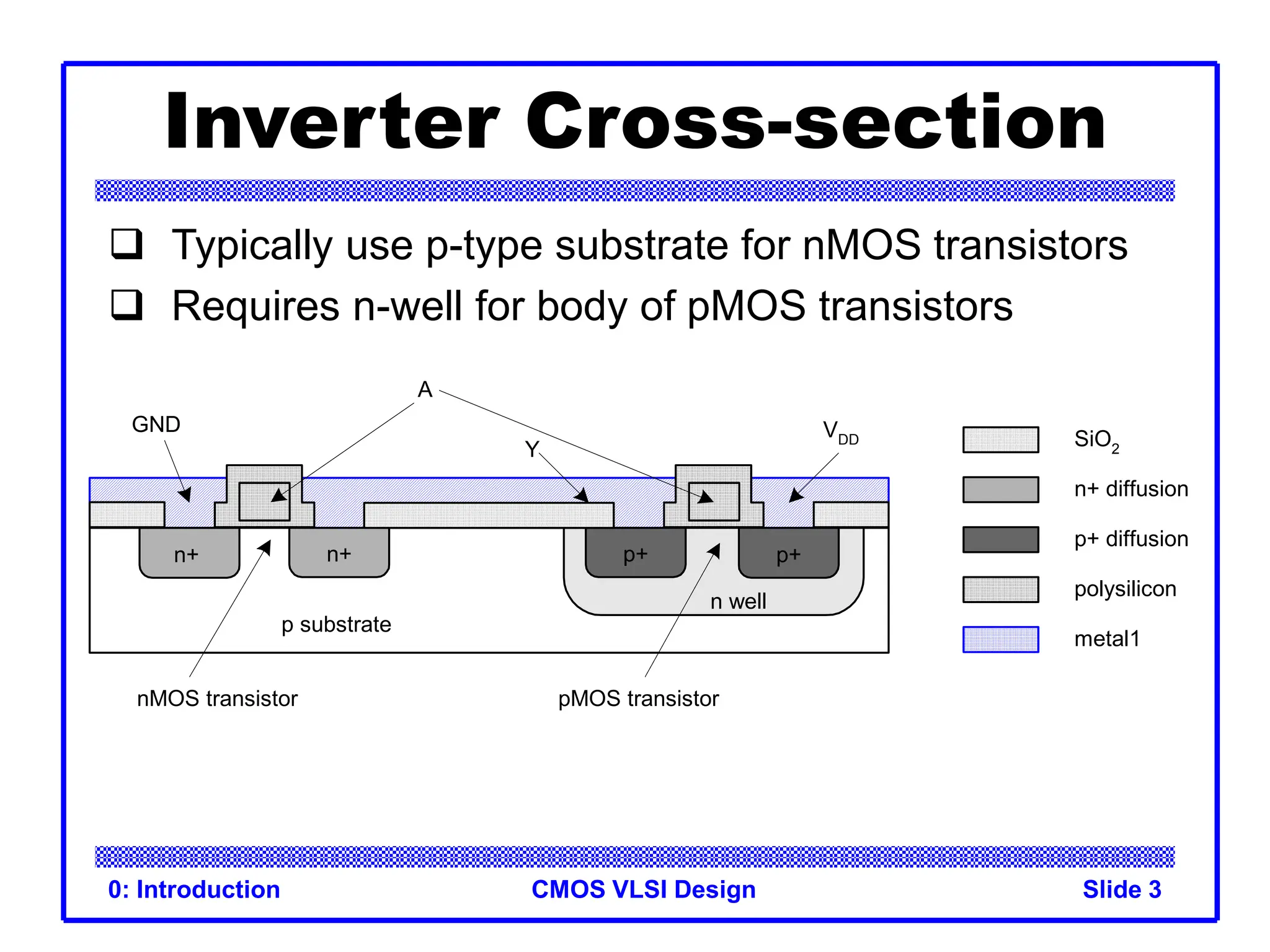

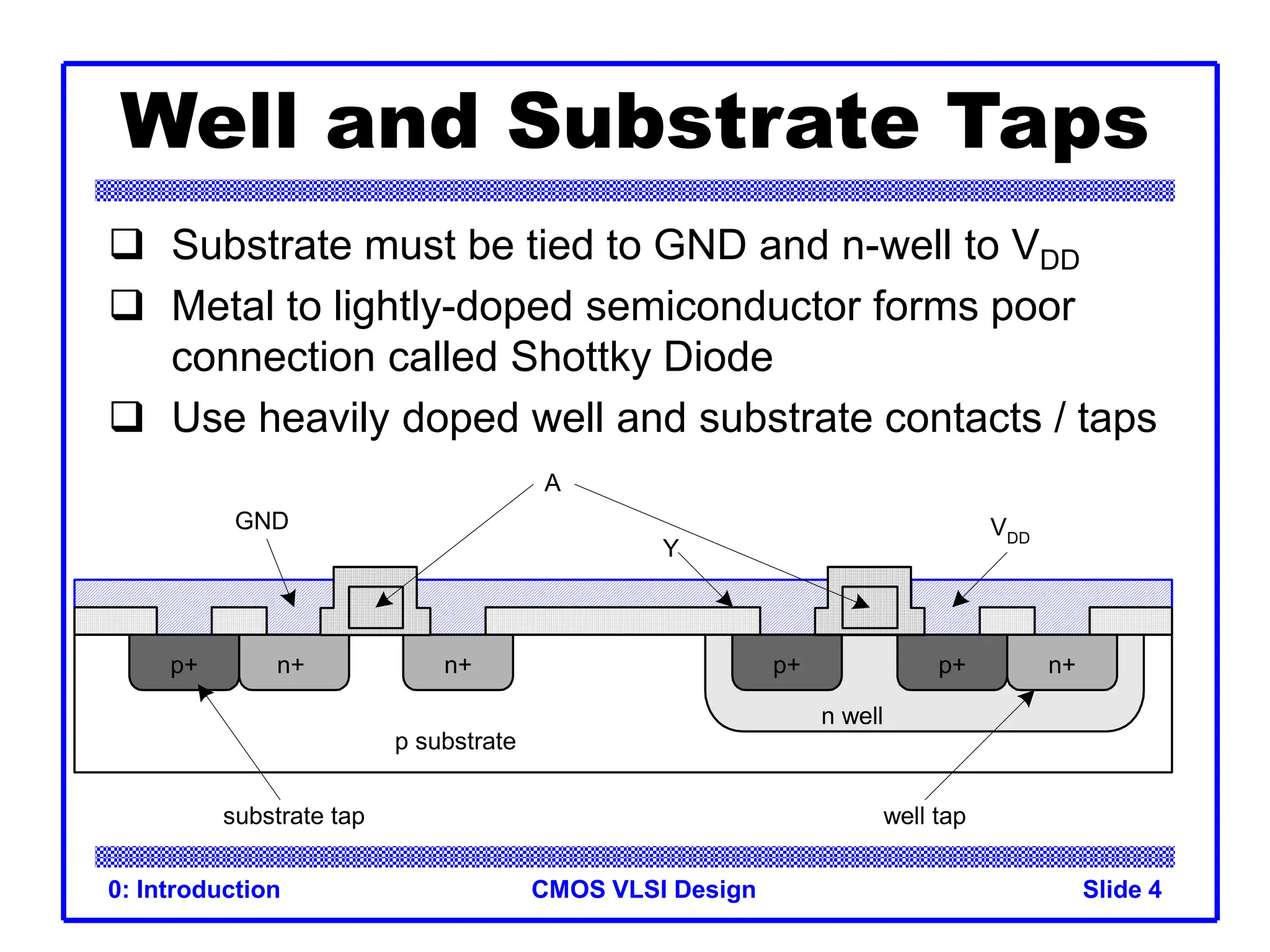

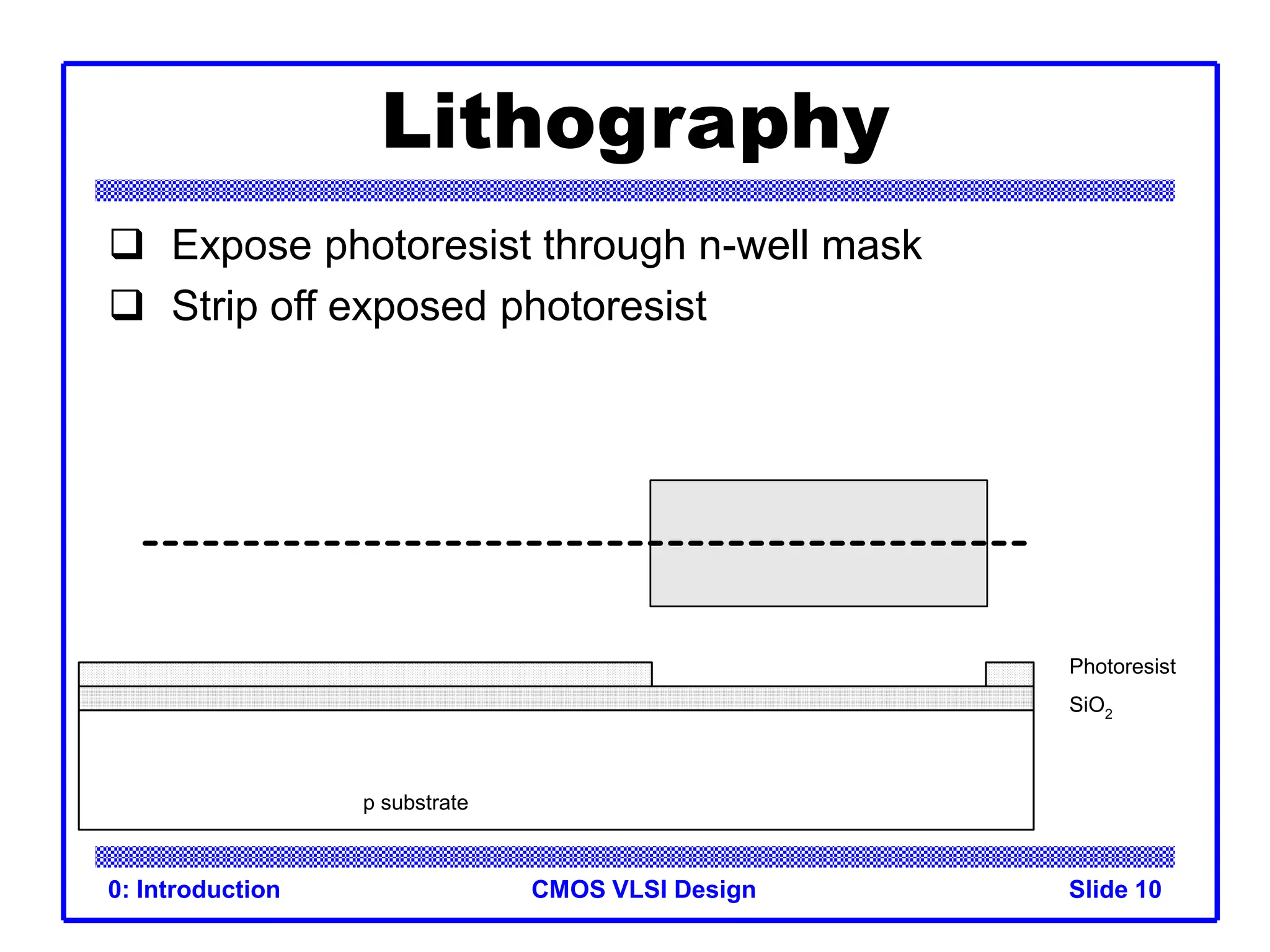

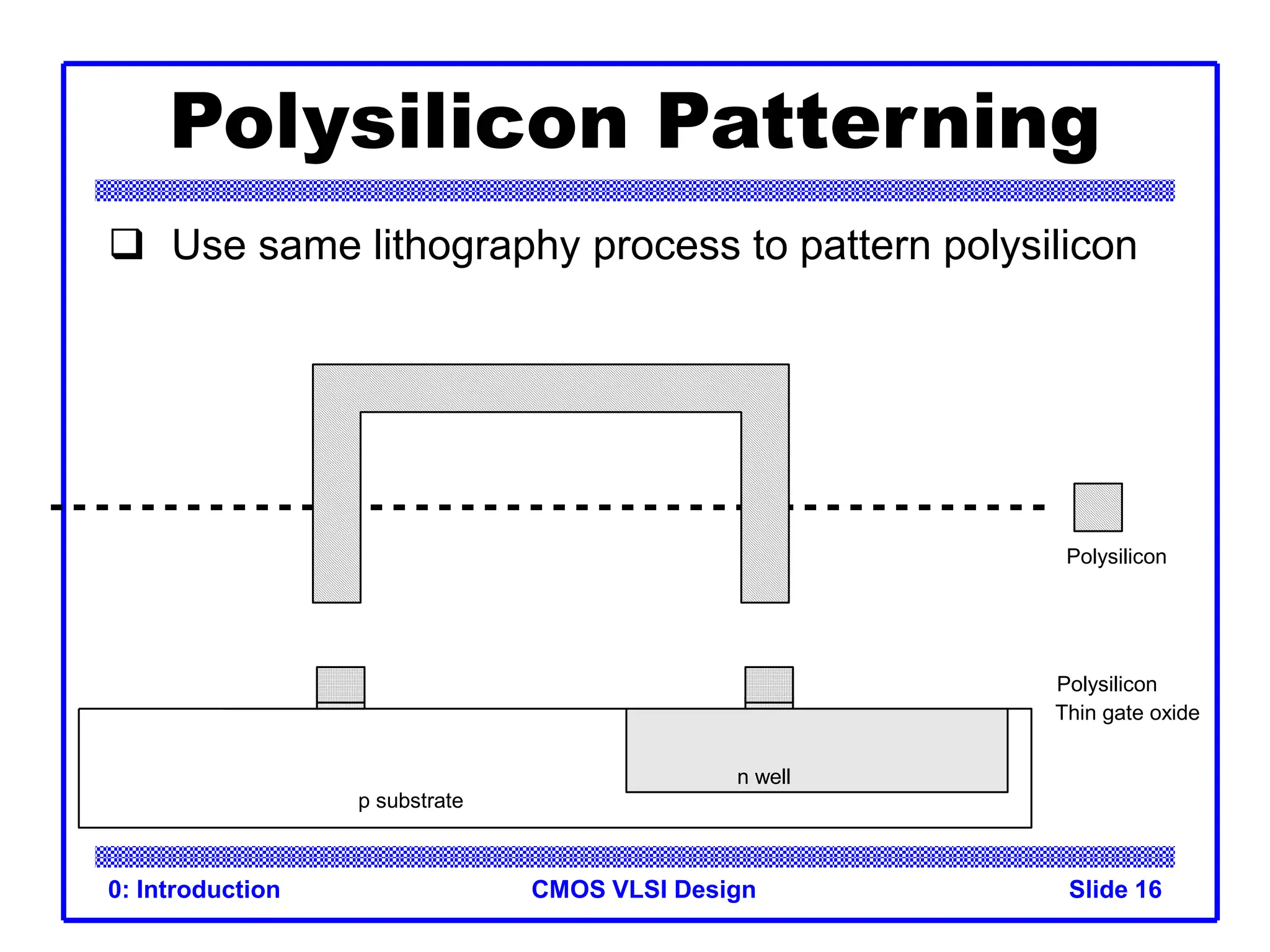

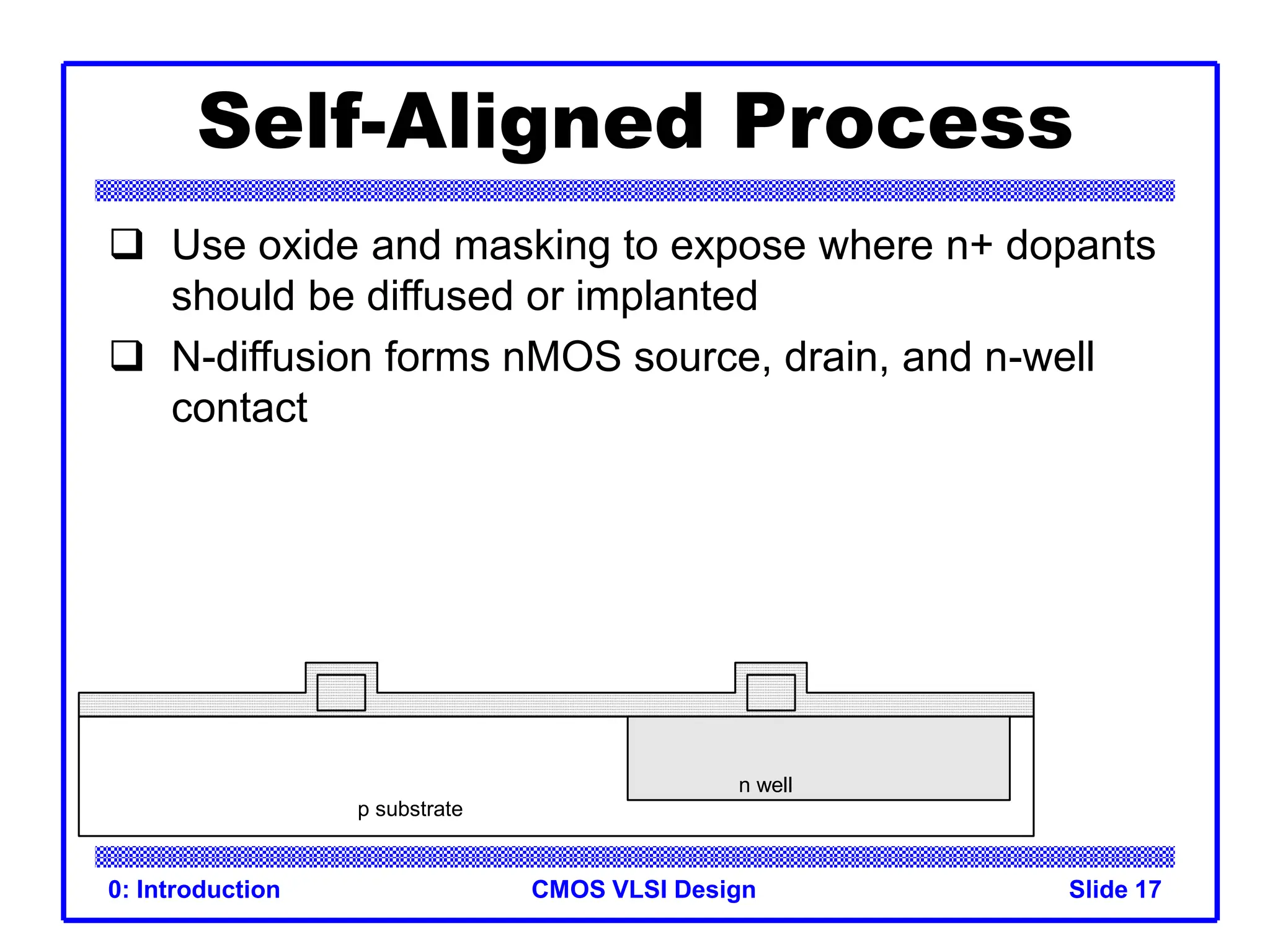

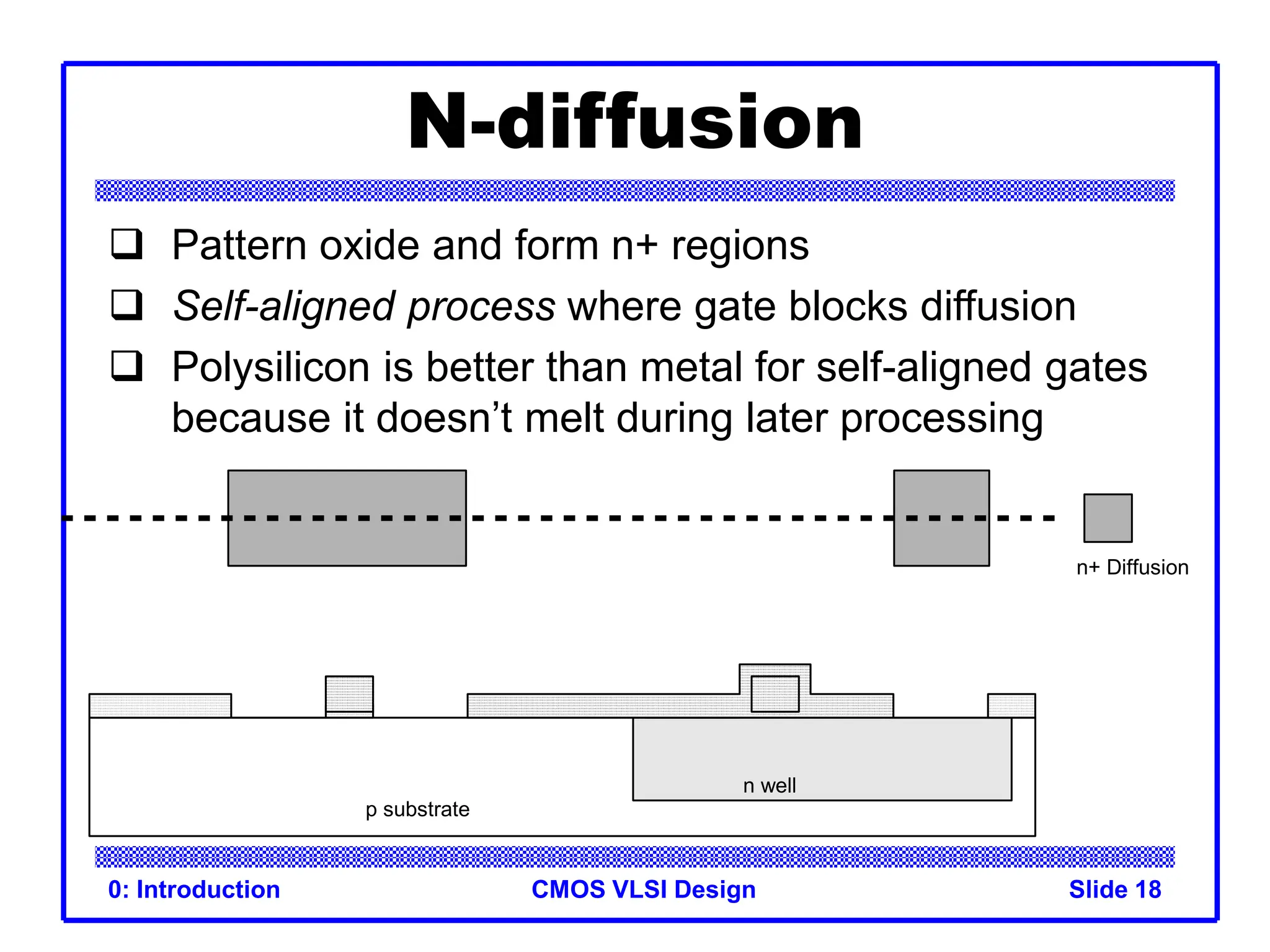

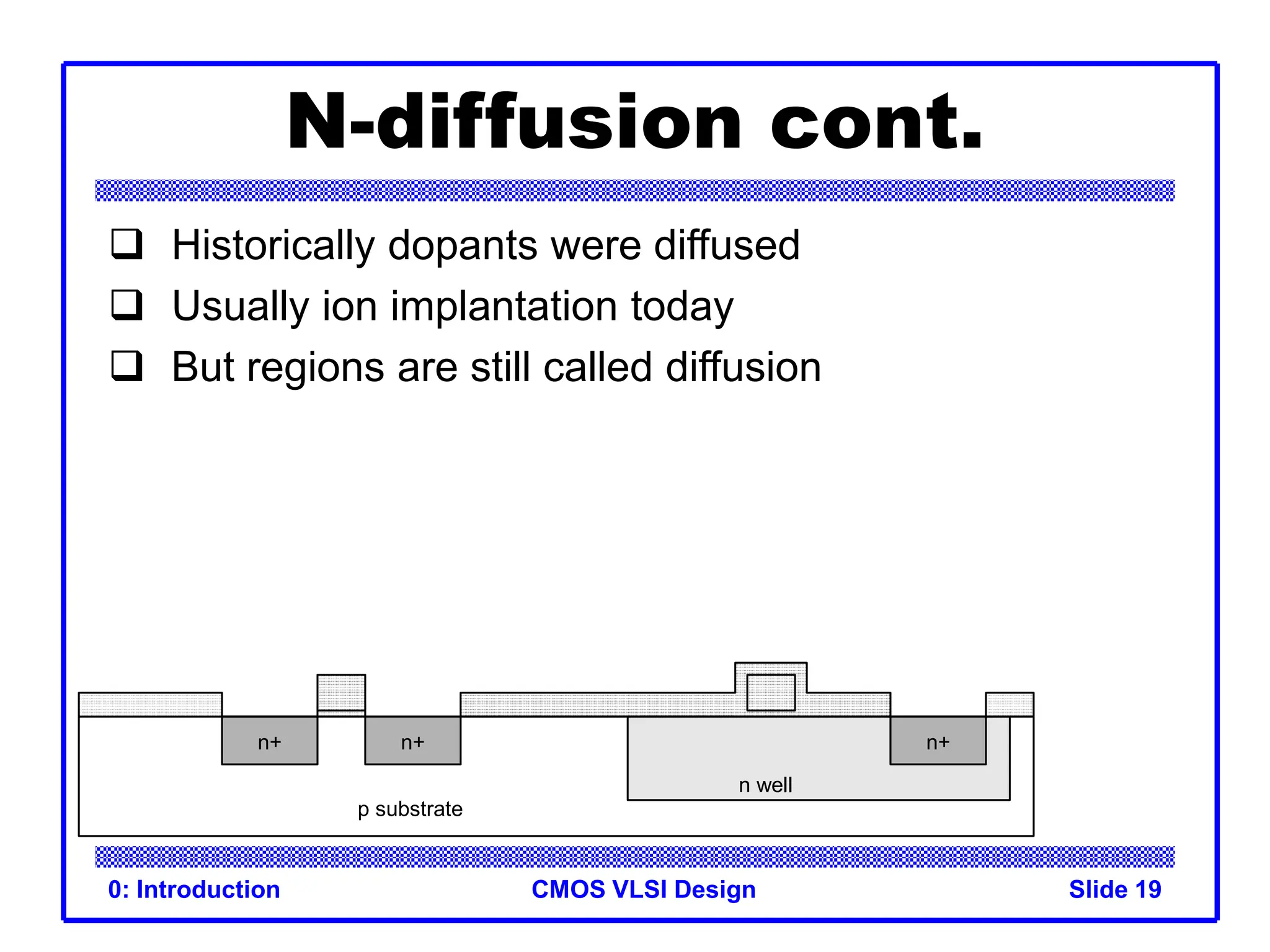

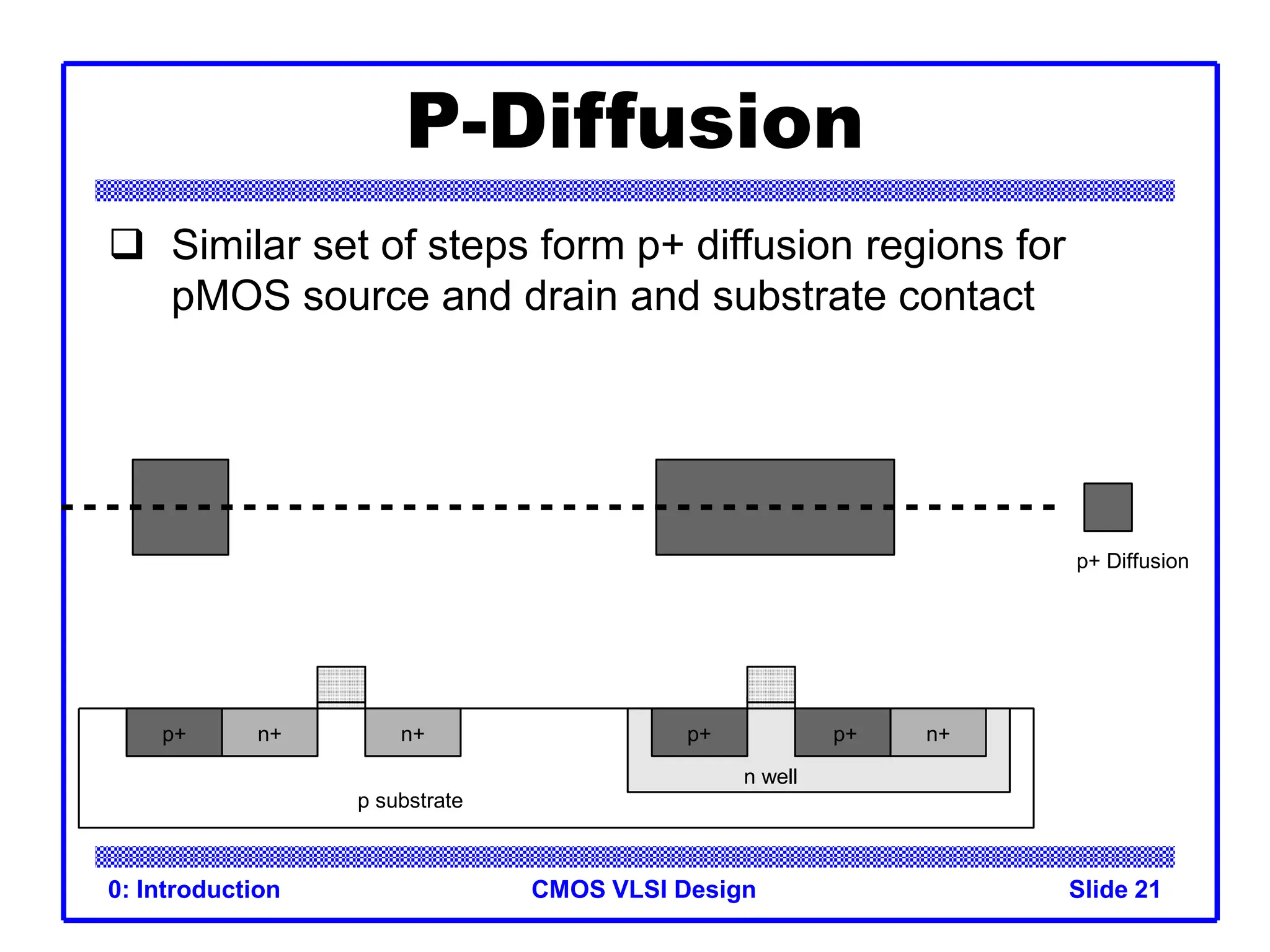

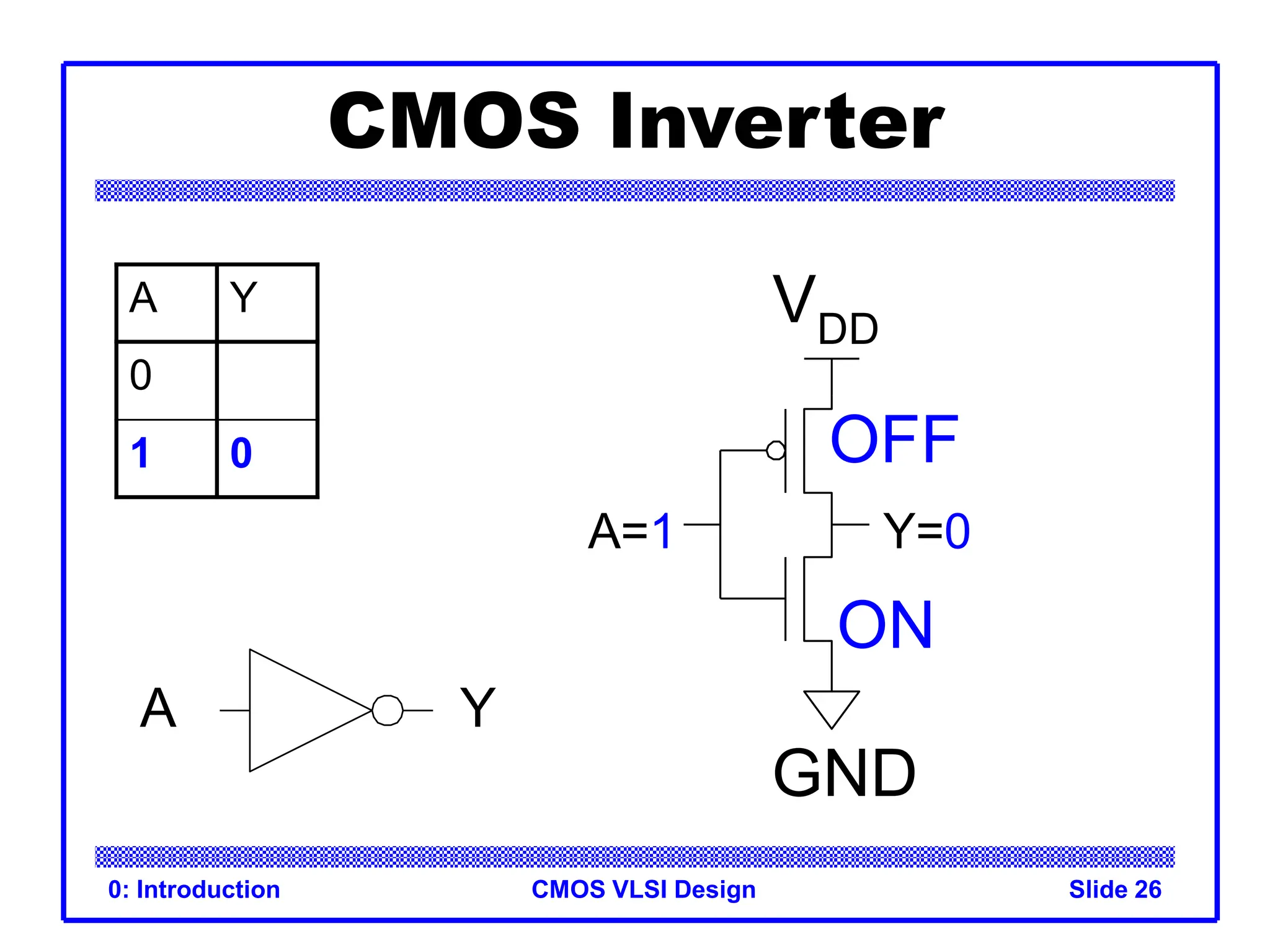

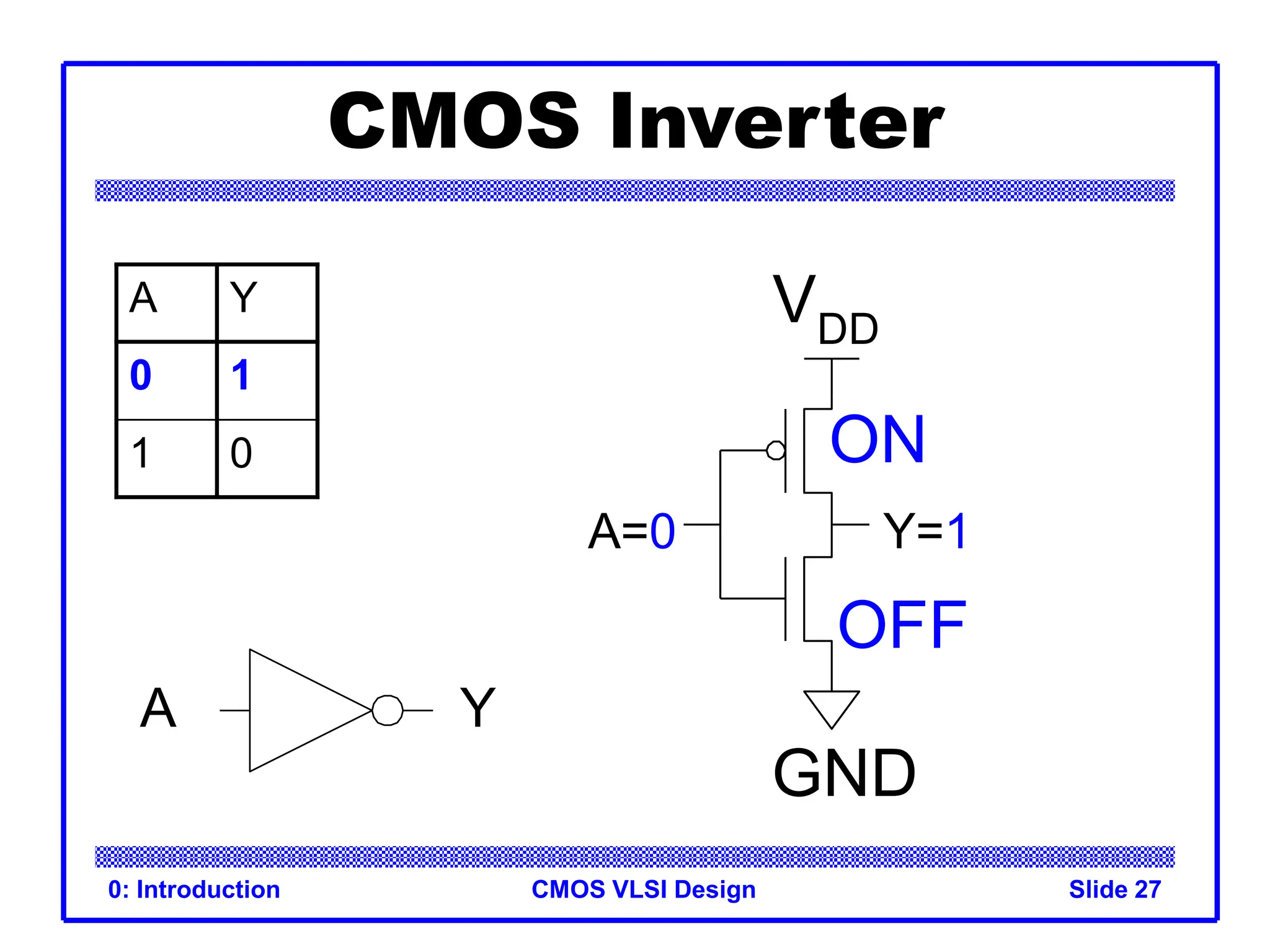

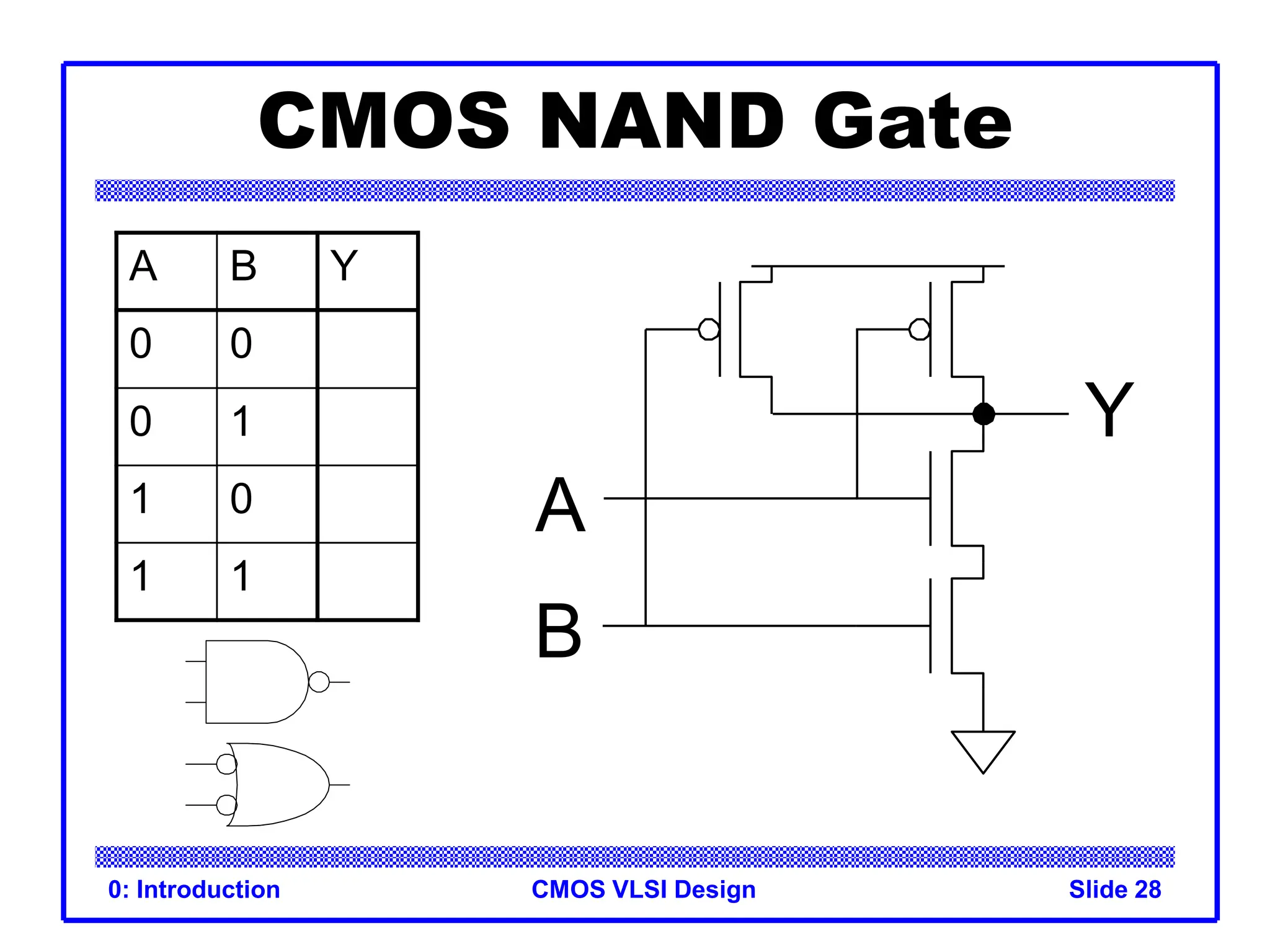

The document describes the basic CMOS fabrication process used to manufacture integrated circuits on silicon wafers. Key steps include depositing alternating thin layers of various materials using techniques like oxidation, lithography, etching, doping, and thermal diffusion. Transistors and wiring are defined using a series of photomasks. The fabrication process is explained through diagrams showing cross-sections of a basic CMOS inverter as it is built up layer by layer on the wafer.