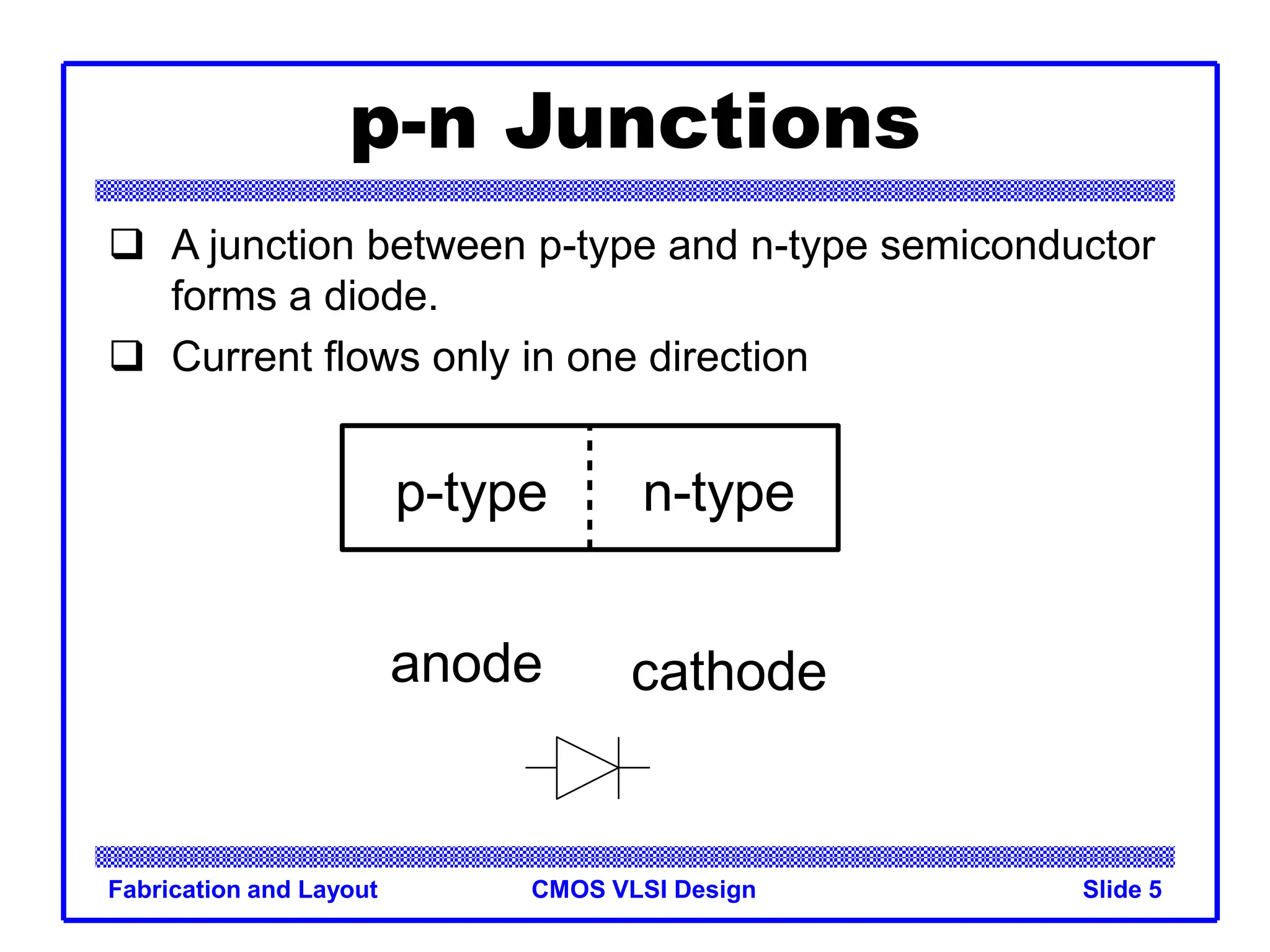

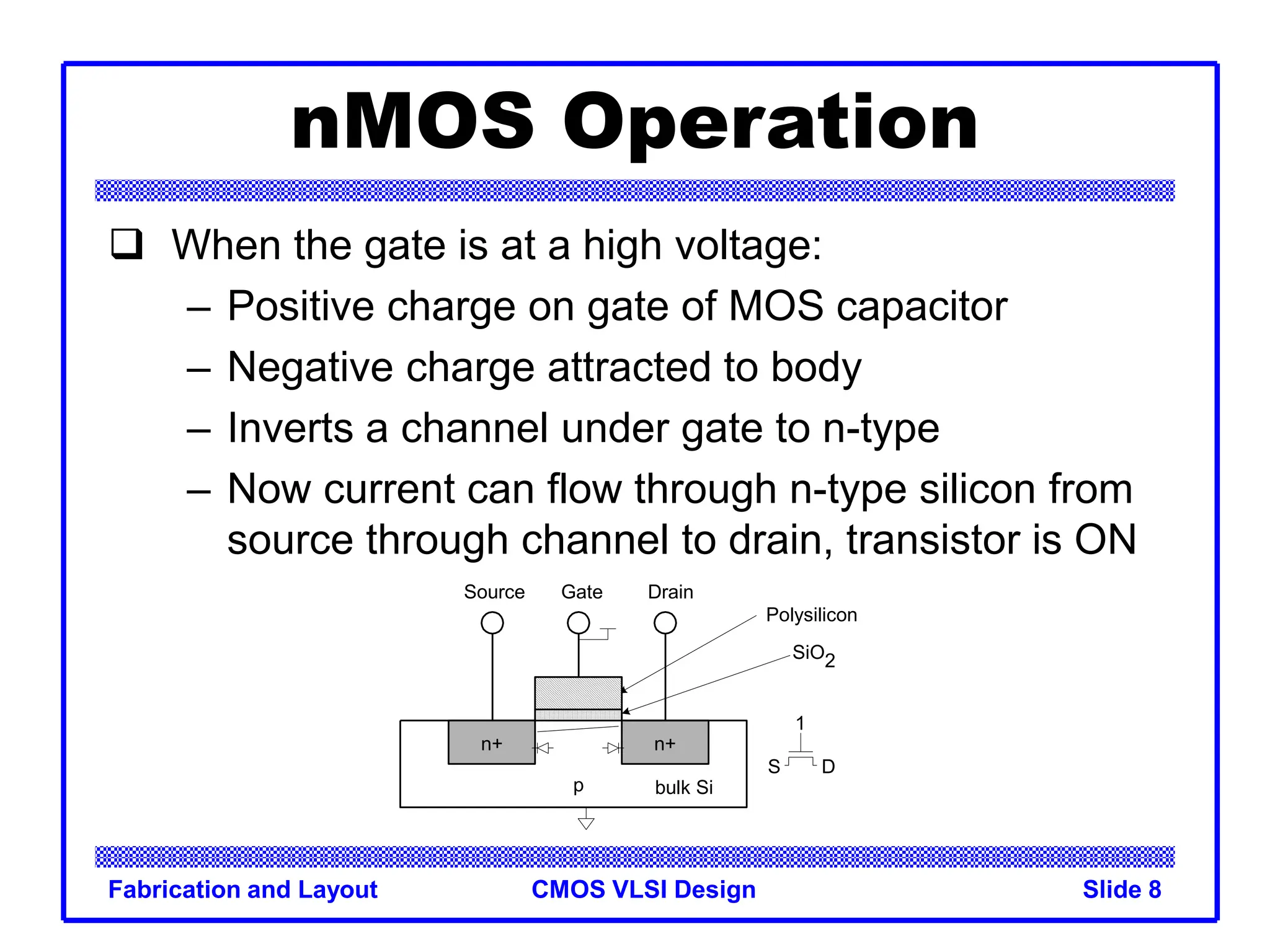

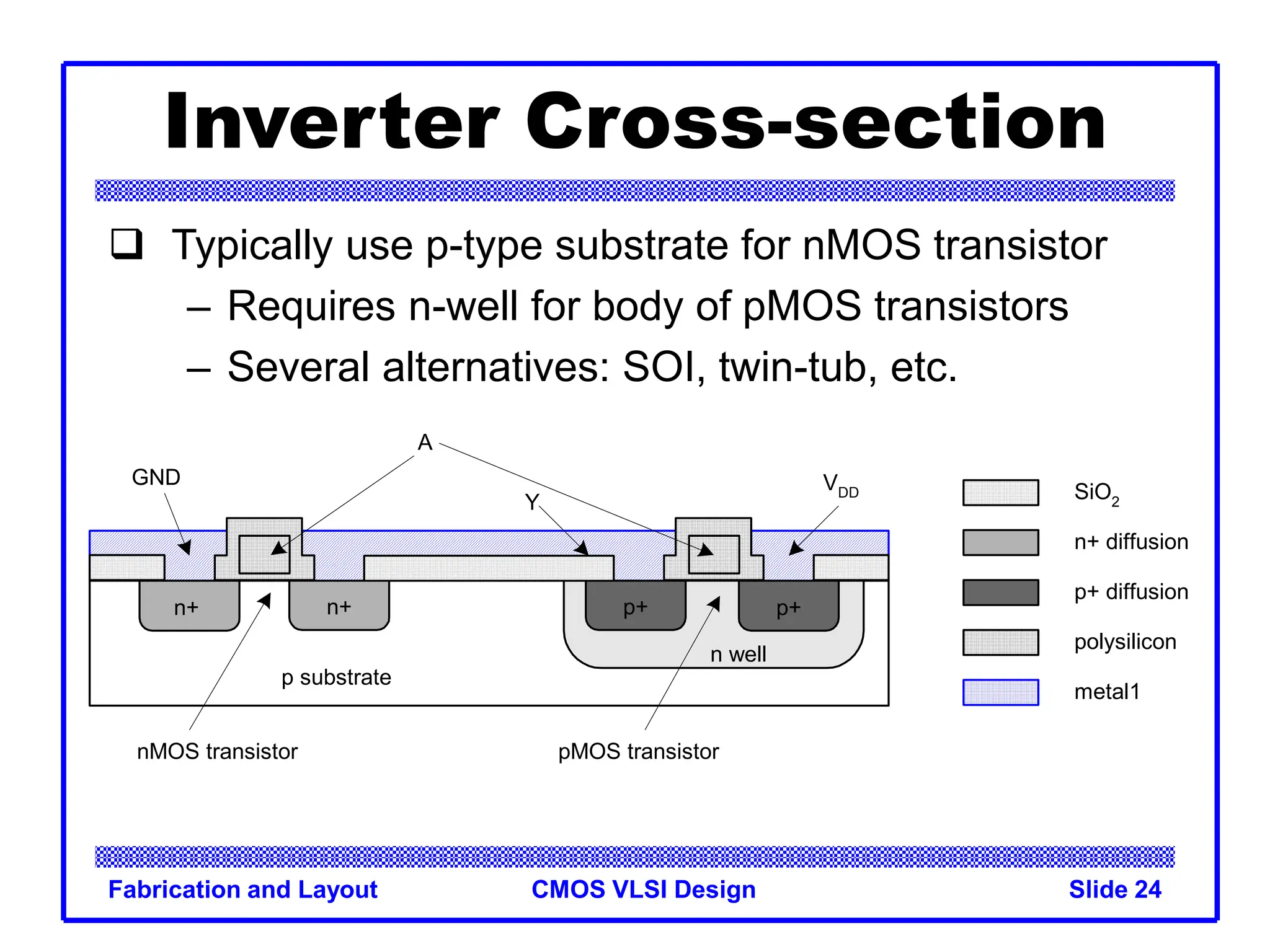

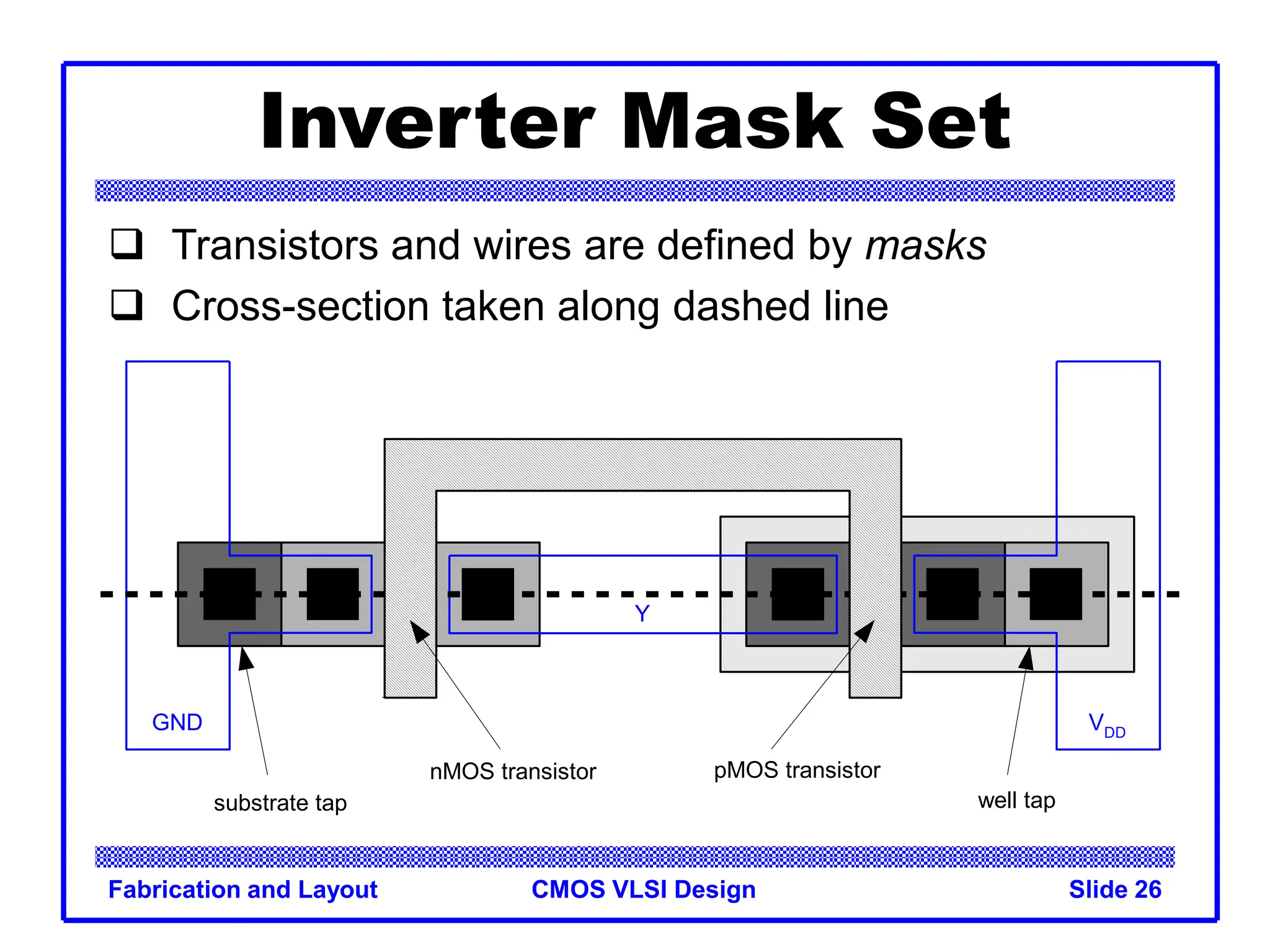

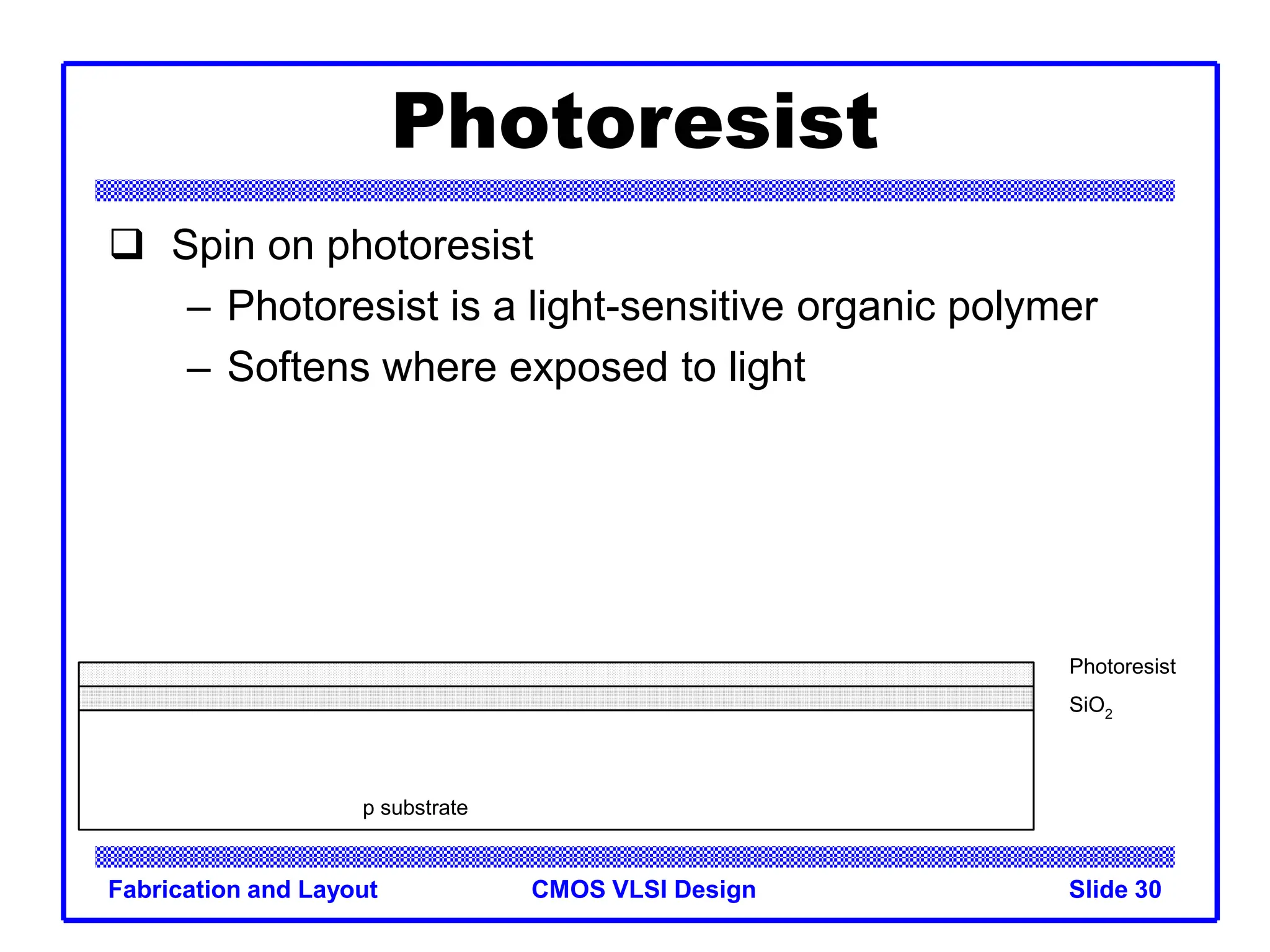

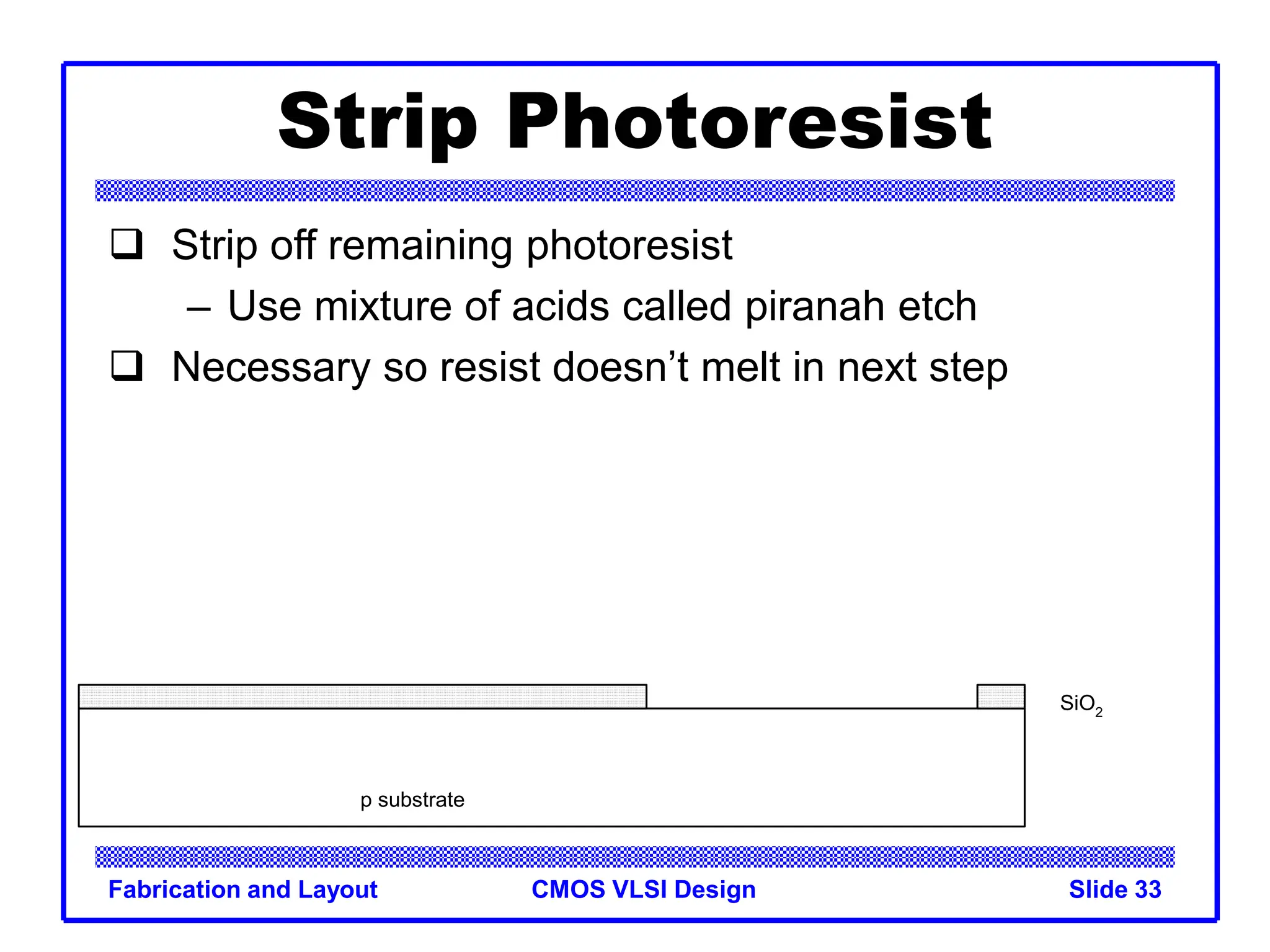

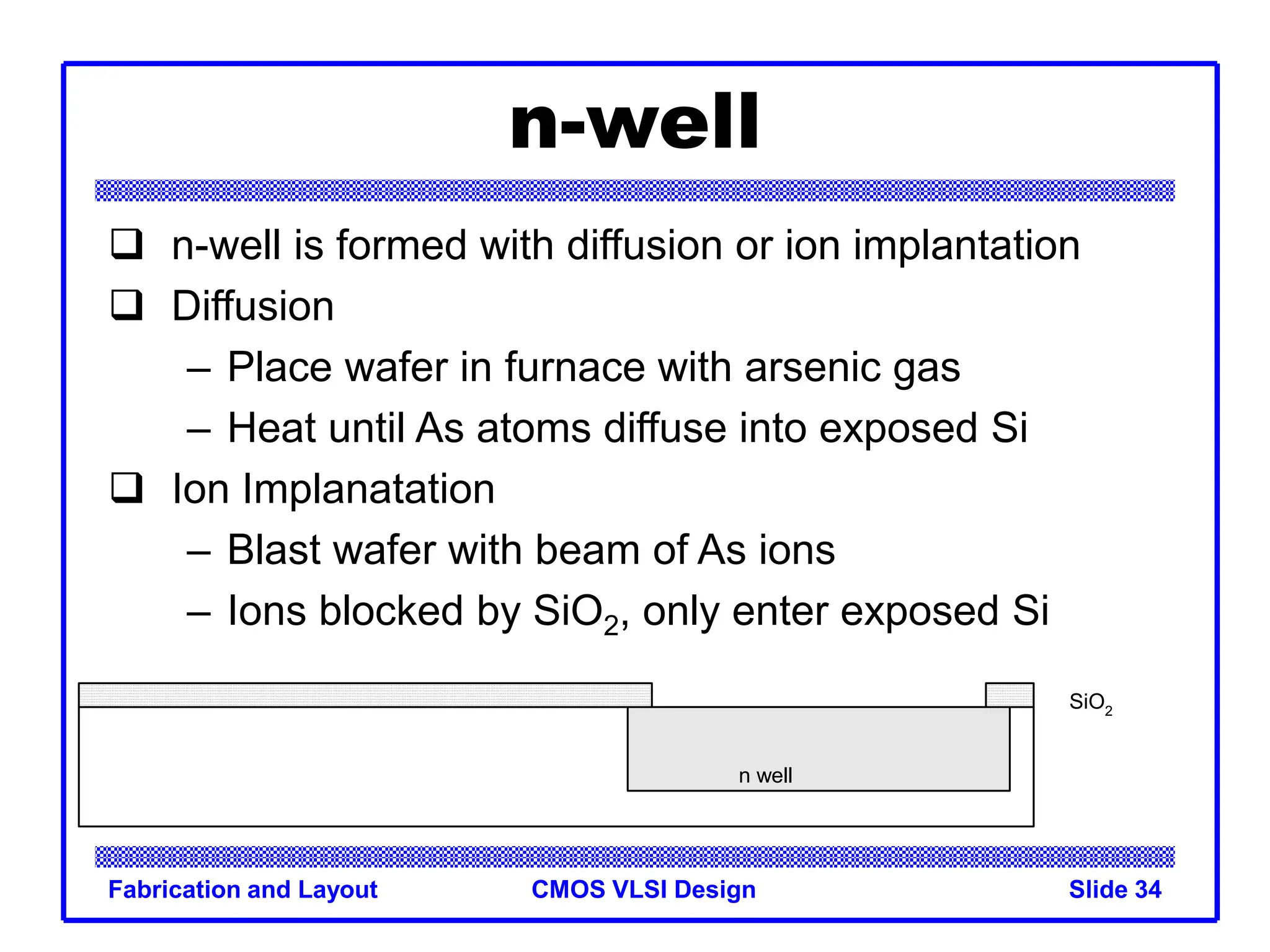

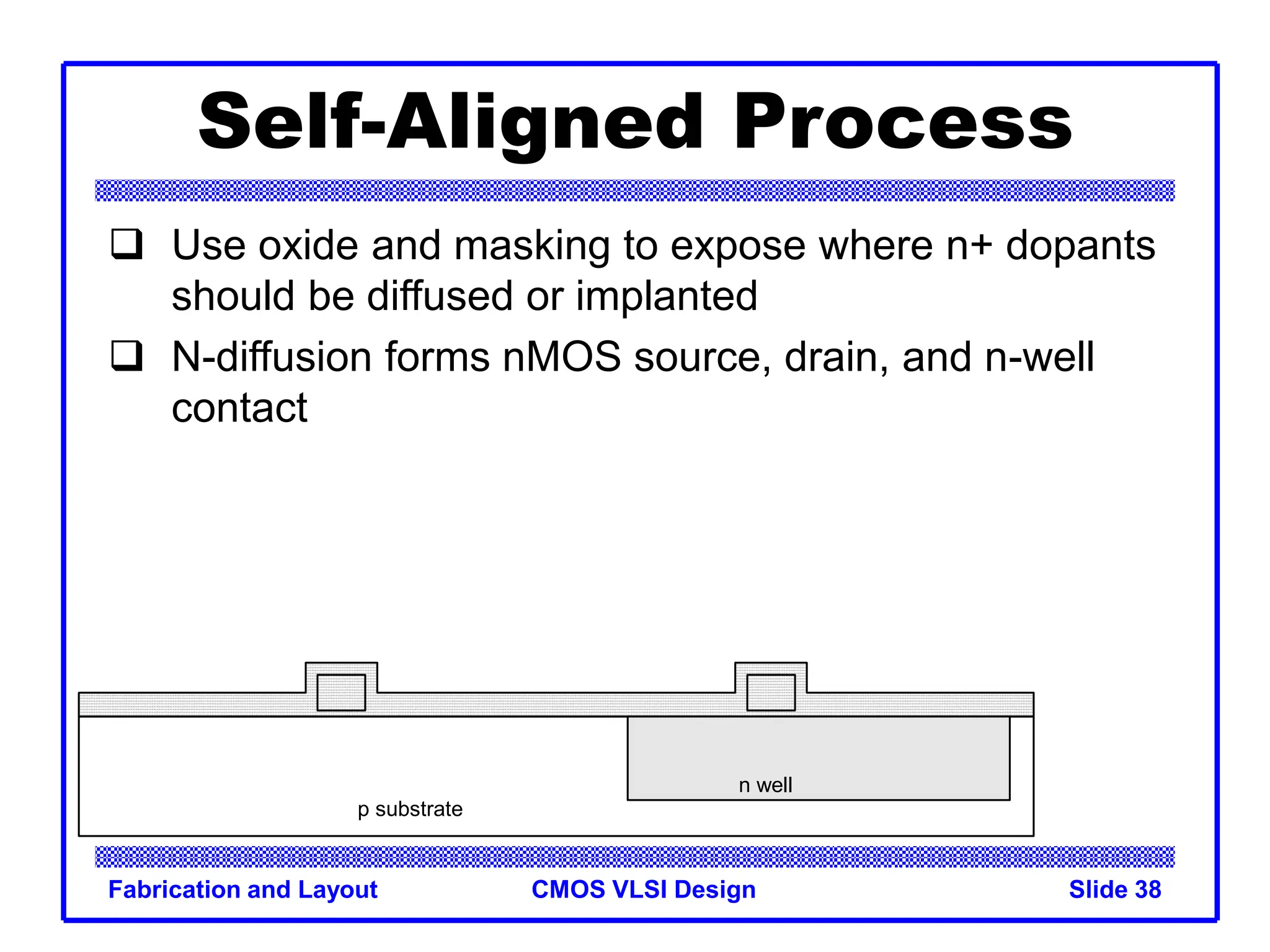

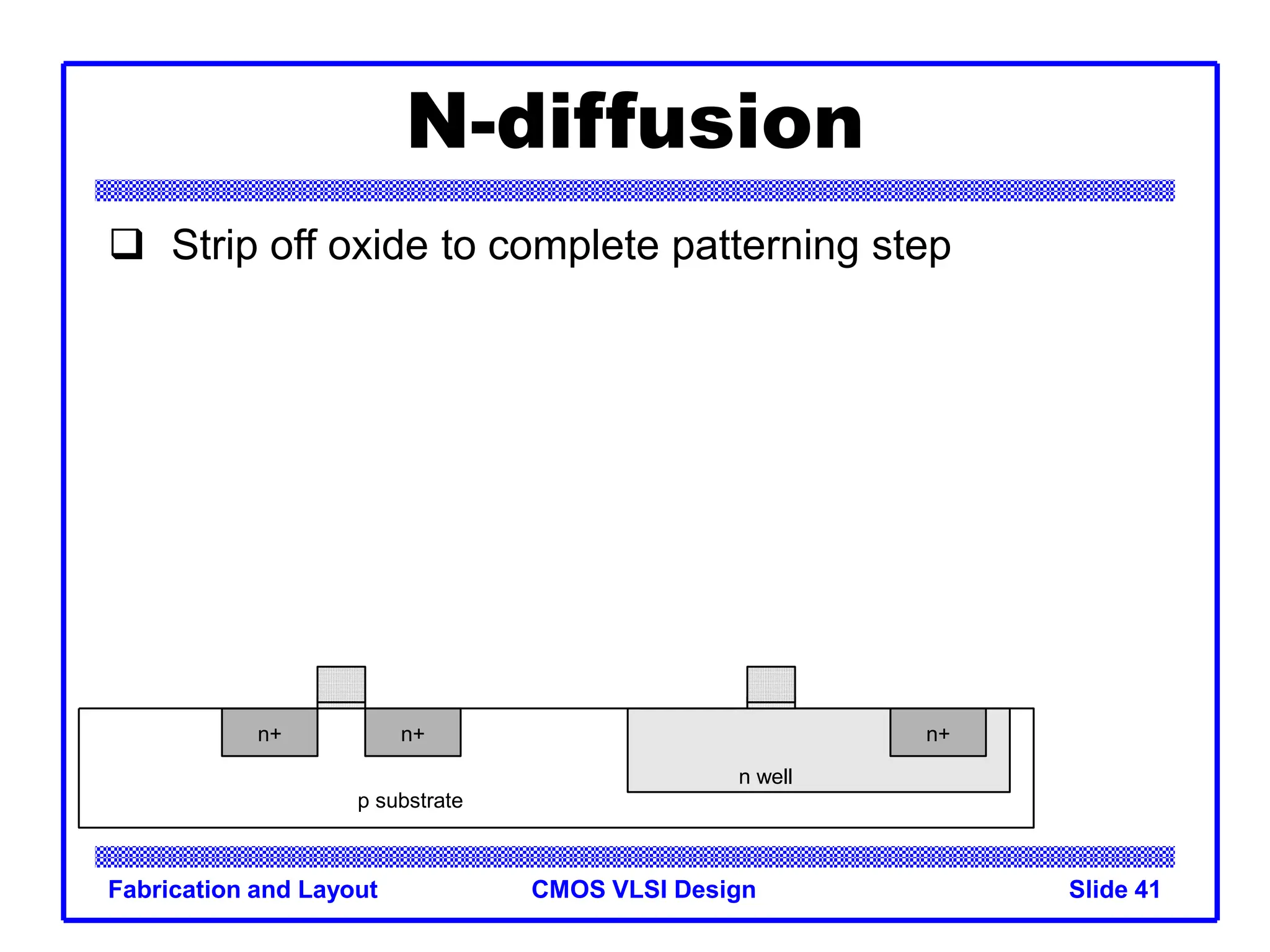

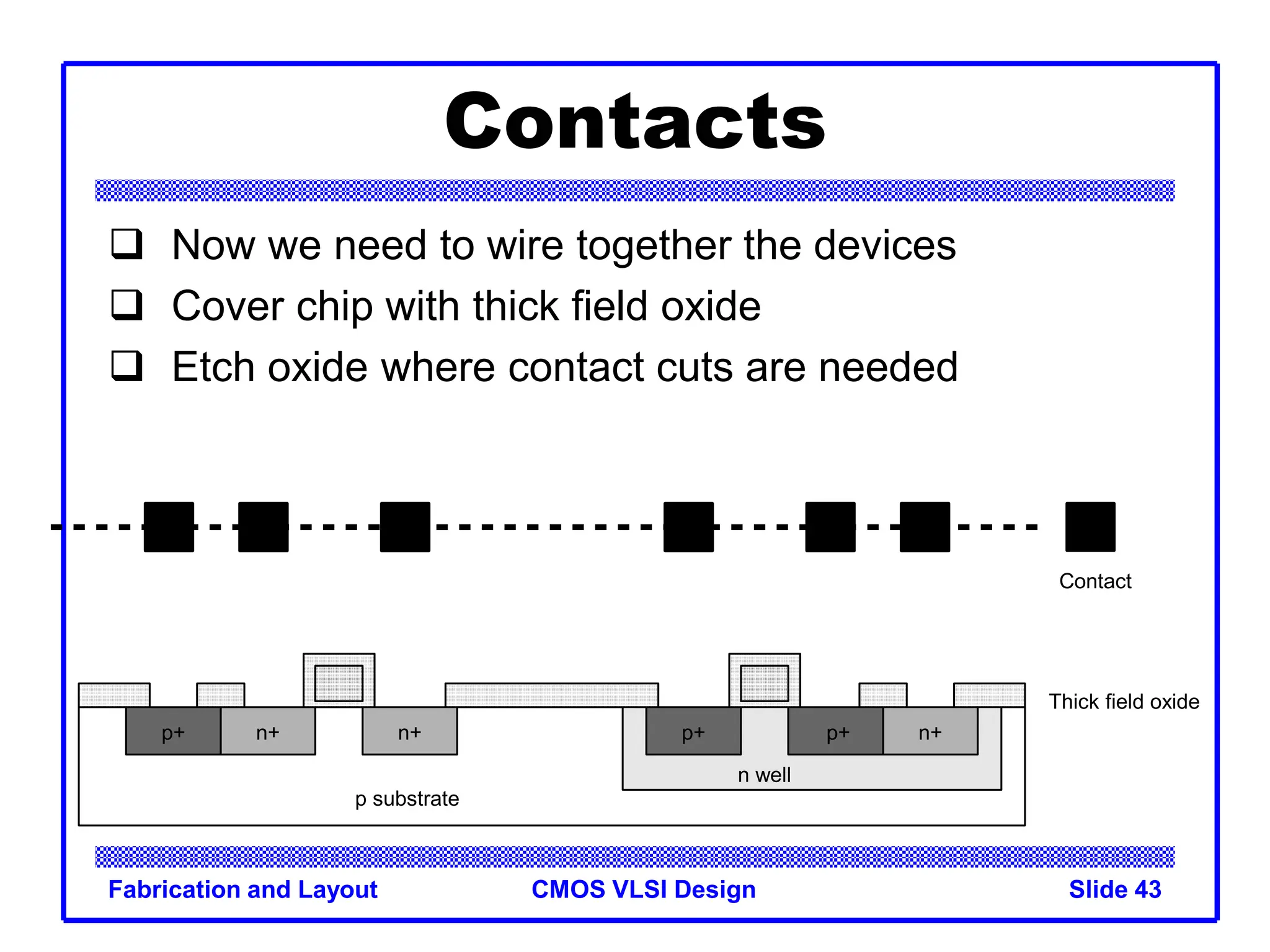

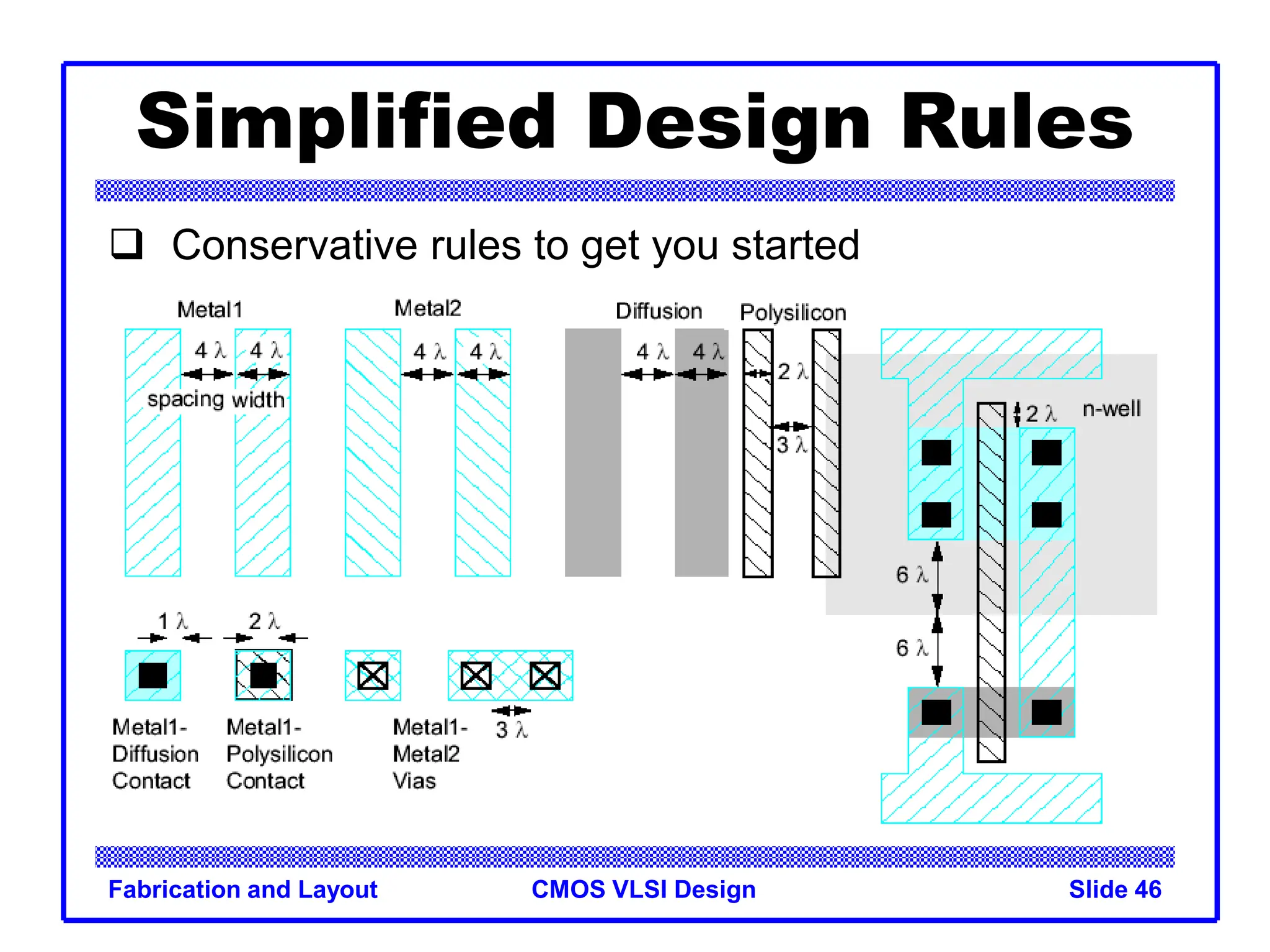

The document provides an introduction to CMOS VLSI design, fabrication, and elementary logic design. It discusses how CMOS chips are built using transistors fabricated on a silicon substrate using a lithography process to define layers like doped regions, polysilicon gates, contacts and metal interconnects. It then explains how basic logic gates like inverters and NAND gates are constructed using nMOS and pMOS transistors and how their operation depends on input voltages. Finally, it outlines the main steps in the CMOS fabrication process used to build up the transistor and interconnect structures in multiple layers.