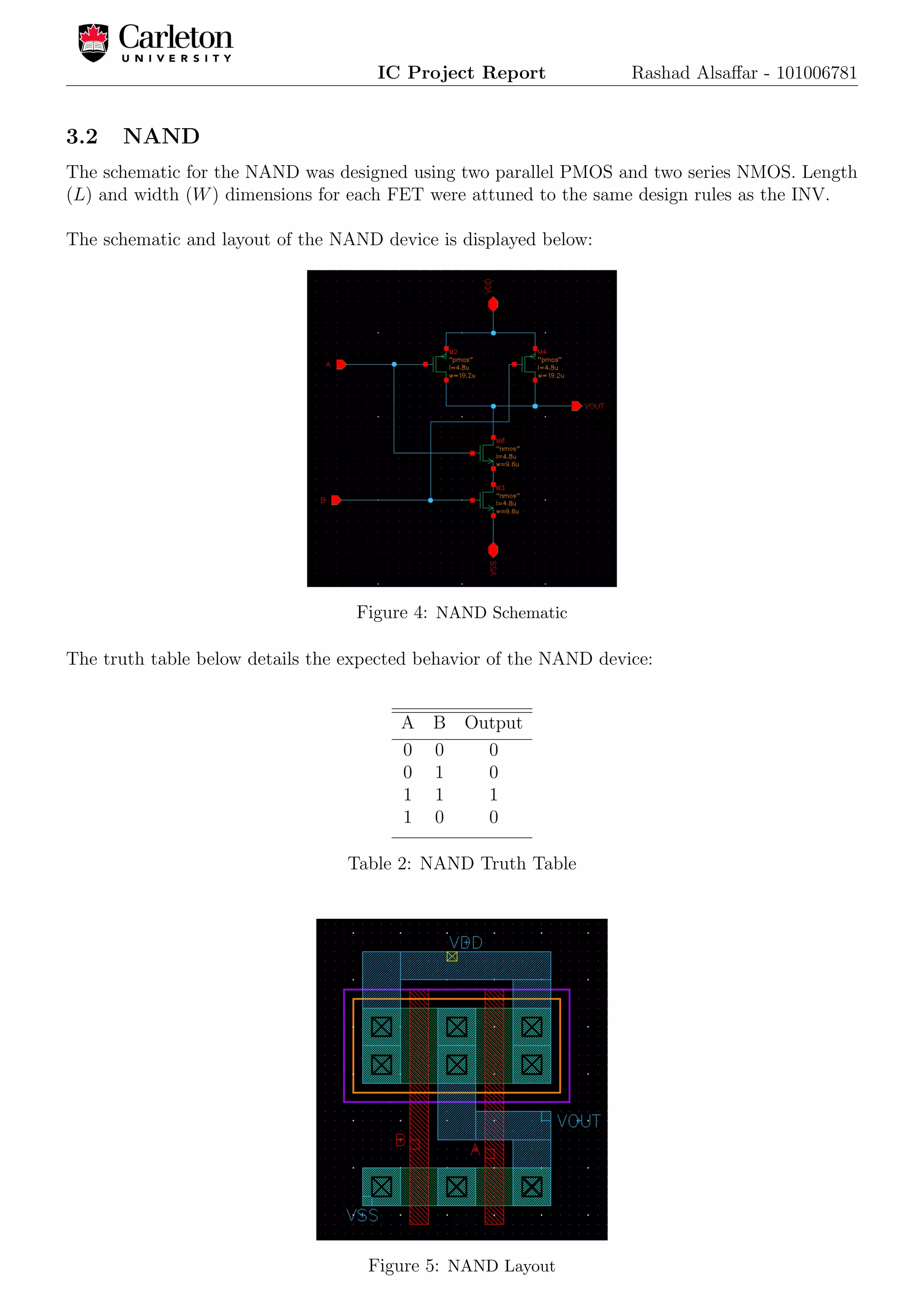

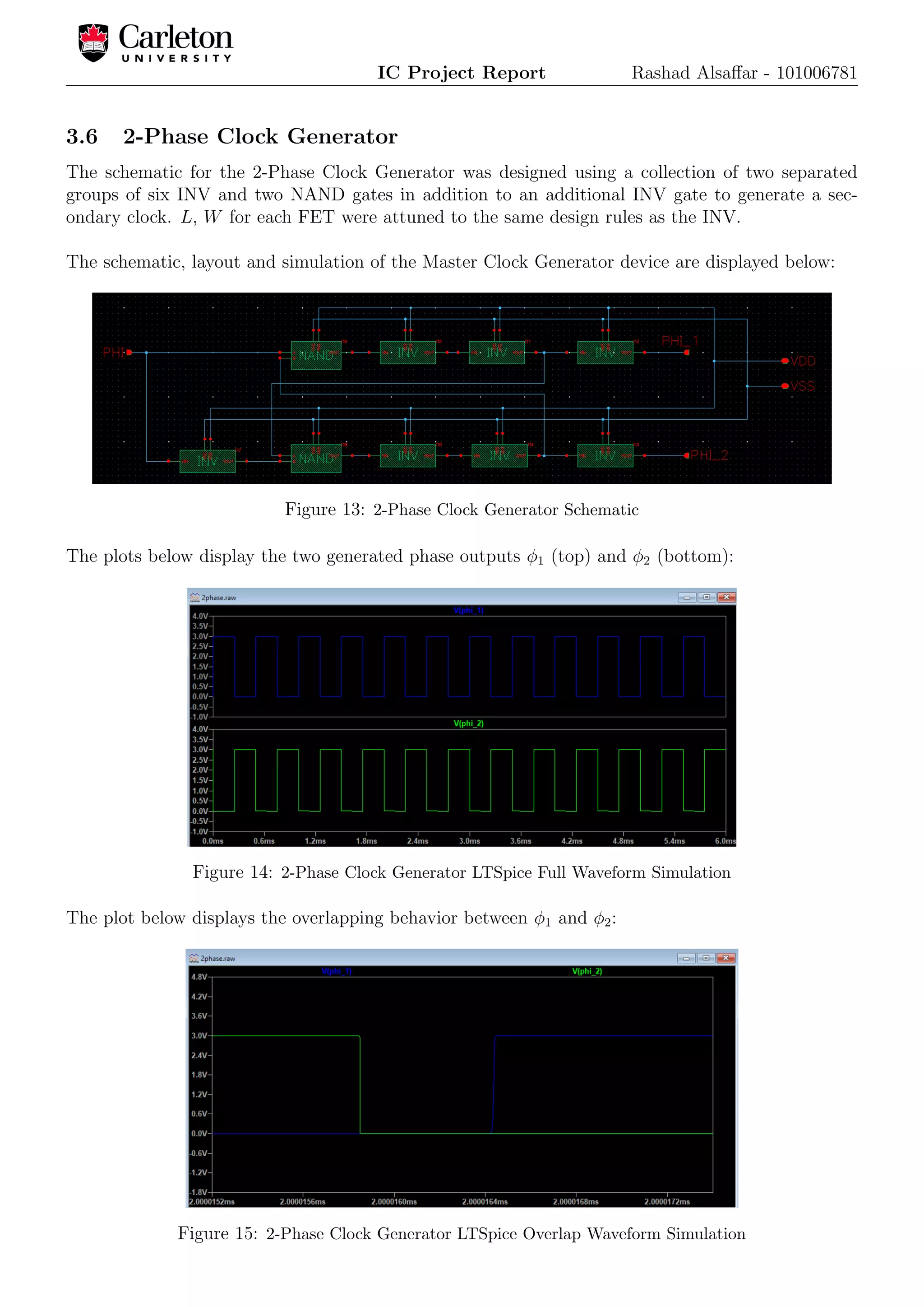

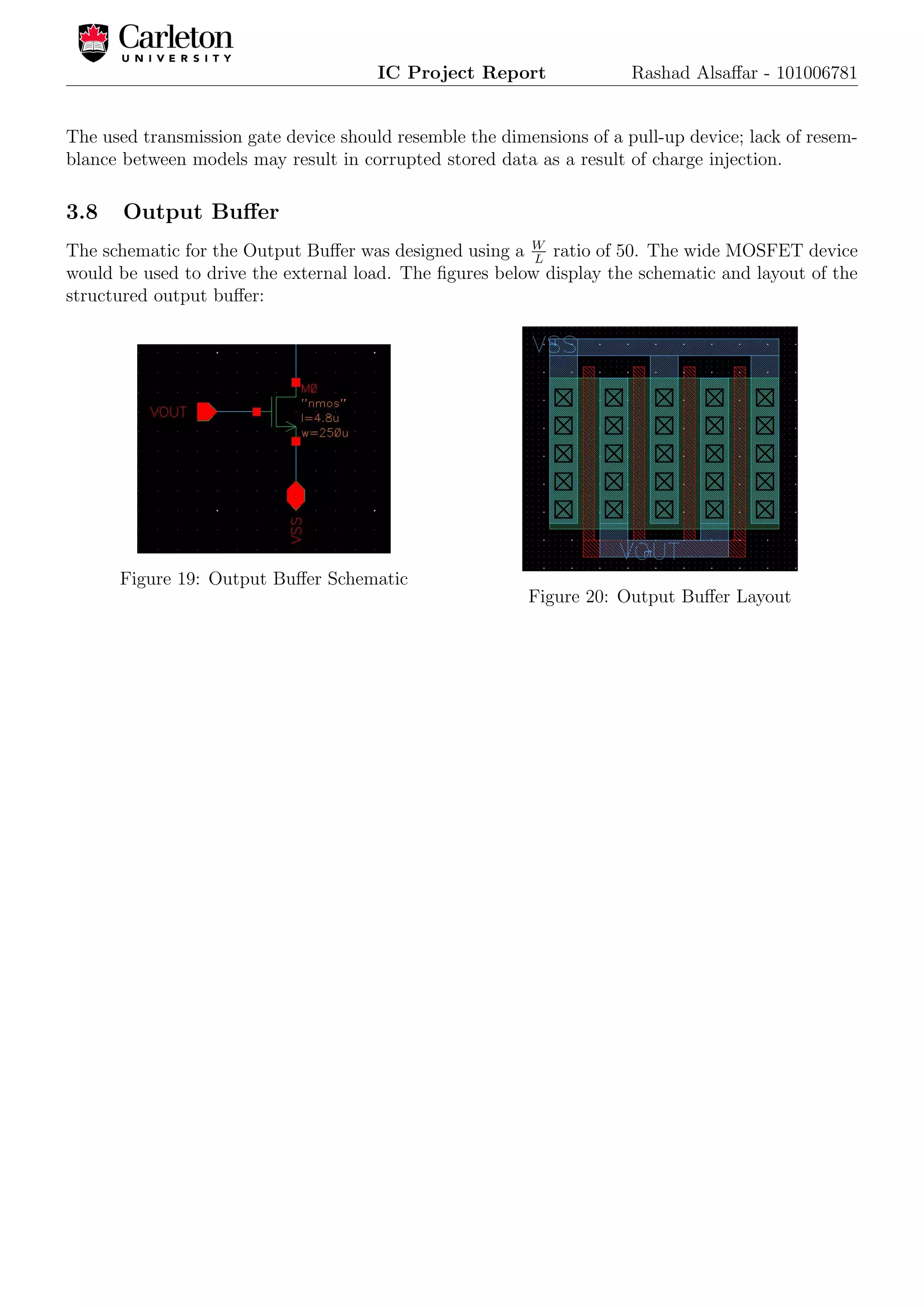

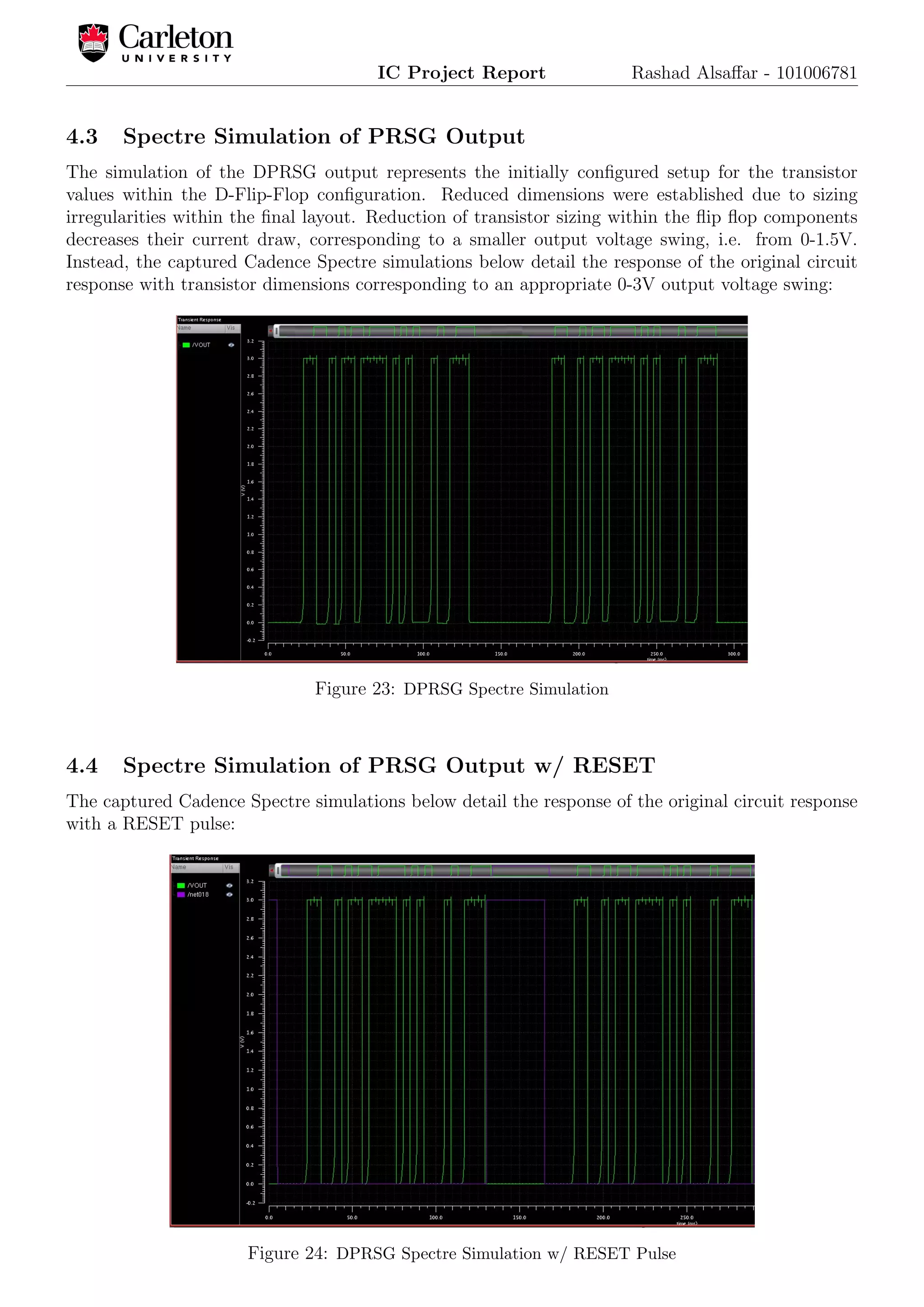

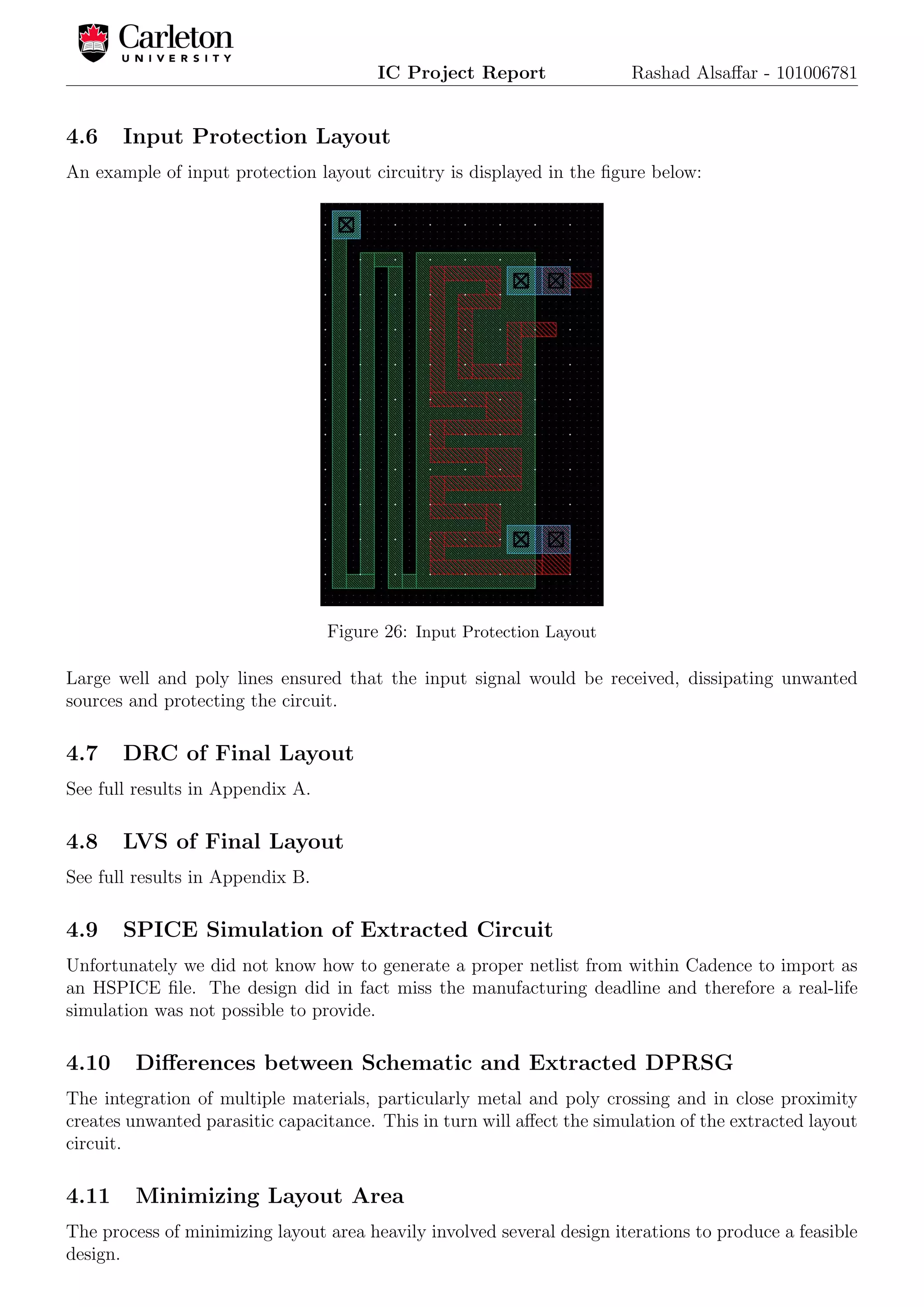

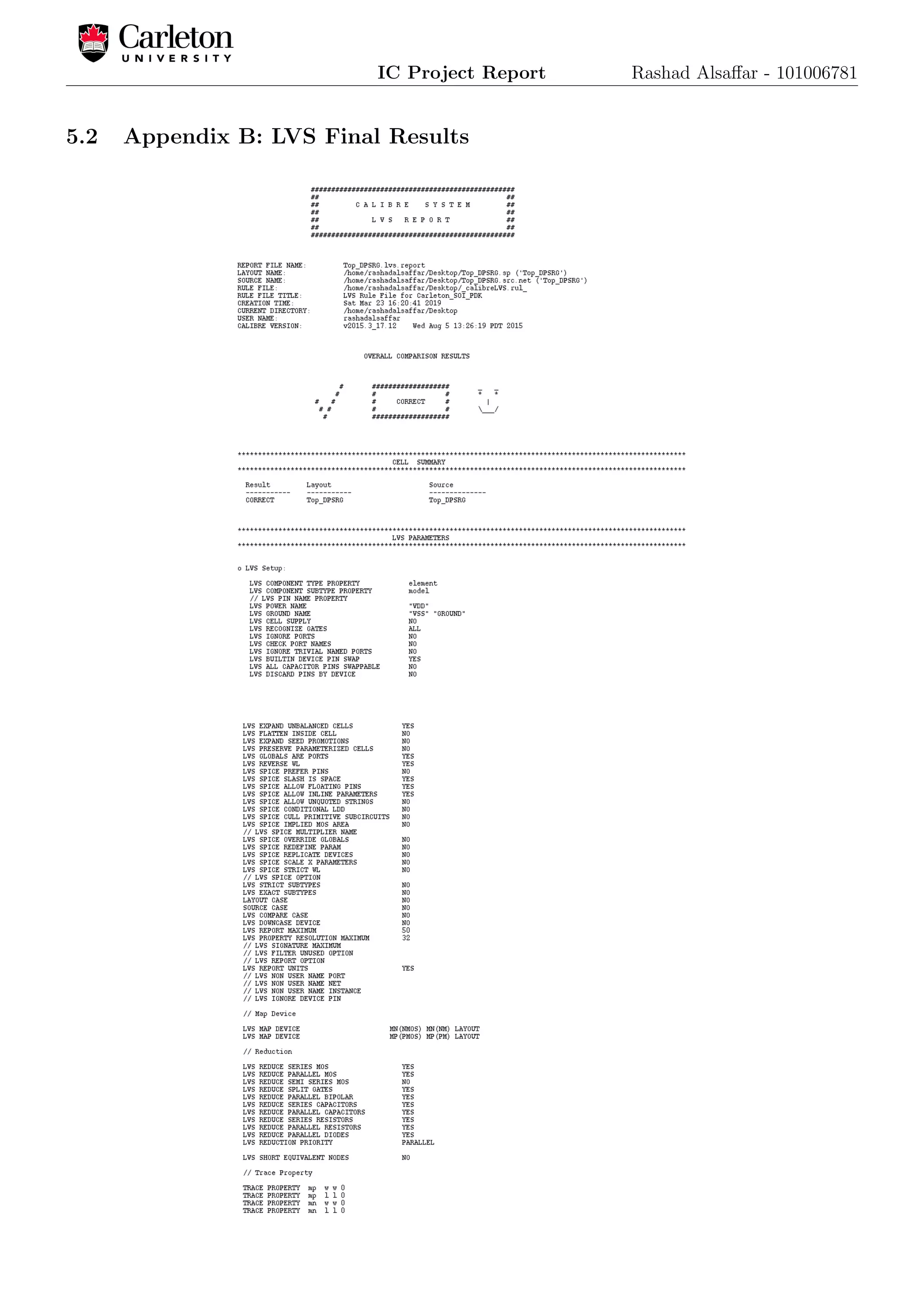

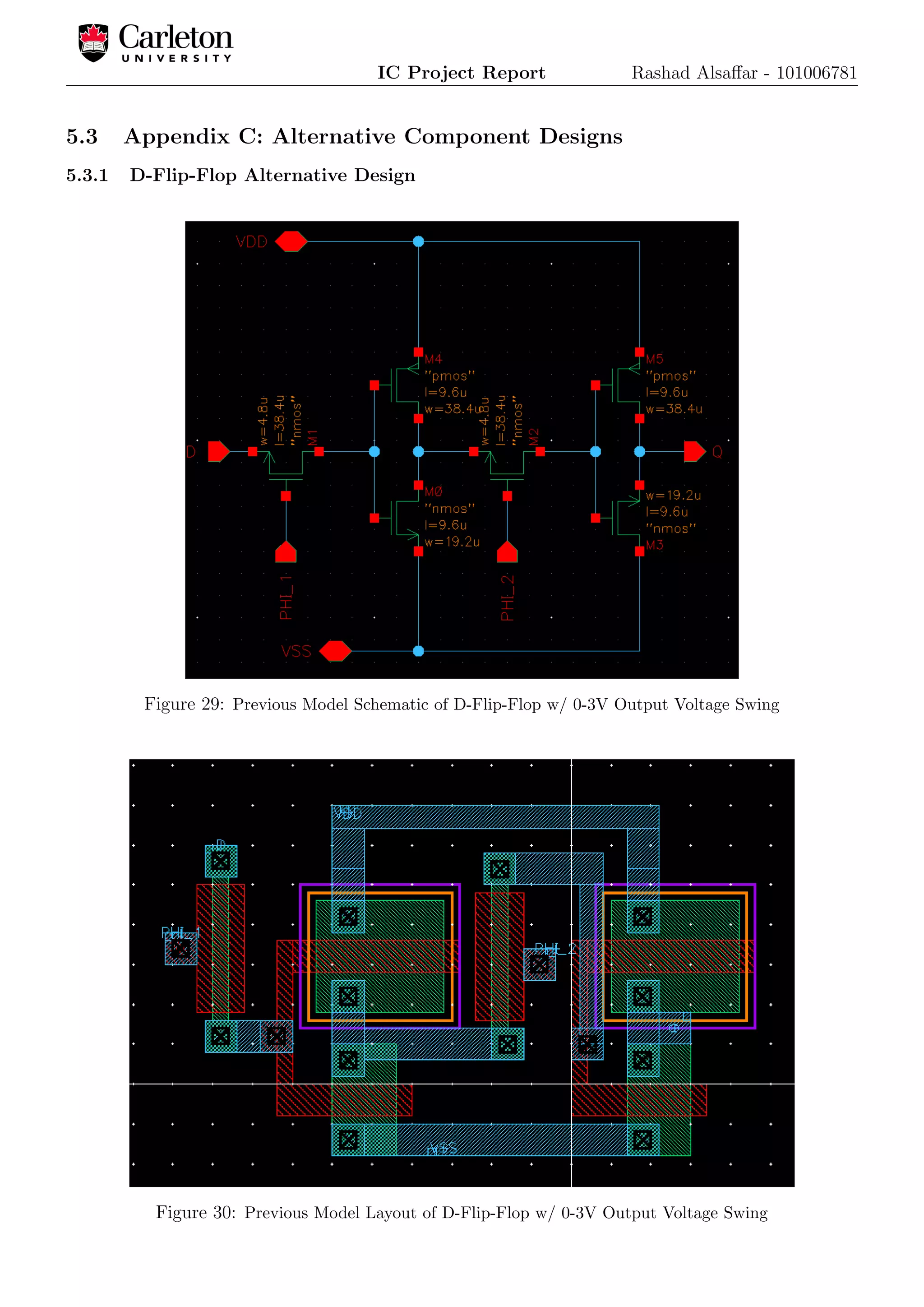

The project focused on designing and fabricating a 5-bit dynamic pseudorandom sequence generator integrated circuit (dprsg) at Carleton University, utilizing various digital logic components and custom layouts. It details the design process, specifications, individual block designs, and a final layout while ensuring simulation tests like DRC and LVS were performed to verify functionality. Challenges included dimension reductions for the d-flip-flop and managing oscillator clock signals to minimize overlap in the clock phases.