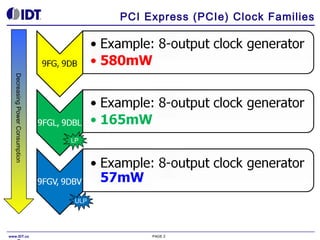

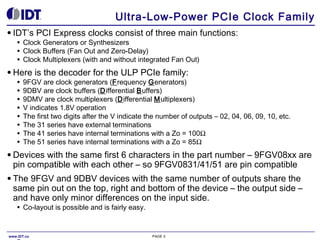

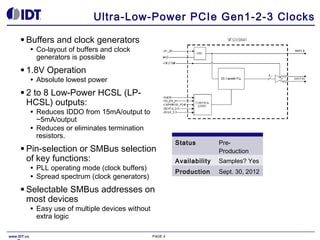

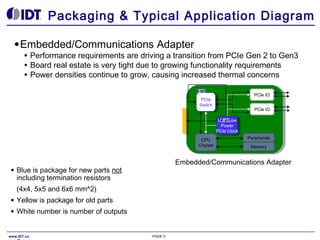

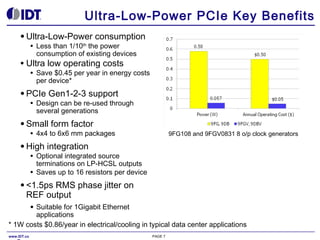

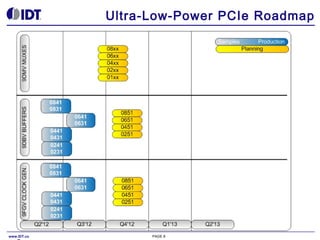

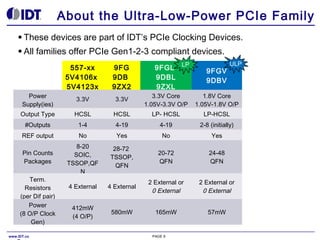

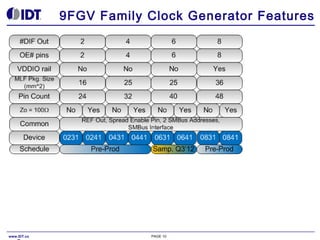

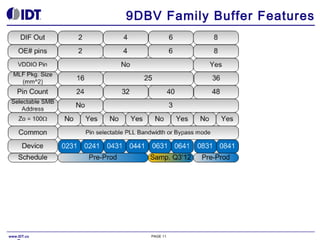

The document outlines IDT's ultra-low-power PCI Express (PCIe) clocking solutions for generations 1-3, showcasing products such as clock generators, buffers, and multiplexers designed for reduced power consumption and high integration. It highlights key features including low operating voltage, minimal power usage, and compact packaging suitable for applications in cloud computing, solid-state drives, and instrumentation. Additionally, it provides information on compatibility, availability, and the potential cost savings associated with using these new devices.