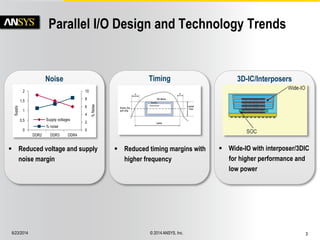

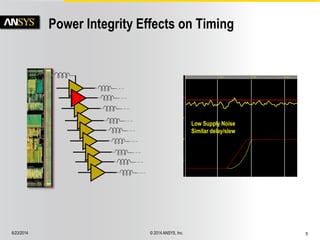

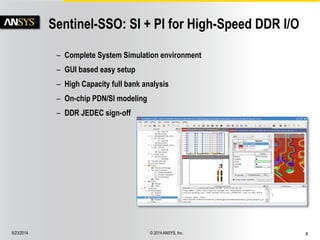

The document discusses the Sentinel-SSO tool for DDR-I/O power and signal integrity analysis, highlighting its modeling requirements and benefits such as complete system simulation and integrated environment for prototyping. It addresses trends in parallel I/O design and the impact of power noise on signal integrity, emphasizing accurate on-chip and I/O modeling capabilities. The document also outlines advancements in simulation accuracy and automatic reporting features.