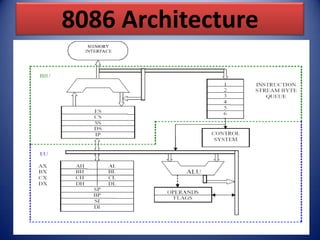

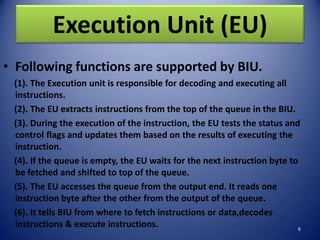

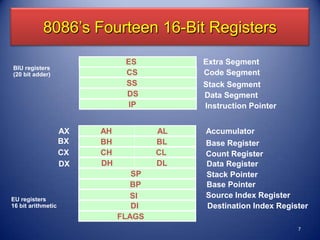

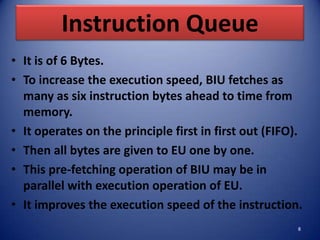

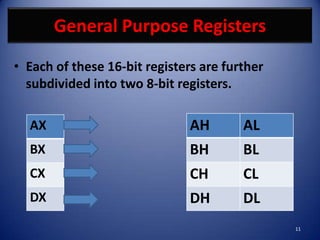

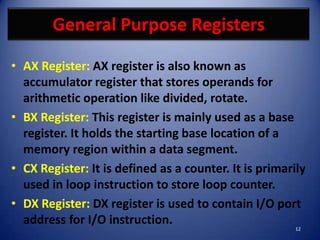

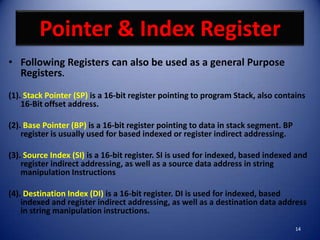

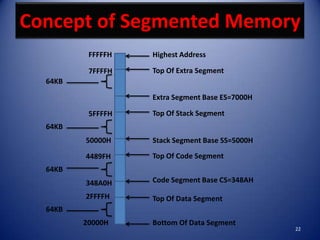

The document describes the 8086 16-bit microprocessor, including that it has a 20-bit address bus, 16-bit data bus, 29,000 transistors, and supports up to 1MB of memory. It discusses the 8086's architecture, which has a bus interface unit and execution unit, as well as its 14 16-bit registers including general purpose, pointer, index, and segment registers. The document also covers the 8086's instruction queue and concept of segmented memory addressing.