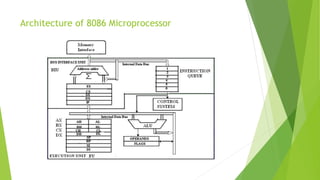

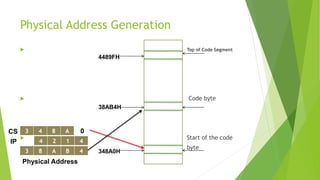

The document summarizes key aspects of the 8086 microprocessor architecture. It describes how the CPU is divided into two units: the Bus Interface Unit (BIU) which handles external bus operations like fetching instructions, and the Execution Unit (EU) which decodes and executes instructions. It provides details on the register organization including general purpose registers, segment registers, and the flag register. It also explains memory segmentation and how physical addresses are calculated by combining segment register values with offset pointers.