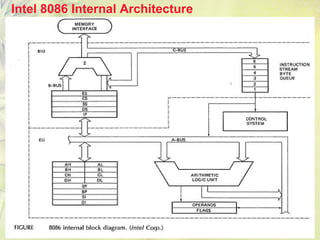

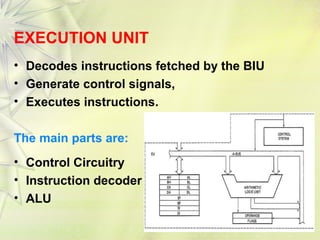

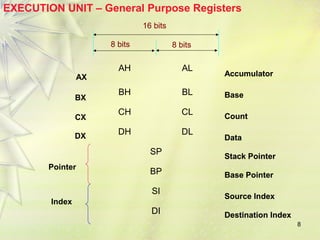

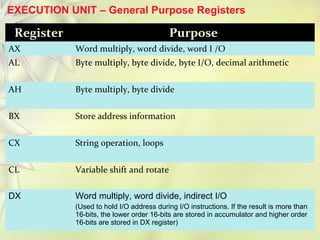

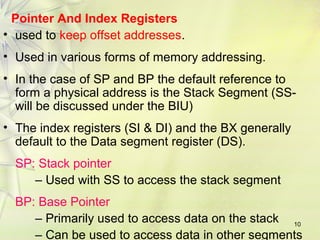

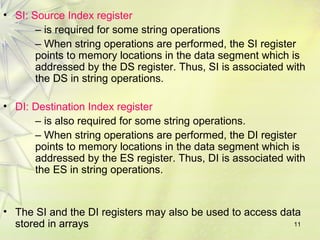

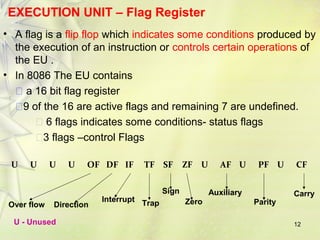

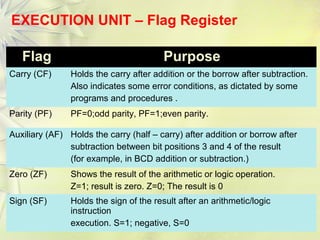

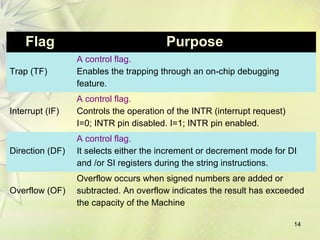

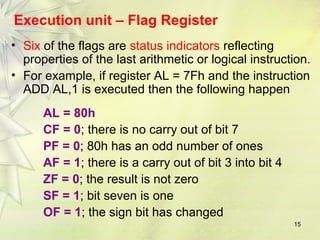

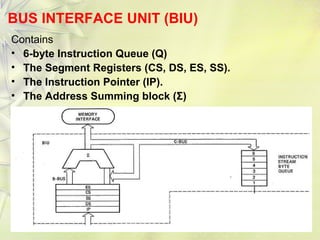

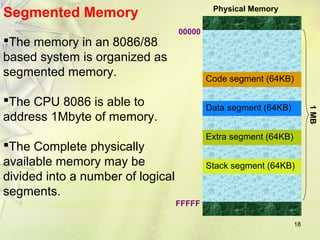

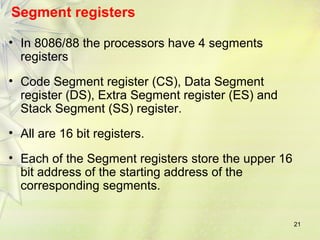

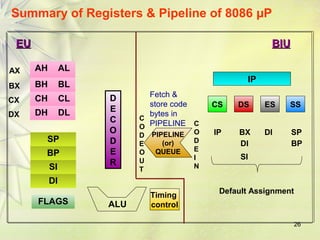

The Intel 8086 is a 16-bit microprocessor that can access up to 1 MB of memory. It has two main components: the Bus Interface Unit (BIU) handles bus operations like instruction fetching and memory access, and the Execution Unit (EU) decodes and executes instructions. The BIU contains registers for the code, data, extra, and stack segments as well as an instruction queue. The EU has registers for accumulation, base, count, data, pointers, and flags, and contains an ALU and instruction decoder. It executes instructions from the queued bytes using a pipeline architecture.