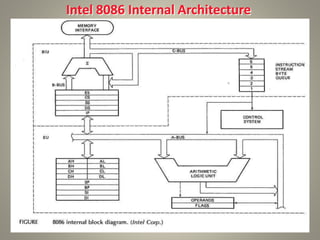

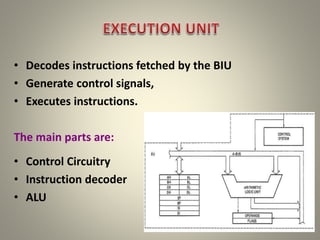

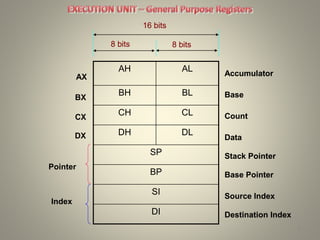

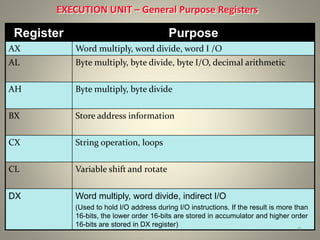

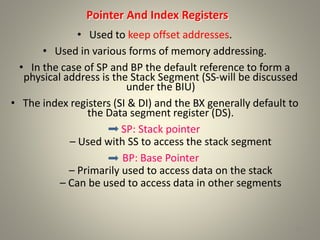

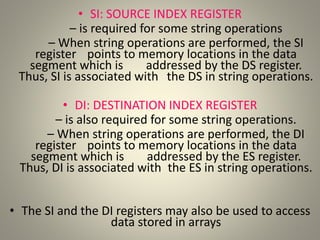

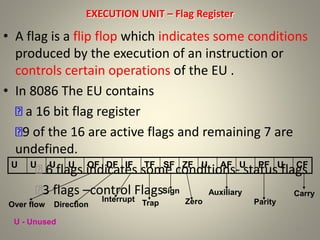

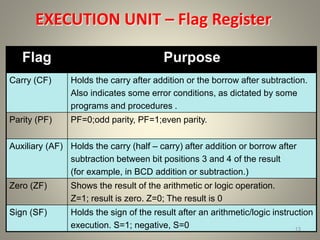

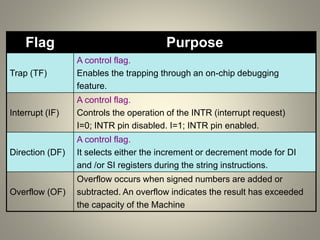

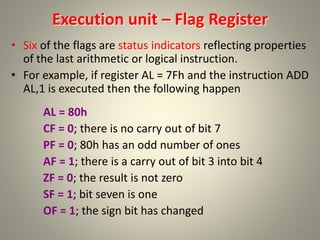

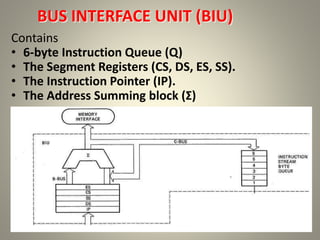

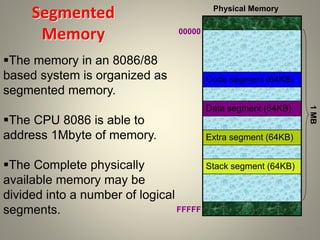

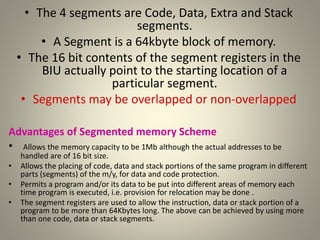

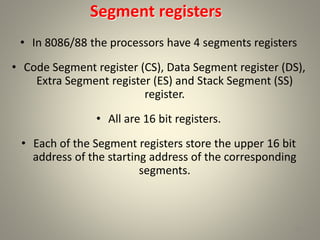

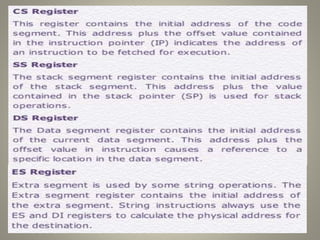

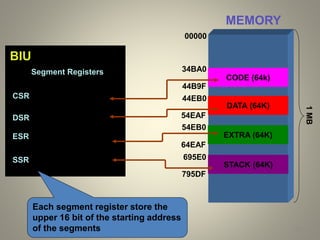

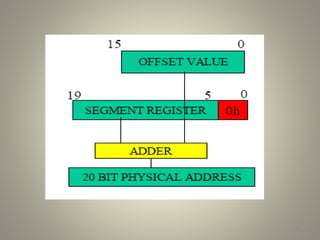

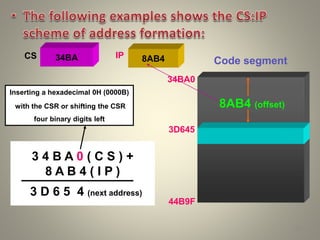

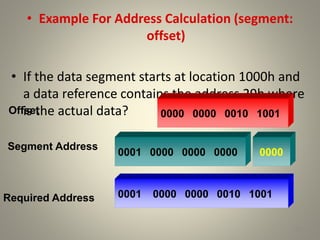

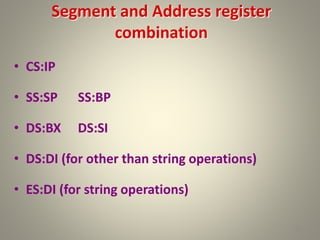

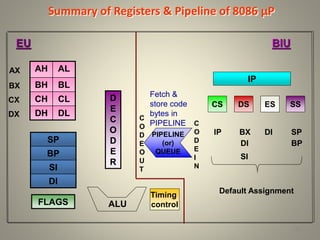

The Intel 8086 microprocessor is a 16-bit processor with a 20-bit address bus, capable of addressing up to 1 MB of memory and supporting 64k I/O ports. It operates using a Bus Interface Unit (BIU) and an Execution Unit (EU), featuring an instruction queue for pipelined instruction processing. The 8086 architecture utilizes segmented memory, allowing for efficient organization and protection of code, data, and stack segments, and includes a variety of registers and flags for managing operations.