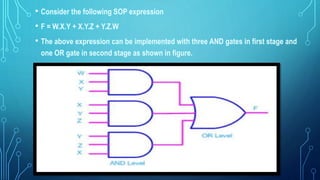

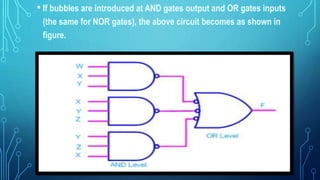

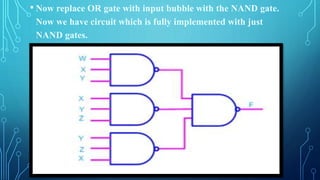

This document discusses the implementation of logic functions using NAND and NOR gates. It explains that any logic function can be realized using either NAND gates by writing it in Sum of Product form, or using NOR gates by writing it in Product of Sum form. It provides an example of a logic function F = W.X.Y + X.Y.Z + Y.Z.W that is implemented using both NAND and NOR gates. Additionally, it discusses common logic minimization techniques like algebraic minimization and Karnaugh maps that are used to simplify Boolean logic expressions into the most efficient form.