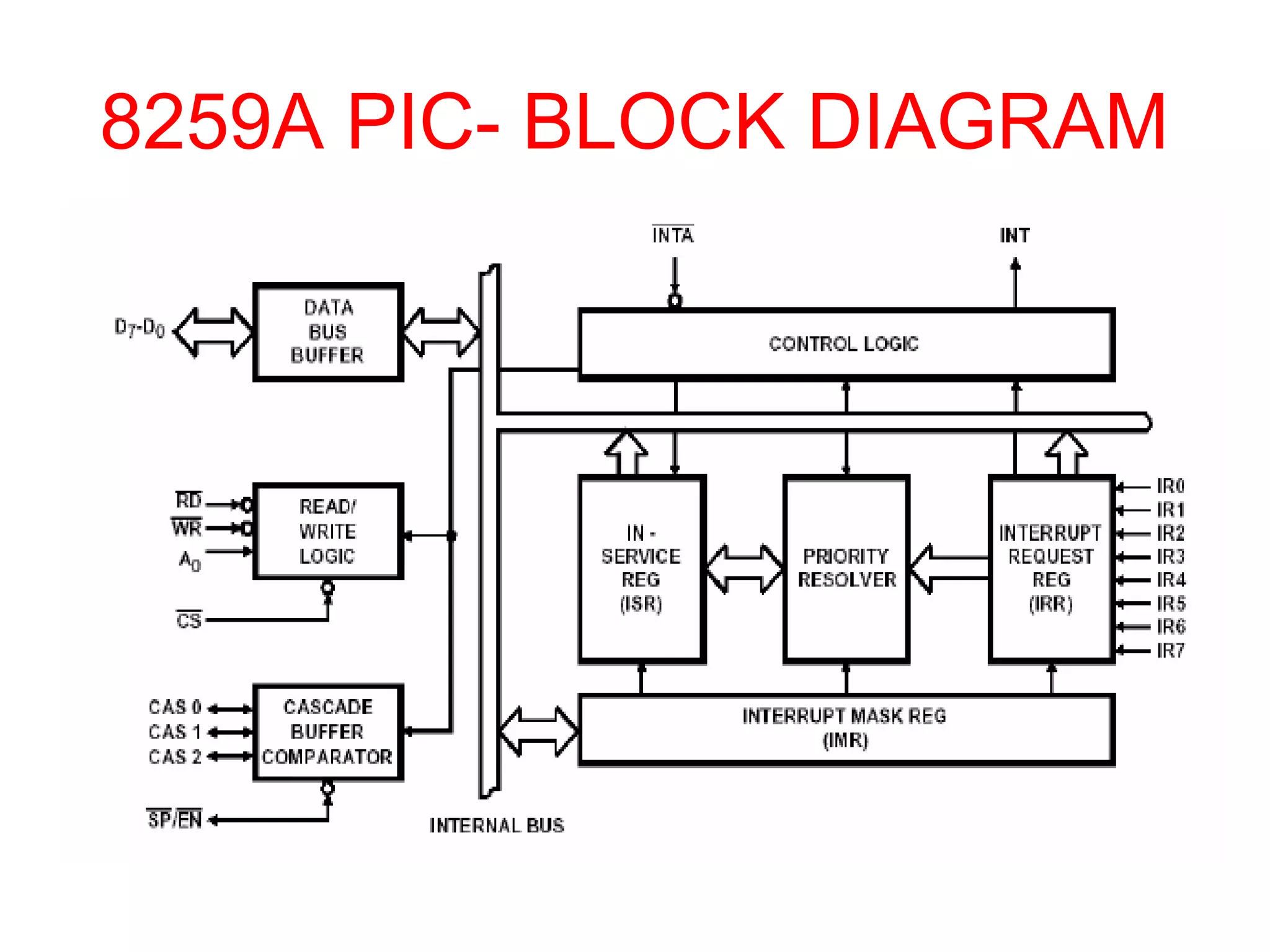

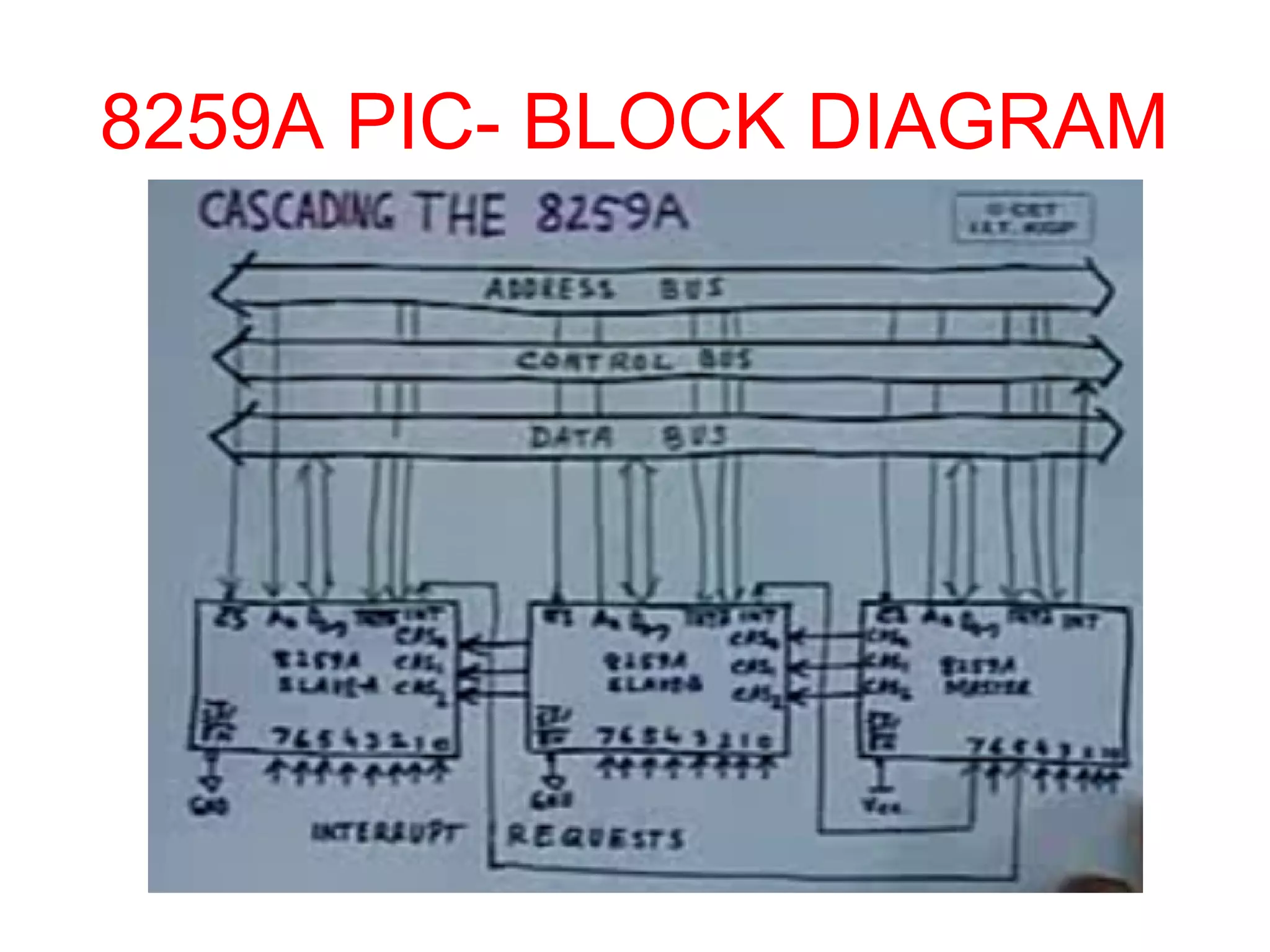

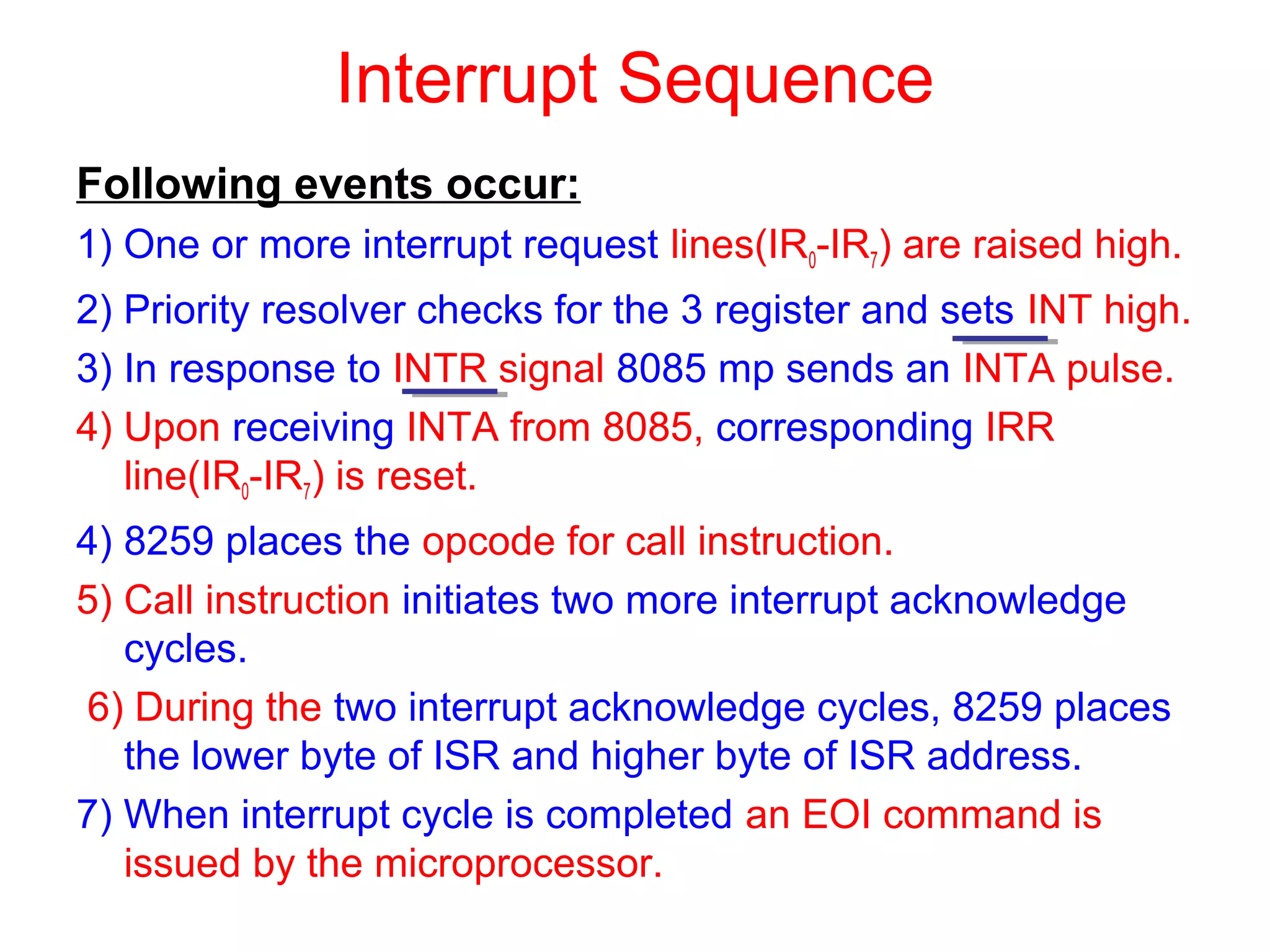

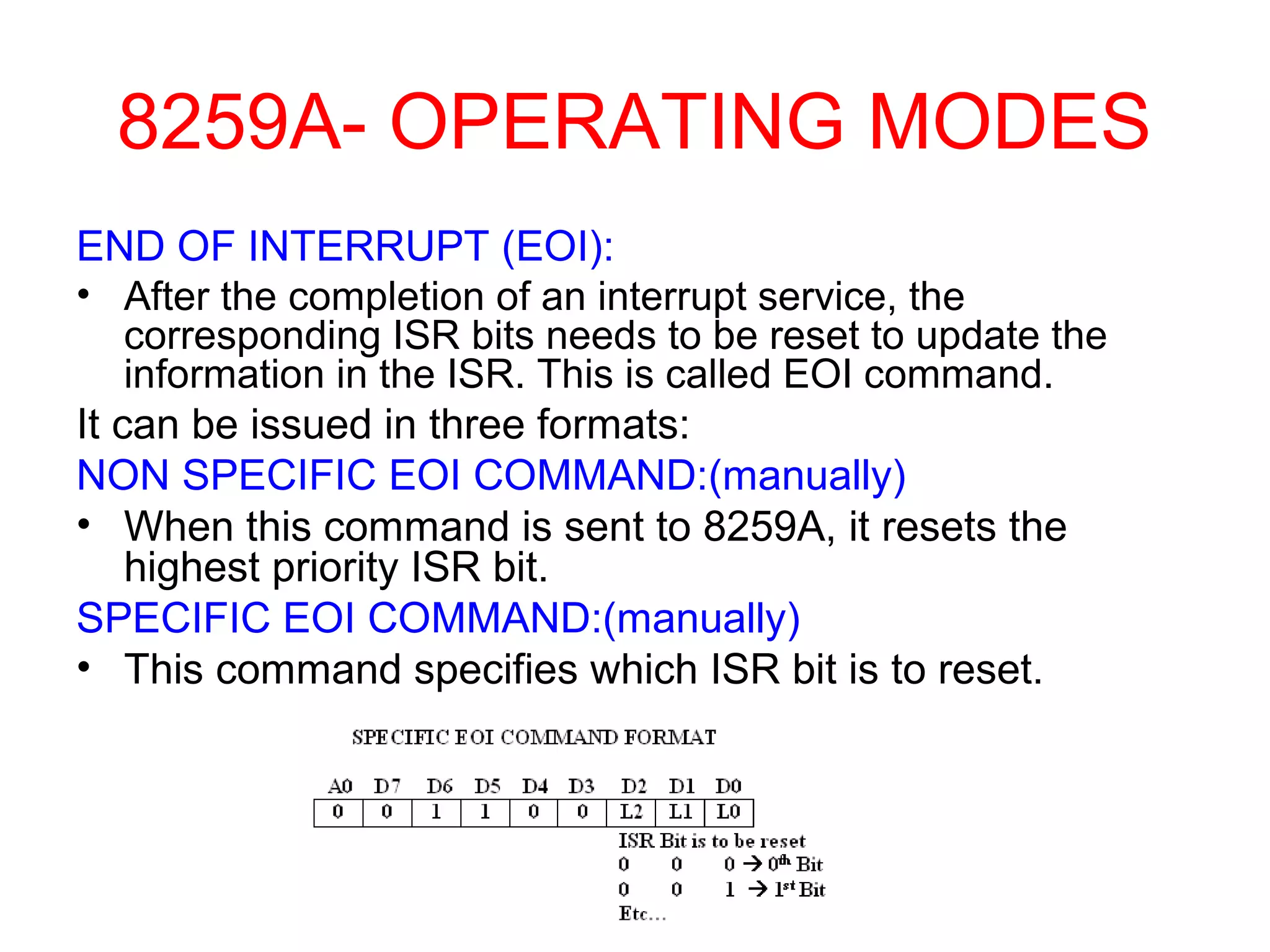

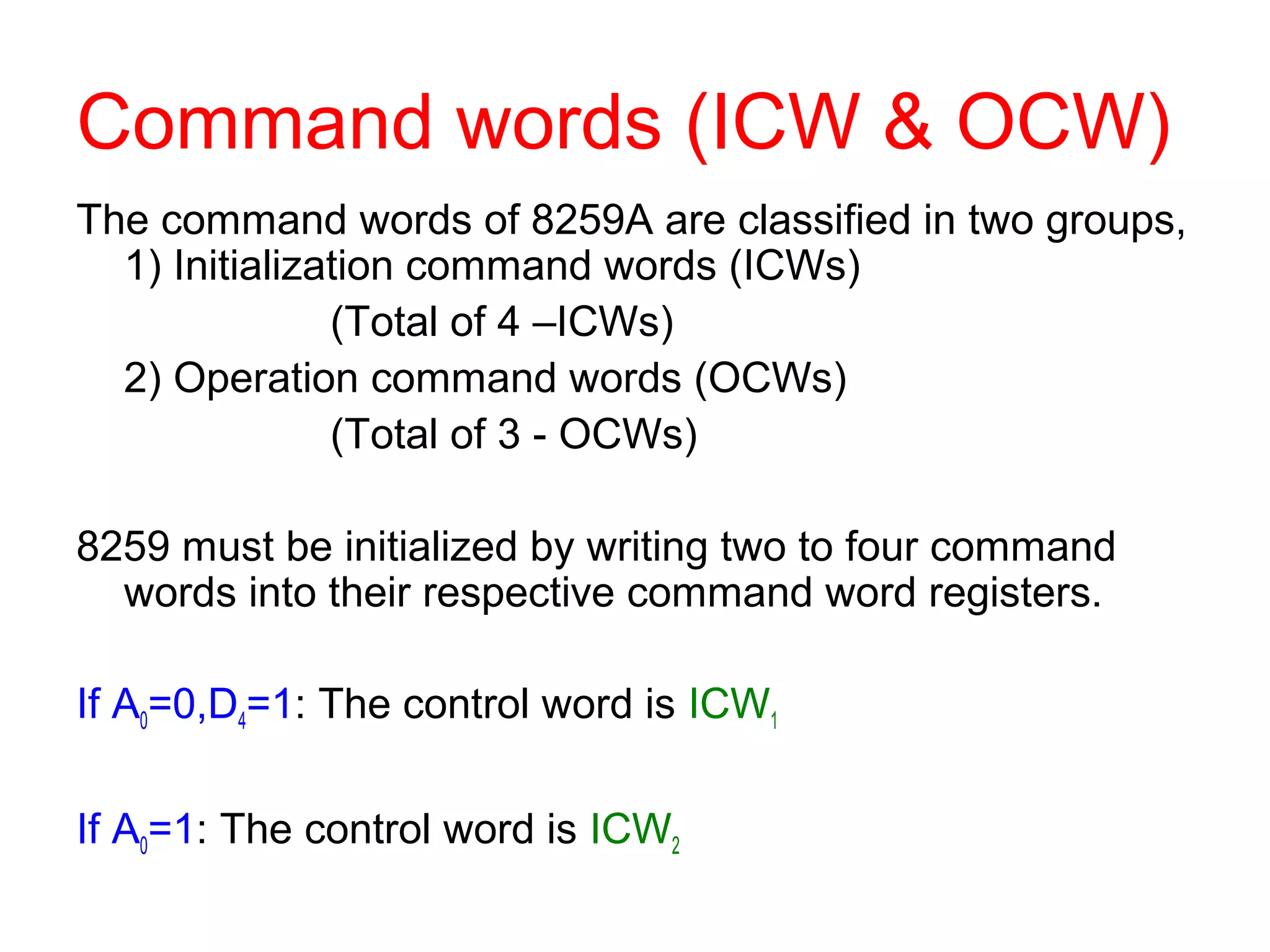

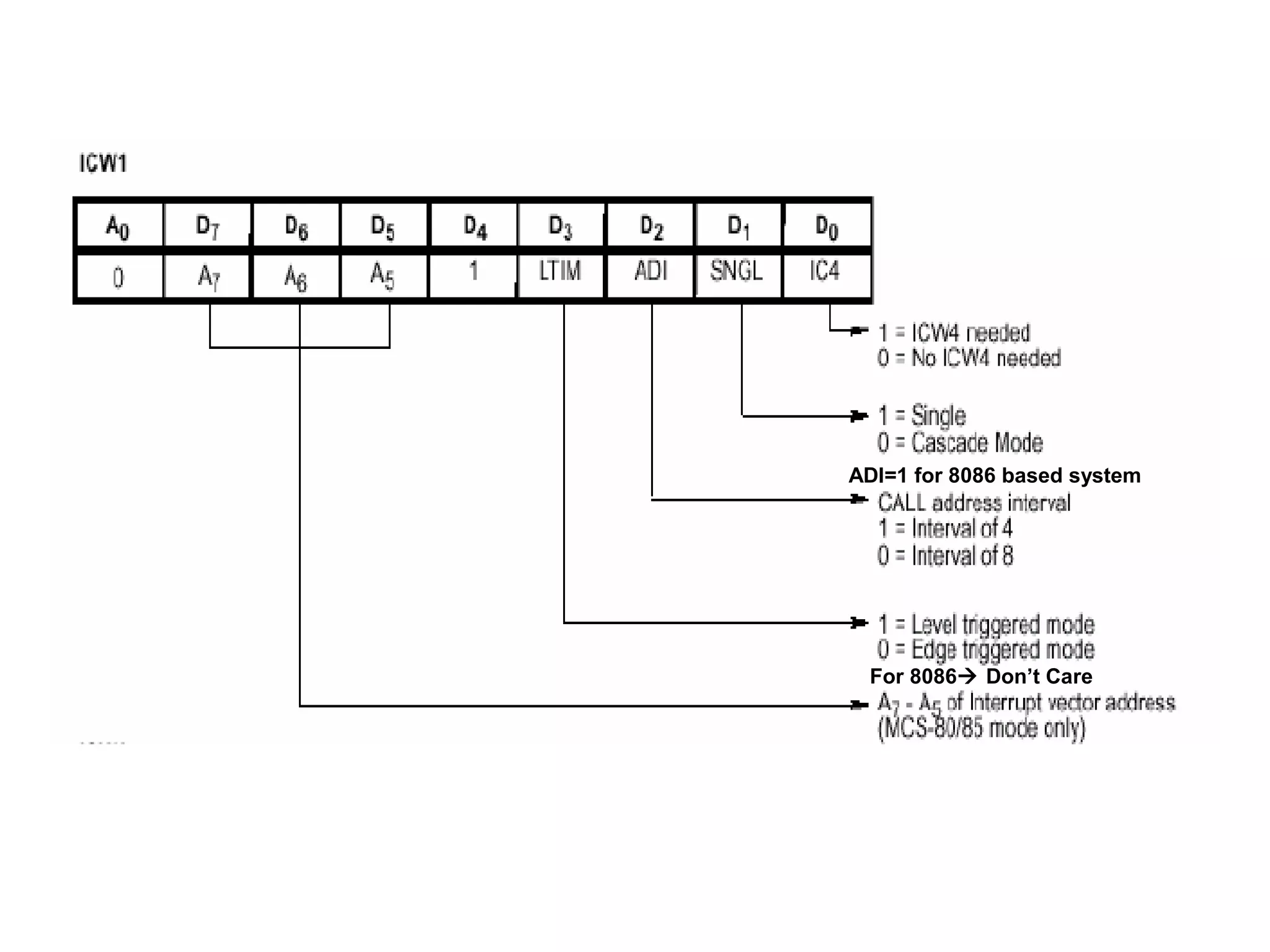

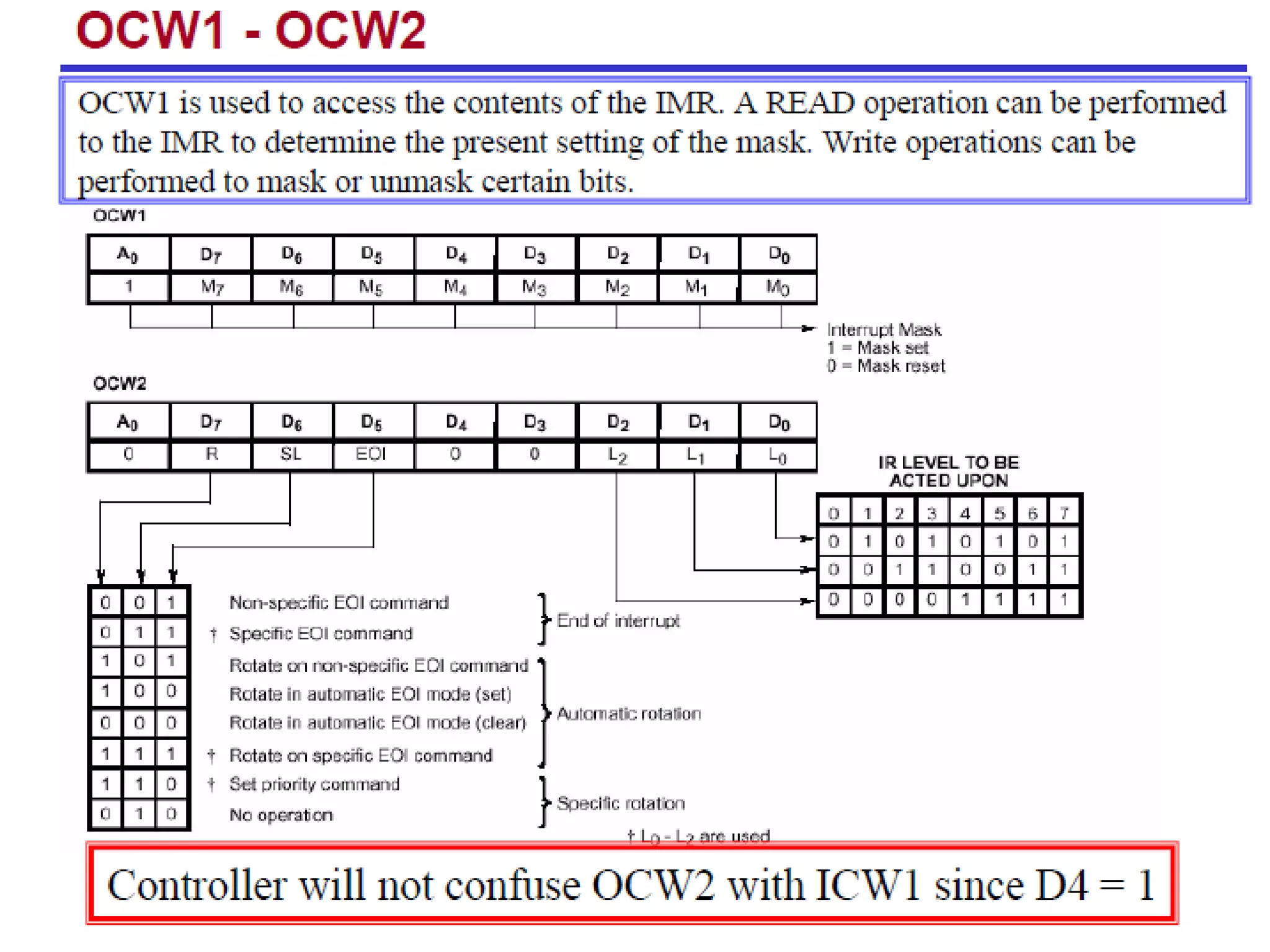

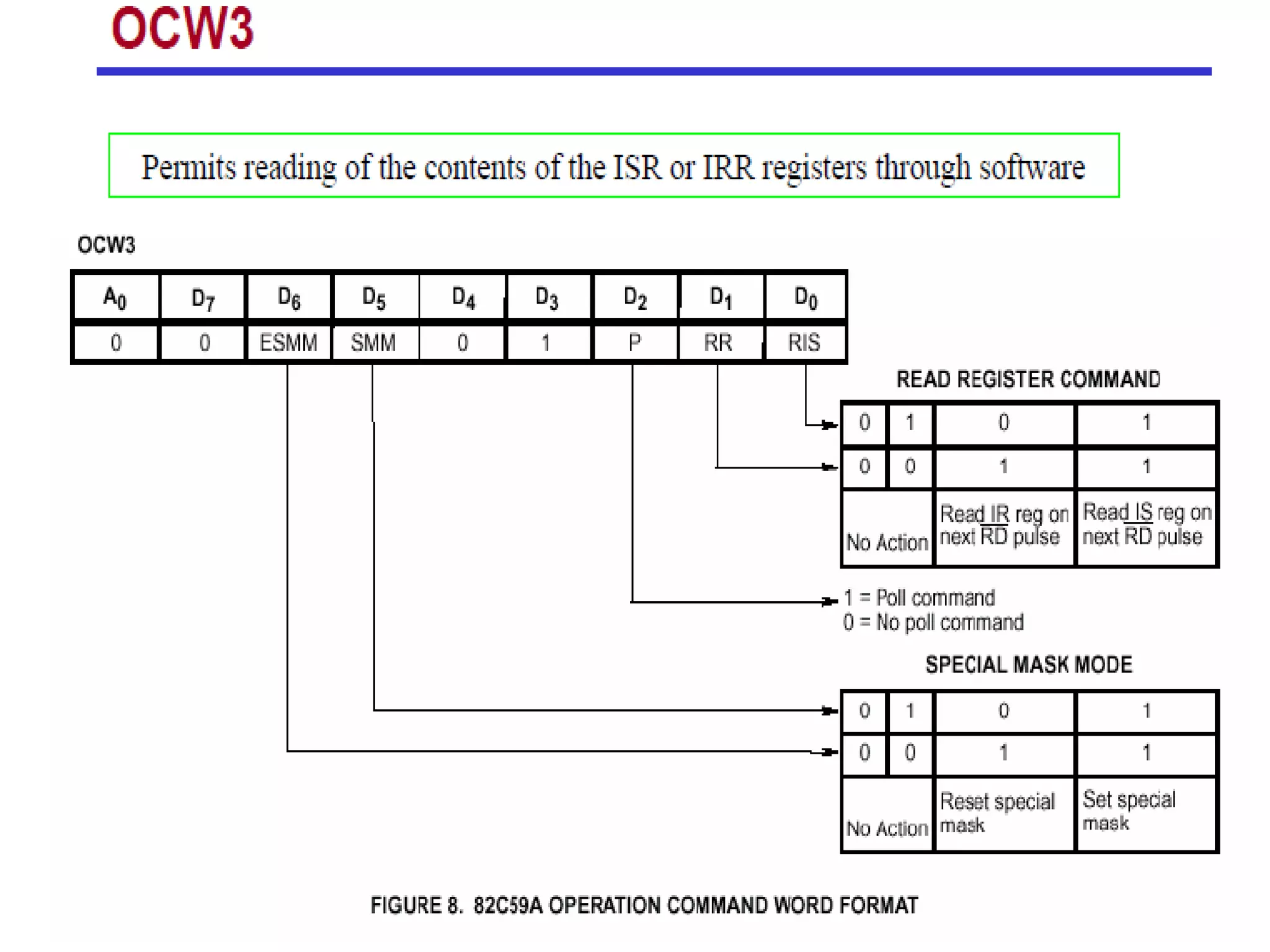

The 8259A Programmable Interrupt Controller (PIC) handles interrupts from I/O devices for processors that have limited hardware interrupt pins. It supports up to 8 interrupt requests with configurable priority levels that can be expanded to 64 levels by cascading additional 8259A chips. The PIC consists of registers and logic to accept interrupt requests, determine priority, notify the processor, and provide the interrupt vector address. It is initialized via initialization command words and controlled via operation command words to configure operating modes like fully nested, automatic rotation, and specific rotation priority schemes.