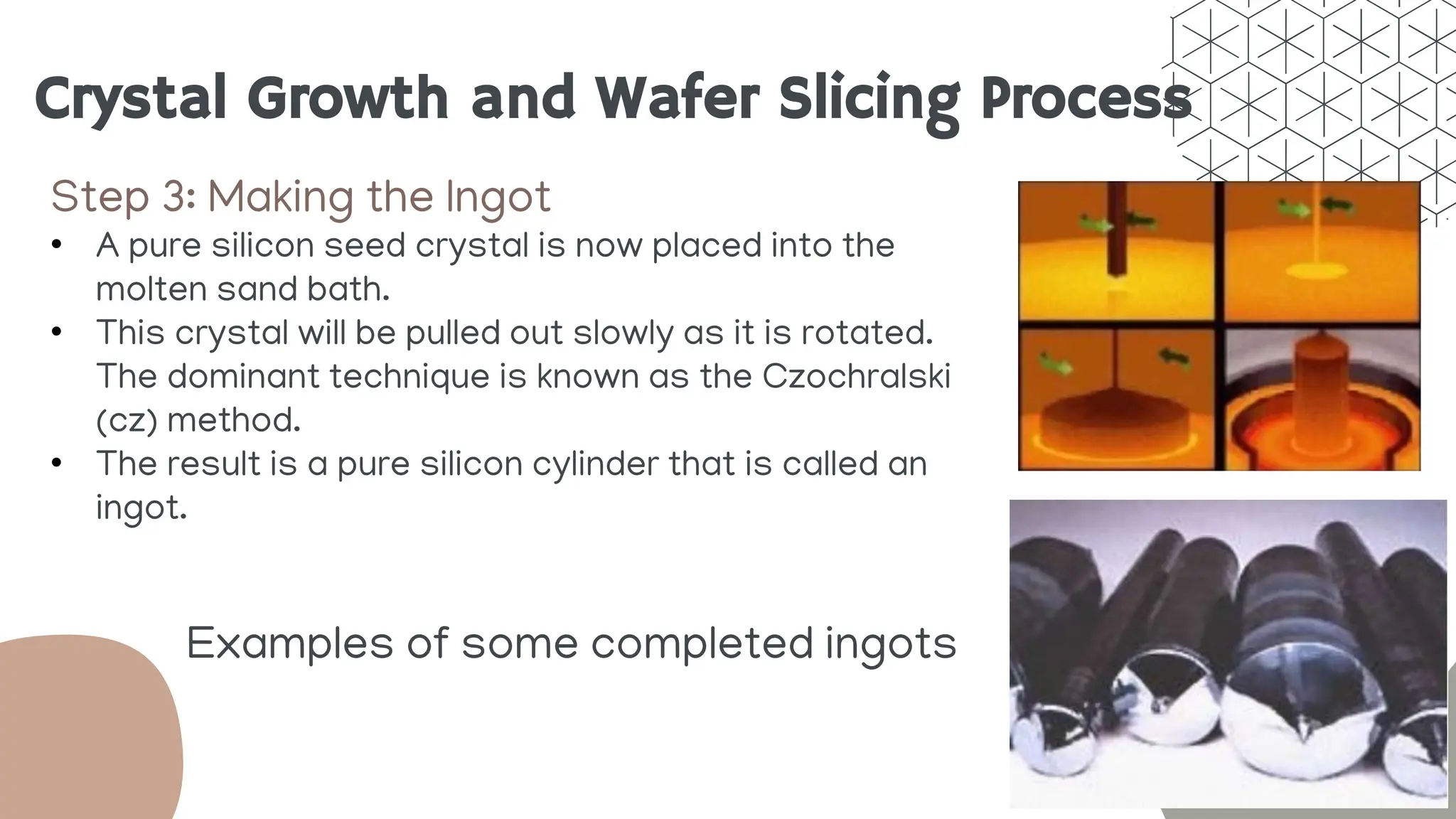

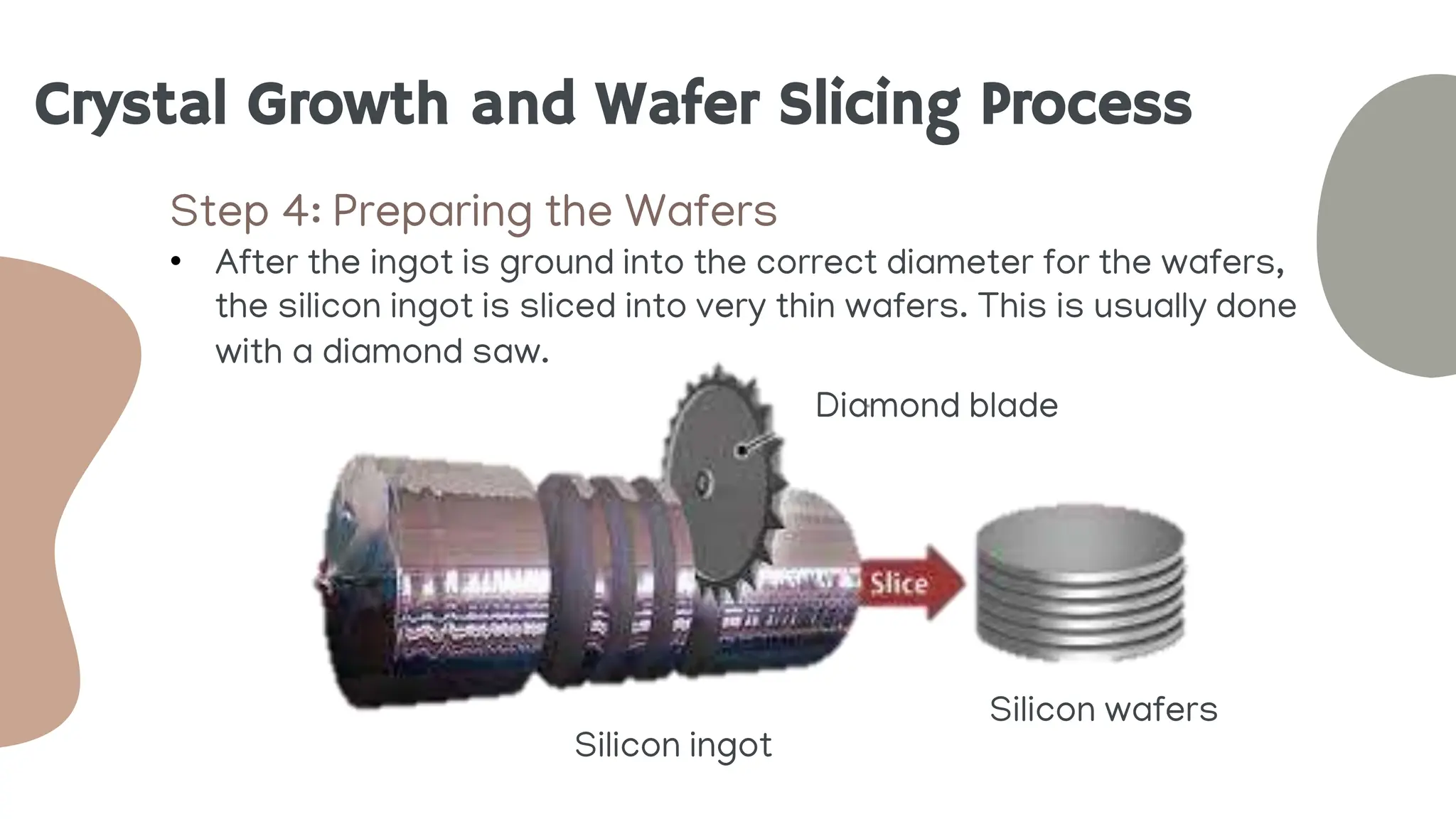

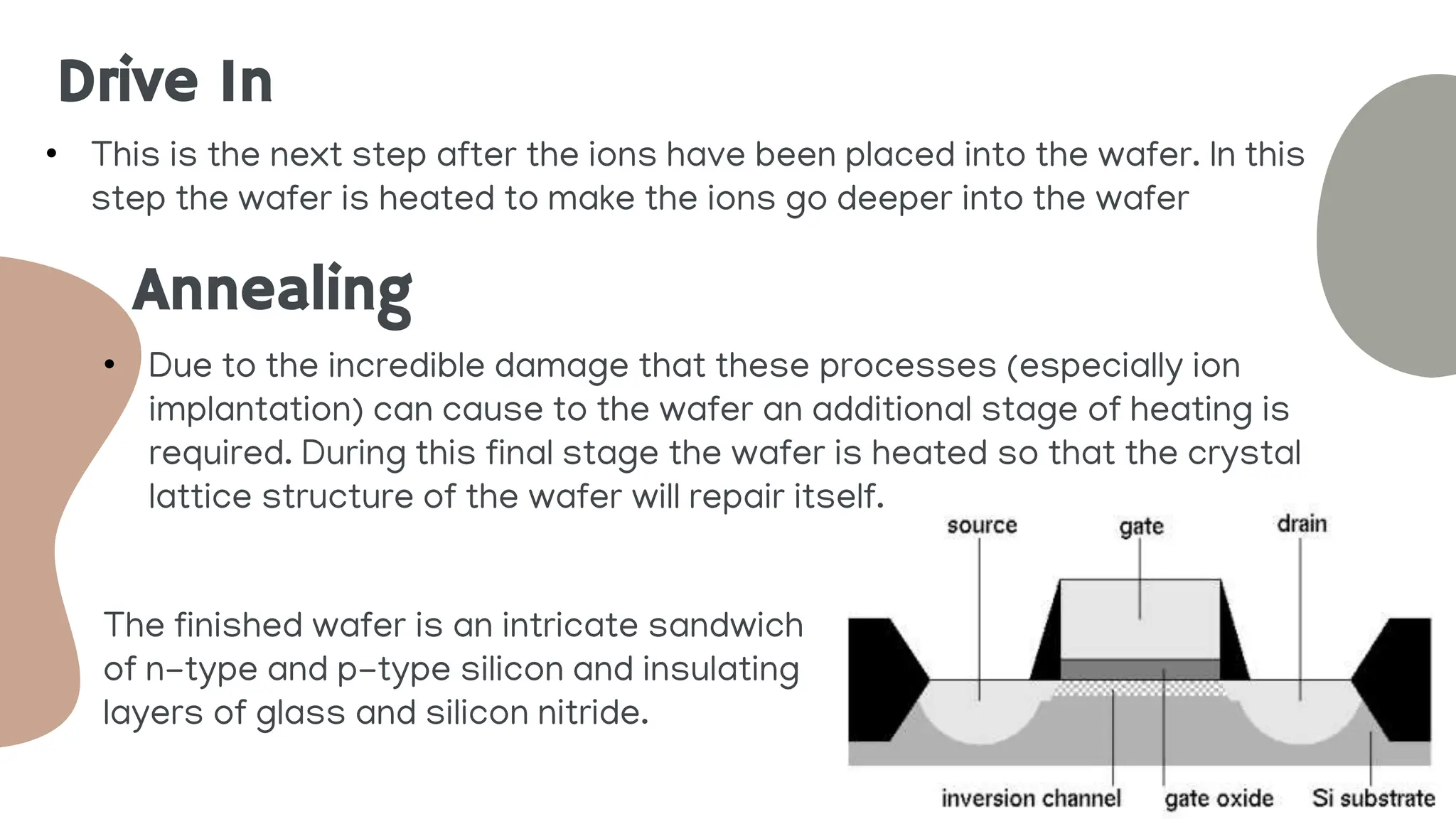

The document summarizes the key steps to prepare and process a silicon wafer for semiconductor memory chips. It involves obtaining pure silicon through crystallization and slicing it into wafers. The wafers are then polished, coated with insulating glass and nitride layers, and patterned using photolithography. Etching, diffusion, and ion implantation are used to introduce dopants according to the pattern. The wafers undergo annealing and various packaging and testing steps to produce finished memory chips. The entire process takes place in cleanrooms to prevent particle contamination.