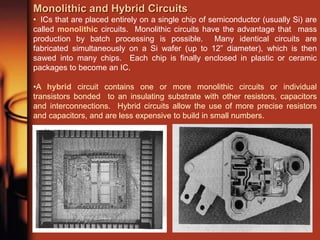

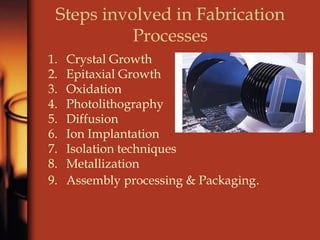

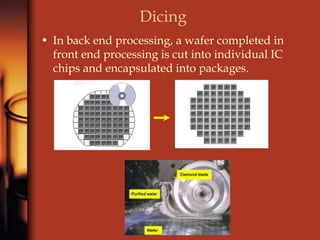

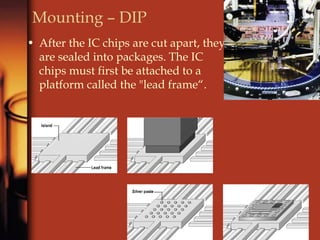

Integrated circuits have increased dramatically in complexity over time due to advances in fabrication technology allowing for higher densities of components on silicon chips. The fabrication process involves growing high purity silicon crystals, depositing layers, doping for conductivity, patterning circuits using photolithography, and packaging individual dies. Advances like shrinking transistor sizes and cleaner room environments have allowed integration to scale while maintaining reliability.