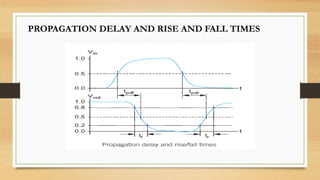

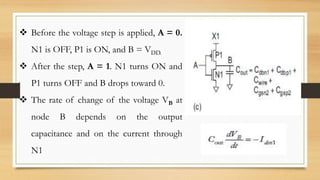

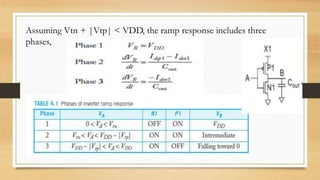

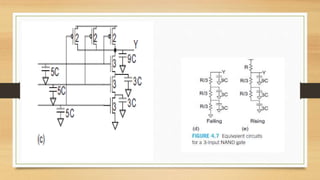

The document discusses propagation delay, rise/fall times, and transient response in digital circuits. It defines key timing parameters and describes how to model digital gates and wires as resistor-capacitor circuits to estimate delays. The RC model approximates transistor behavior with average resistance and capacitance values. Delay is calculated using techniques like Elmore delay, which sums the resistive and capacitive contributions of each node in the circuit. Examples show how to apply these techniques to calculate delays for common circuit structures.