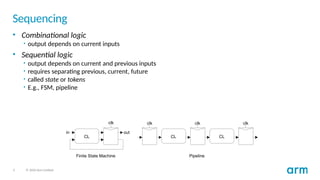

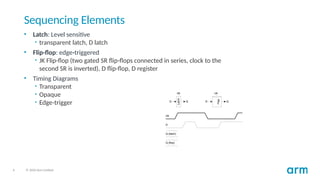

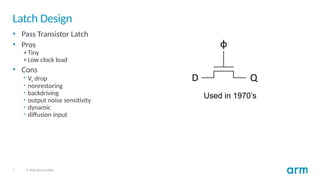

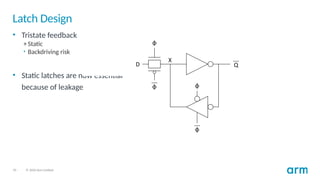

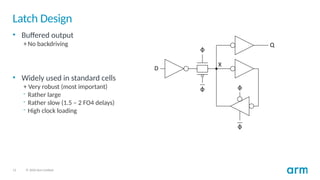

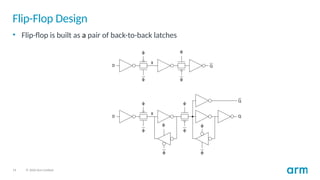

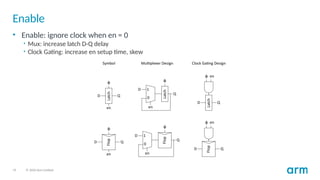

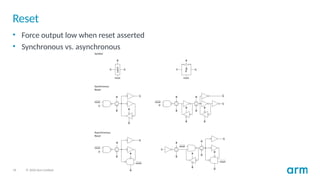

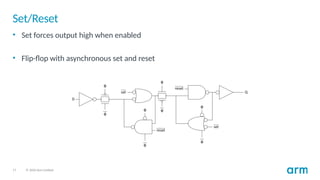

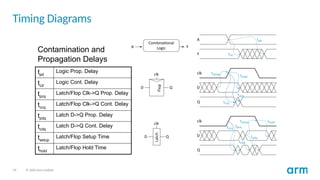

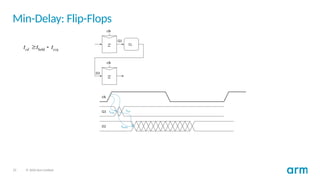

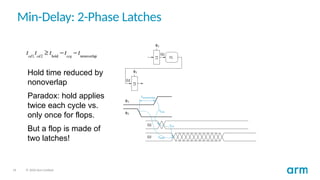

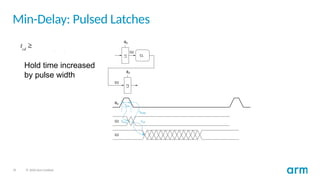

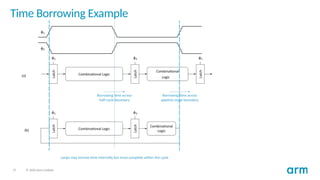

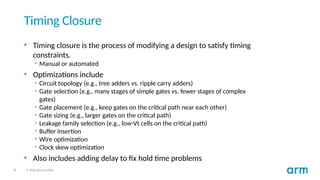

The lecture on sequential circuit design covers input and output timing constraints, including setup and hold times, as well as propagation and contamination delays. It discusses various sequencing elements like latches and flip-flops, their designs, and the importance of timing analysis in ensuring circuit functionality. Additionally, it highlights timing closure processes to meet design specifications and introduces concepts like time borrowing and clock skew.