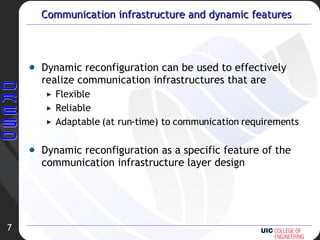

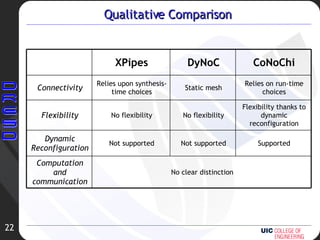

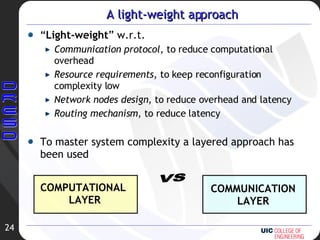

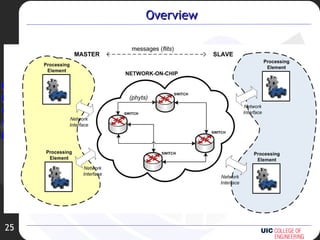

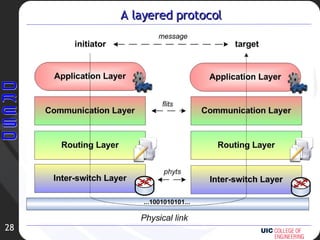

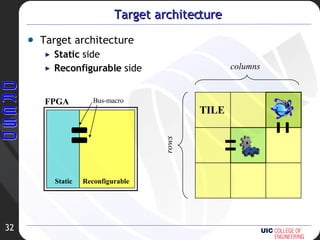

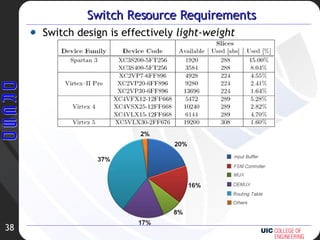

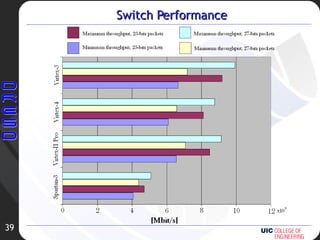

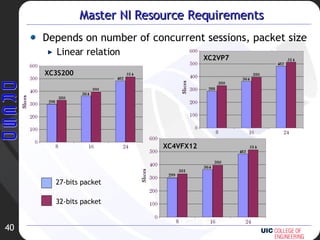

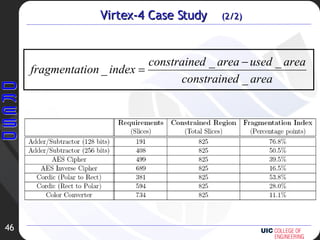

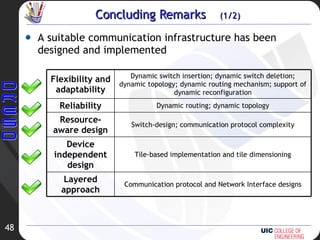

The document summarizes a thesis that defines a communication infrastructure for partially reconfigurable architectures. The proposed infrastructure uses a network-based approach with network nodes tailored for partial reconfiguration. It aims to provide a flexible, reliable and adaptable communication schema. The thesis outlines related works on communication infrastructures for FPGAs, presents the proposed layered network approach and implementation, experimental results comparing it to previous works, and conclusions.

![A Flexible Tile-Based Communication Infrastructure for Partial Reconfigurable Architectures BY Simone Corbetta [email_address] Thesis committee: Shantanu Dutt (chair), Donatella Sciuto, Ashfaq Ahmad Khokhar UIC Thesis Defense: May, 8th 2008](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/75/UIC-Thesis-Corbetta-1-2048.jpg)

![Aims [A1] Define a communication infrastructure for partially reconfigurable architectures [A2] Design the communication protocol [A3] Design network nodes [A4] Implementation](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-2-320.jpg)

![Communication-centric design Increasing complexity in modern Systems-on-Chips Increasing applications scenarios Communication requirements increase Communication-centric design [1,2] Static versus dynamic environment Executing applications are not known a priori Communication requirements cannot be specified prior to system execution “ Classical” widely-used communication approaches lack of flexibility and scalability Need to define a flexible, adaptable solution [1] “ Communication Centric SoC Design for Nanoscale Domain ”. Ogras, U. Y.; Jingcao, Hu; Marculescu, R. 16th IEEE International Conference on Application-Specific Systems, Architecture and Processors. July 2005. pp.73-78. [2] “ On-Chip Networks: a Scalable, Communication-Centric Embedded System Design Paradigm ”. Henkel, J.; Wolf, W.; Chakradhar, S. Proceedings of the 17th International Conference on VLSI Design, 2004. pp.845.851.](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-6-320.jpg)

![Network-on-Chip Borrow main ideas from data-network (LANs, WANs) Based on distributed communication nodes ( switches ) [3,4] [3] “ Networks-on-Chip: a New SoC Paradigm ”. De Micheli, G.; Benini, L. Computer. 2002, Volume 35. pp.70-78. [4] “ Networks-on-Chip: a New Paradigm for System-on-Chip Design ”. Nurmi, J. Proceedings of the International Symposium on System-on-Chip, Nov. 2005. pp.2-6. Computational overhead; high resource requirements Flexibility; scalability; reusability; reliability, no single point-of-failure Drawbacks Advantages](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-11-320.jpg)

![Field Programmable Gate Arrays Programmable logic devices (Re)programmable logic blocks and interconnects Configuration is stored within the configuration memory architecture Image taken from “ Bebop to the Boolean Boogie: an Unconventional Guide to Electronics Fundamentals, Components and Processes ” by Clive Maxfield [Everyday Practical Electronics]](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-13-320.jpg)

![XPipes (1/2) Designed for multi-processors systems [5] Ad-hoc network topology defined at synthesis-time XPipesCompiler Based on a layered approach: Smart Stack protocol [5] Bertozzi, D.; Benini, L. “ XPipes: A Network-on-Chip Architecture for Gigascale Systems-on-Chip ”. Circuits and Systems Magazine , IEEE, 2004, 4, pp.18-31. DATA-LINK LAYER NETWORK LAYER TRANSPORT LAYER physical link](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-16-320.jpg)

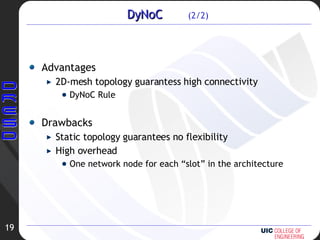

![DyNoC (1/2) Static NoC for heterogeneous systems [6] Static 2D-mesh interconnection topology Static routing mechanism (modified XY-Algorithm ) [6] Bobda, C.; Ahmadinia, A.; Majer, M.; Teich, J.; Fekete, S.; Van der Veen, J. “ DyNoC: A Dynamic Infrastructure for Communicationin Dynamically Reconfigurable Devices ”. International Conference on Field Programmable Logic and Applications , August 2005, pp.151-158. DyNoC Rule](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-18-320.jpg)

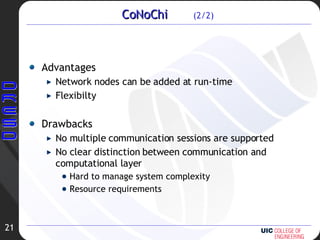

![CoNoChi (1/2) Reconfigurable packet-switched communication architecture [7] [7] Pionteck, T.; Koch, R.; Albrecth, C. “ Applying Partial Reconfiguration to Networks-on-Chips ”. International Conference on Field Programmable Logic and Applications , August 2006, pp.1-6.](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-20-320.jpg)

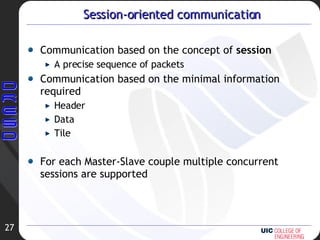

![Packet-switched communication Packet-switching instead of circuit-switching [8] General packet structure [8] Dally, W.; Towles, B. “Route packets, not wires: on-chip interconnection networks” . In proceedings of the Design and Automation Conference in Europe, 2001, pp.684-689. Contains communication-related information (route update, communication tail, replies…) Control Contains data of the current communication request Data Contains preliminary information on the current communication session, useful for the recipient Header](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-26-320.jpg)

![Webpage www.dresd.org/?q=CITiES Mailing List [email_address] Contact To have more information regarding the CITiES Project: [email_address] For a complete list of information on how to contact us: www.dresd.org/?q=contact_cities General Information](https://image.slidesharecdn.com/uiccorbettathesis-1211290127761418-9/85/UIC-Thesis-Corbetta-50-320.jpg)