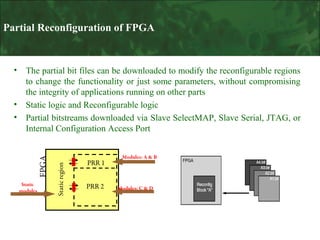

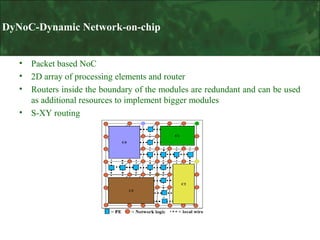

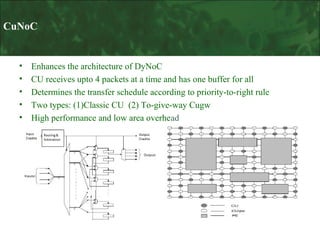

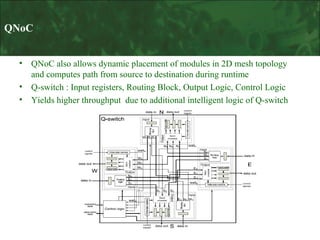

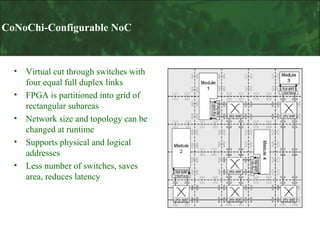

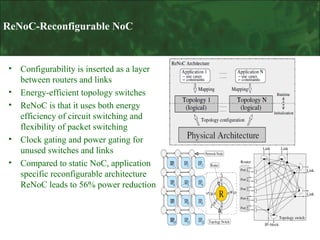

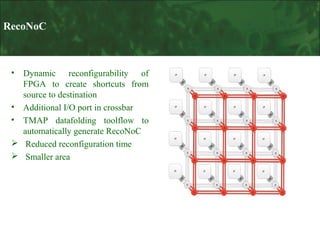

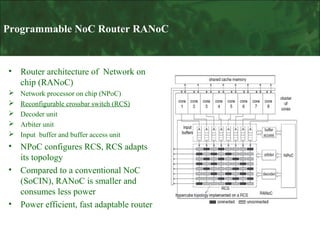

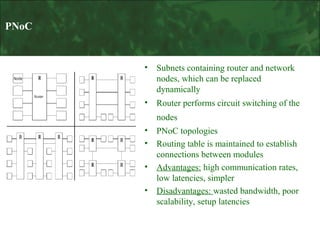

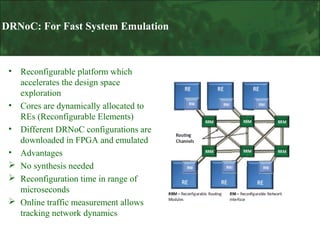

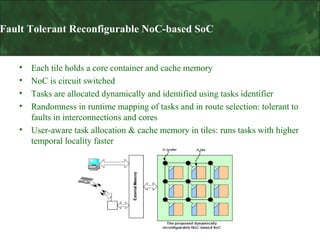

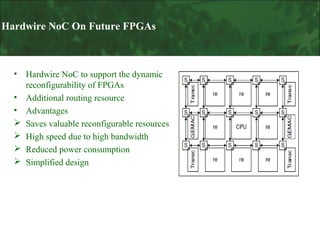

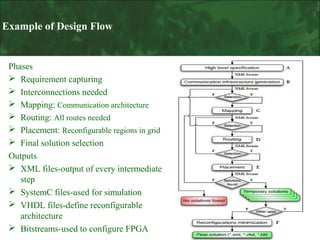

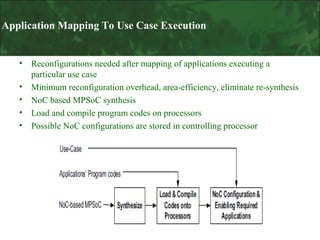

This document discusses runtime reconfigurable network-on-chips (NoCs) for field programmable gate arrays (FPGAs). It describes several NoC architectures that support dynamic exchange of hardware modules through partial reconfiguration of FPGAs, including DyNoC, CuNoC, QNoC, CoNoChi, ReNoC, and RecoNoC. It also discusses the design factors, quantitative metrics, and applications of runtime reconfigurable NoCs, and concludes that these NoCs provide interconnect frameworks with reconfiguration capabilities, flexibility, and performance to integrate multiple applications on a single FPGA.