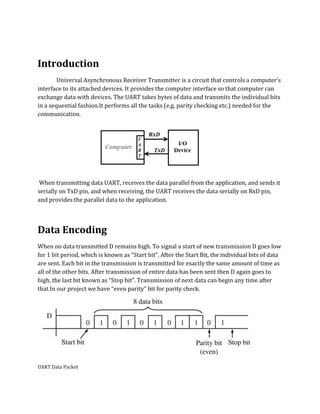

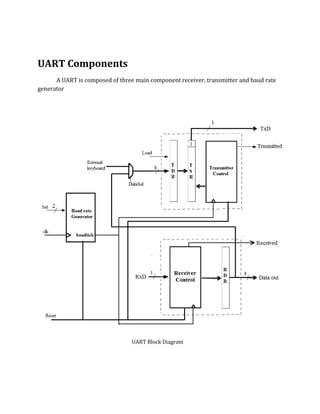

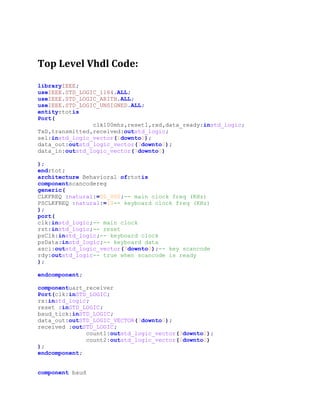

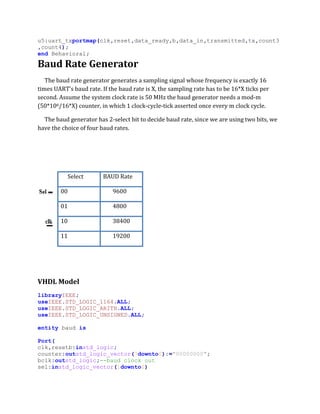

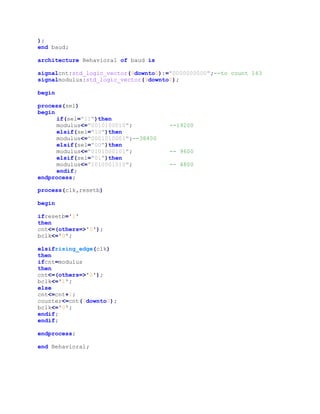

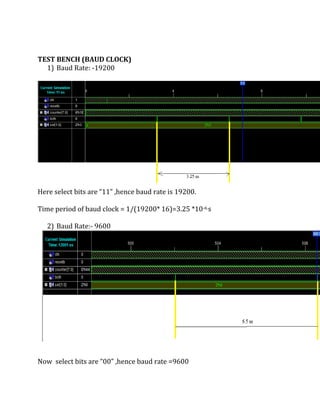

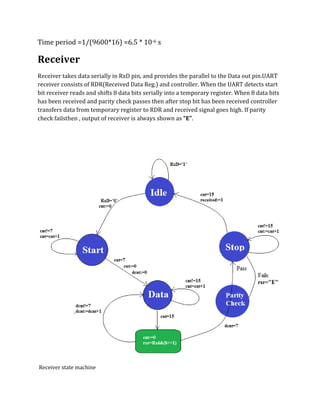

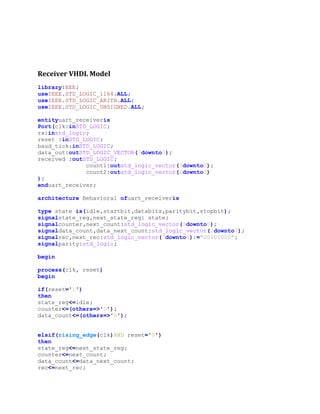

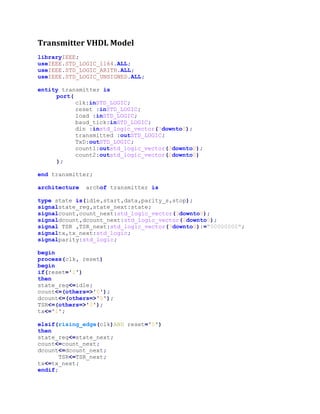

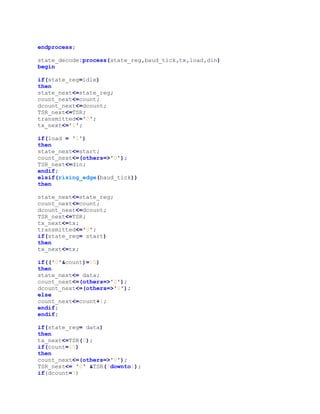

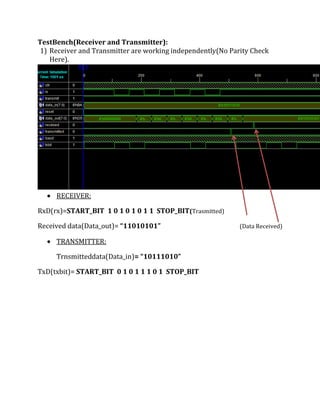

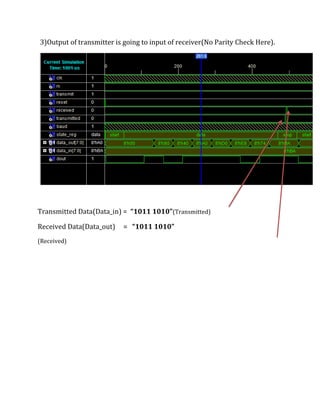

The document describes a Universal Asynchronous Receiver Transmitter (UART) circuit. A UART allows a computer to communicate with external devices by transmitting serial data. It contains a receiver that takes in serial data and a transmitter that sends out serial data. A baud rate generator is used to synchronize the transmission and reception of bits. The document provides details on the UART components, data encoding, and includes VHDL code for a UART design.