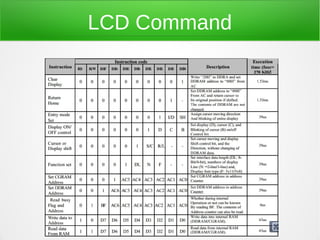

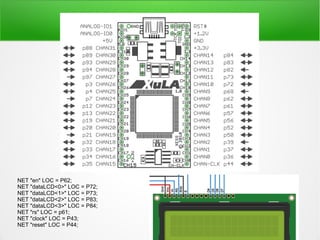

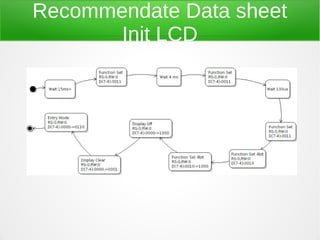

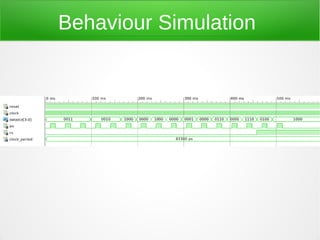

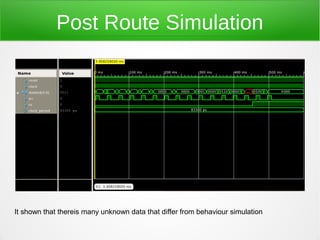

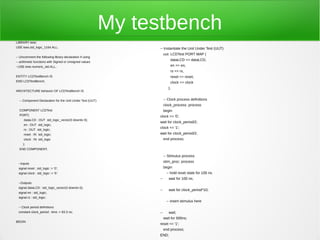

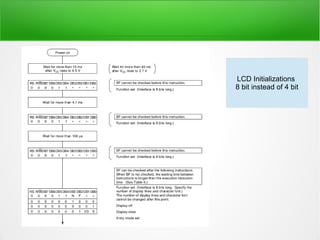

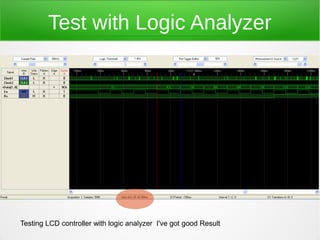

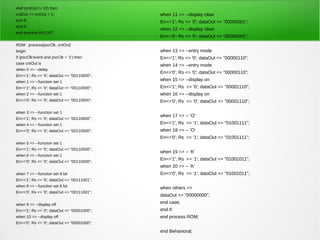

The document describes interfacing an FPGA to an LCD 16x2 display. It includes a block diagram, pin descriptions, timing diagrams, LCD initialization procedures from the datasheet, and VHDL code to implement the LCD controller on the FPGA. The VHDL code uses a state machine and ROM-based model with an 8-bit data line to generate the LCD initialization sequence and display text on the LCD. Behavioral and post-route simulations are shown to verify the design works as intended.