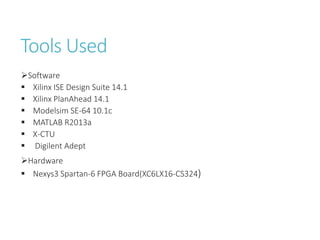

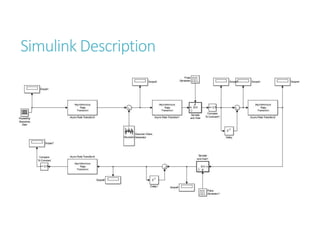

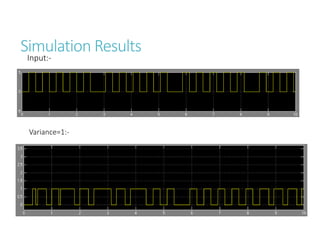

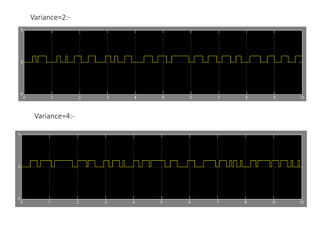

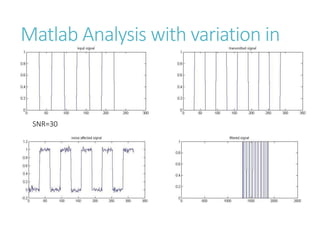

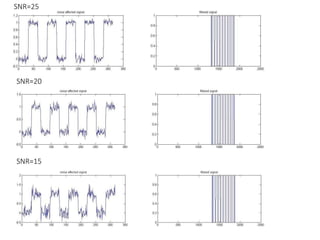

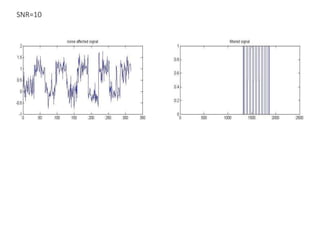

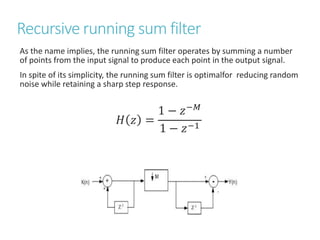

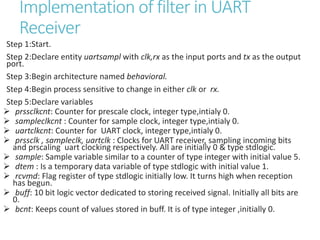

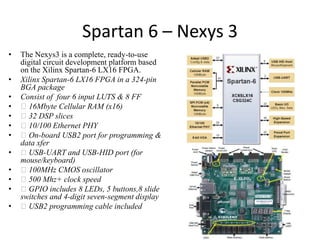

This document describes a project to design a robust UART architecture using a recursive running sum filter for better noise performance. It discusses adding noise to communication channels to test noise performance. It then describes implementing a UART receiver using a recursive running sum filter to reduce noise while maintaining signal integrity. The UART design is tested on a Nexys3 Spartan-6 FPGA board in Xilinx ISE using VHDL. Simulation results at different noise levels show the filter is effective at reducing noise.