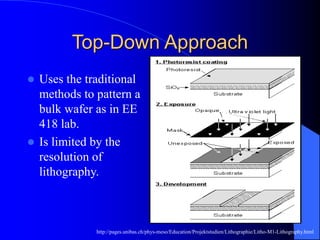

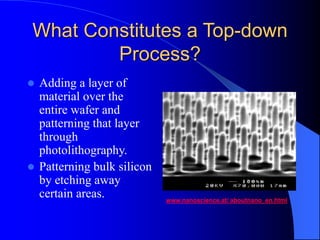

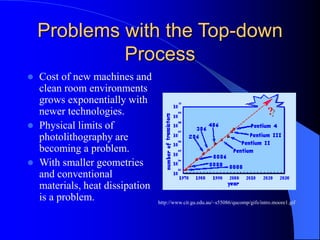

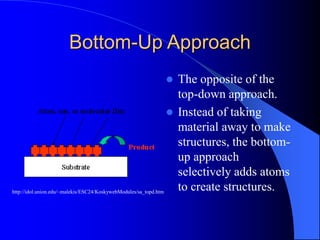

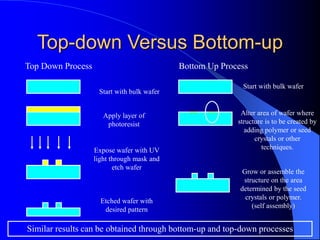

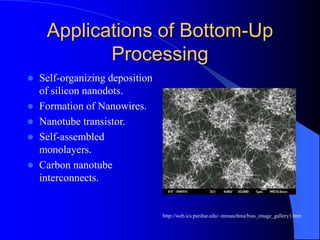

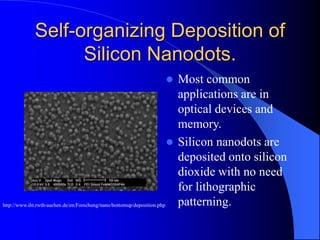

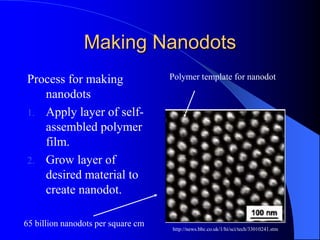

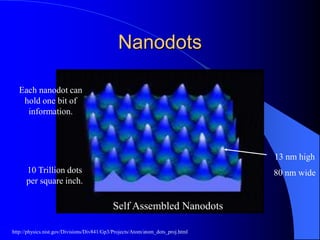

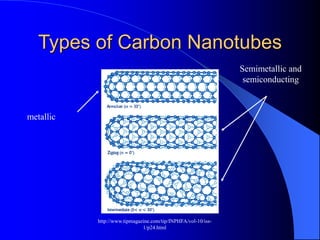

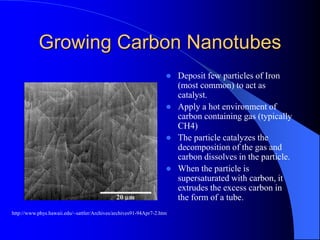

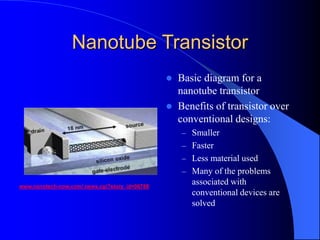

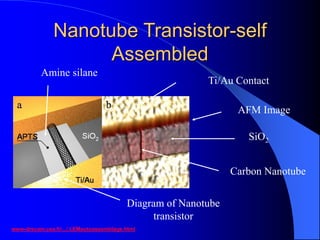

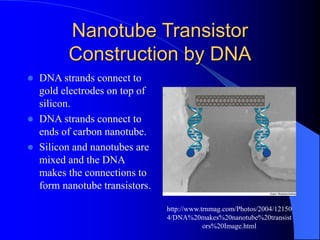

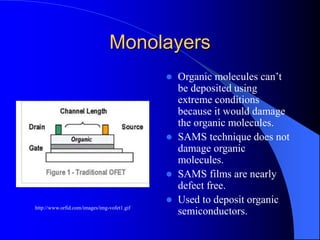

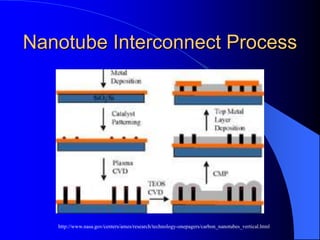

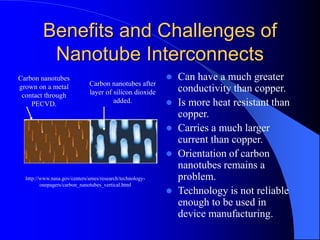

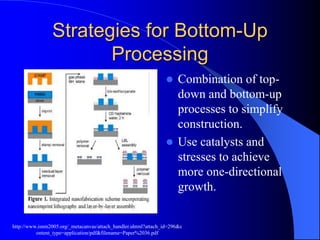

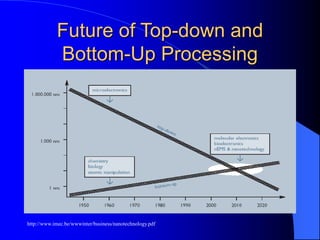

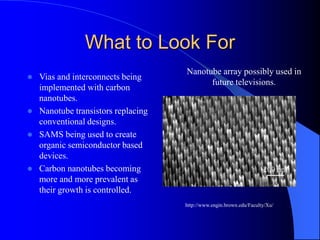

The document discusses top-down and bottom-up processes for manufacturing structures at the nanoscale. Top-down processes start with bulk material and use techniques like lithography and etching to pattern structures, while bottom-up processes build structures from the atomic or molecular scale using self-assembly. Both approaches are needed as bottom-up is required to make smaller structures than lithography allows, and applications include growing carbon nanotubes, nanodots, and using self-assembled monolayers. Challenges of bottom-up include controlling assembly, but the future will see more integration of both top-down and bottom-up nanomanufacturing.